Computer Architecture

Chapter 8

Multiprocessors

Shared Memory Architectures

Prof. Jerry Breecher

CSCI 240

Fall 2003

Chap. 8 - Multiprocessors 2

Chapter Overview

We’re going to do only one section from this chapter, that part related

to how caches from multiple processors interact with each other.

8.1 Introduction – the big picture

8.3 Centralized Shared Memory Architectures

Chap. 8 - Multiprocessors 3

Introduction

8.1 Introduction

8.3 Centralized Shared

Memory Architectures

The Big Picture: Where are

We Now?

The major issue is this:

We’ve taken copies of the contents of main

memory and put them in caches closer to the

processors. But what happens to those

copies if someone else wants to use the main

memory data?

How do we keep all copies of the data in synch

with each other?

Chap. 8 - Multiprocessors 4

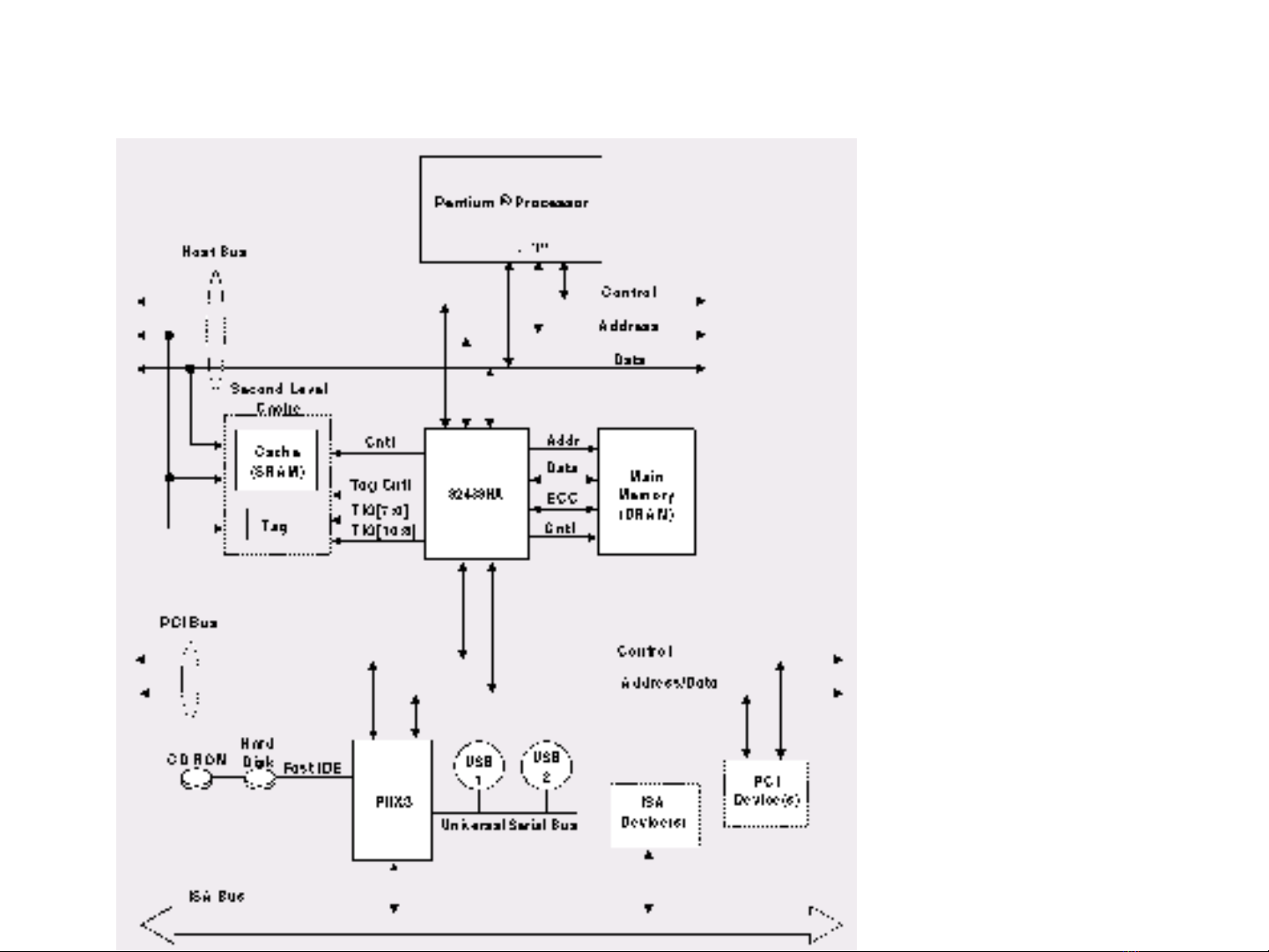

The Multiprocessor Picture

Processor/Memory

Bus

PCI Bus

I/O Busses

Example:

Pentium System

Organization

Chap. 8 - Multiprocessors 5

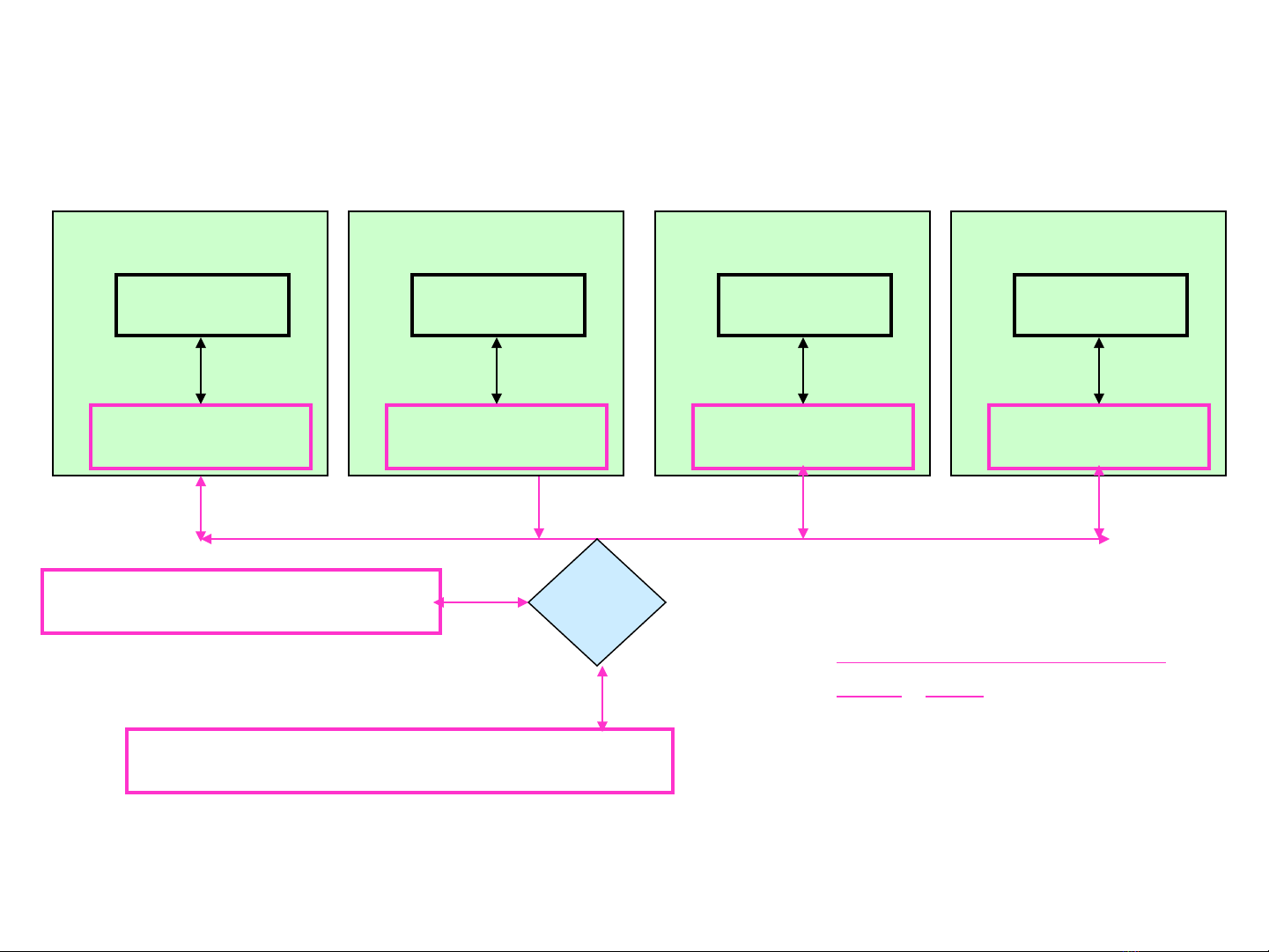

Memory

Disk & other IO

Shared Memory Multiprocessor

Registers

Caches

Processor

Registers

Caches

Processor

Registers

Caches

Processor

Registers

Caches

Processor

Chipset •Memory: centralized with

Uniform Memory Access

time (“uma”) and bus

interconnect, I/O

•Examples: Sun Enterprise

6000, SGI Challenge, Intel

SystemPro

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)

![Giáo trình Sửa chữa máy in và thiết bị ngoại vi - Trường Cao đẳng Cơ điện Hà Nội [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251231/gaupanda090/135x160/47191775188546.jpg)