Kiểm tra cuối HK – Kiến trúc Máy tính – CS2009 Trang 1/2

Trường ĐH Bách Khoa TP.HCM

Khoa KH & KT Máy tính

ĐỀ THI CUỐI HỌC KỲ I – 2009-2010

Môn Kiến trúc Máy tính (CSE504002)

Thời gian: 90 phút

(Được tham khảo tài liệu, không được sử dụng máy tính laptop)

Bài 1: (2 điểm) Một nhóm kỹ sư đang thiết kế một bộ xử lý đơn giản. Họ phải chọn lựa giữa

cách hiện thực theo kiểu pipeline và không pipeline. Các thông số thiết kế cho 2 cách hiện thực

này được thể hiện trong bảng sau:

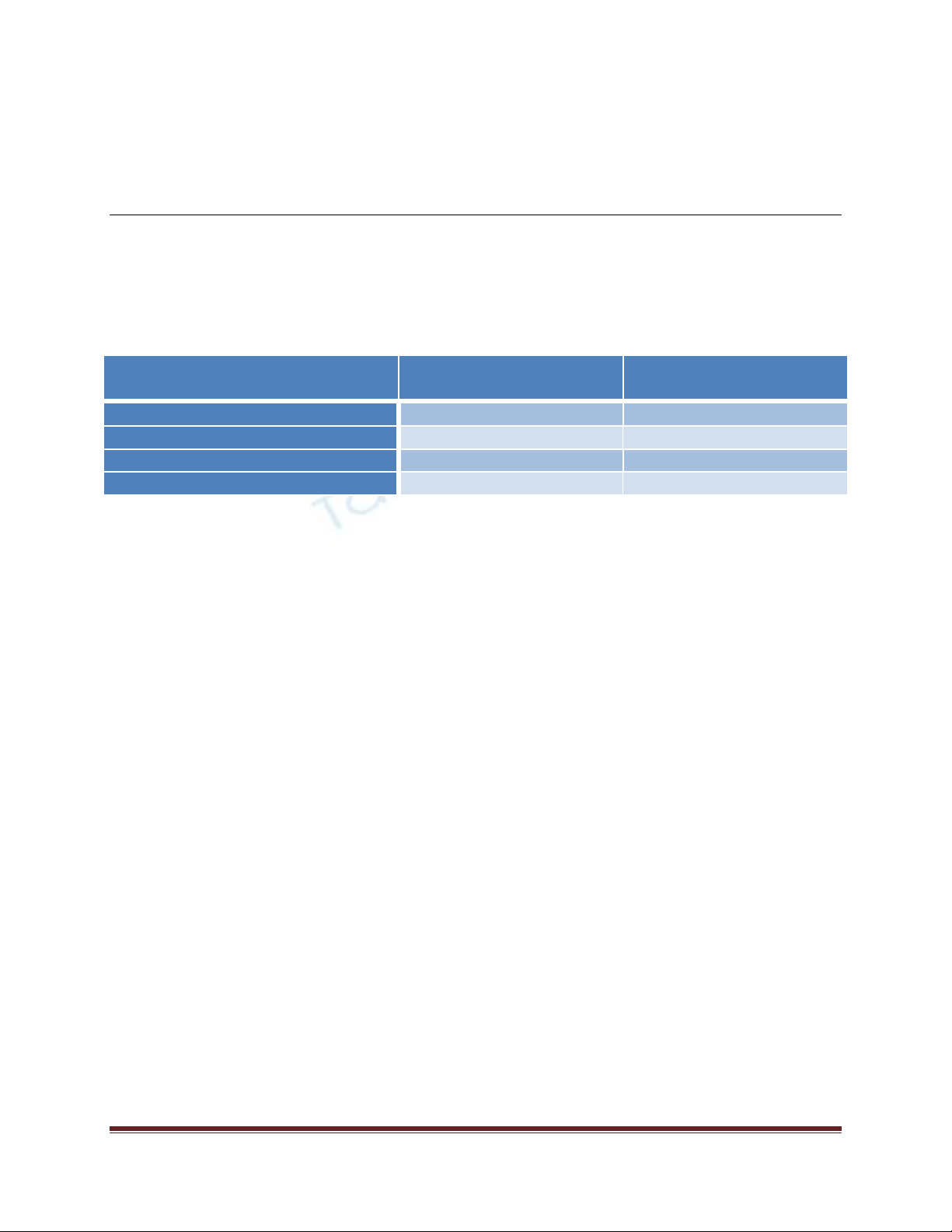

Thông số thiết kế

Cách hiện thực

pipeline

Cách hiện thực

không pipeline

Tốc độ xung clock

600MHz

450MHz

CPI cho các lệnh truy xuất bộ nhớ

2.5

1.2

CPI cho các lệnh số học/luận lý

1

1

CPI cho các lệnh điều khiển

2

1

a. Cho một chương trình bao gồm 20% các lệnh số học/luận lý, 10% các lệnh điều khiển và

70% các lệnh truy xuất bộ nhớ. Xác định CPI trung bình cho mỗi cách hiện thực. Cách

thiết kế nào hiệu quả hơn?

Average CPI for Pipelined Version = (0.2*1 + 0.1*2 + 0.7*2.5) = 2.15

Average CPI for Non-Pipelined Version = (0.2*1 + 0.1*1 + 0.7*1.2) = 1.14

CPU execution time for Pipelined version = 2.15/(600 Mhz) = 3.58ns

CPU execution time for Non-Pipelined version = 1.14/(450 Mhz) = 2.53ns

Cách hiện thực không pipeline nhanh hơn.

b. Cho một chương trình bao gồm 75% các lệnh số học/luận lý, 15% các lệnh điều khiển và

10% các lệnh truy xuất bộ nhớ. Xác định CPI trung bình cho mỗi cách hiện thực. Cách

thiết kế nào hiệu quả hơn?

Average CPI for Pipelined Version = (0.75*1 + 0.15*2 + 0.1*2.5) = 1.3

Average CPI for Non-Pipelined Version = (0.75*1 + 0.15*1 + 0.1*1.2) = 1.02

CPU execution time for Pipelined version = 1.3/(600 Mhz) = 2.16ns

CPU execution time for Non-Pipelined version = 1.02/(450 Mhz) = 2.26ns

Cách hiện thực pipeline nhanh hơn.

Kiểm tra cuối HK – Kiến trúc Máy tính – CS2009 Trang 2/2

Bài 2: (2.5 điểm) Dùng hợp ngữ MIPS viết phiên bản hợp ngữ cho đoạn chương trình C sau đây:

int A[100], B[100];

for (i=1; i < 100; i++) {

A[i] = A[i-1] + B[i];

}

Giả thiết rằng ban đầu chỉ có địa chỉ nền của mảng A và B được lưu trong thanh ghi $a0 và $a1.

Đáp án

li $t0, 1 # Starting index of i

li $t5, 100 # Loop bound

loop: lw $t1, 0($a1) # Load A[i-1]

lw $t2, 4($a2) # Load B[i]

add $t3, $t1, $t2 # A[i-1] + B[i]

sw $t3, 4($a1) # A[i] = A[i-1] + B[i]

addi $a1, 4 # Go to i+1

addi $a2, 4 # Go to i+1

addi $t0, 1 # Increment index variable

bne $t0, $t5, loop # Compare with Loop Bound

halt: nop

Kiểm tra cuối HK – Kiến trúc Máy tính – CS2009 Trang 3/2

Bài 3: (2 điểm) Cho một bộ xử lý có bộ nhớ vật lý 16KB, đánh địa chỉ theo từng byte và một

cache có kích thước mỗi dòng là 8 byte.

a. Giả sử cache dùng phương thức ánh xạ trực tiếp với trường tag trong địa chỉ là 7 bit.

Trình bày khung dạng địa chỉ bộ nhớ và xác định các thông số sau: số khối trong bộ nhớ

chính và số dòng trong cache

Số đơn vị có khả năng định vị địa chỉ là byte

Bộ nhớ có 16KB = 214 dùng địa chỉ 14 bit để xác định byte.

Một khối trong bộ nhớ chính bằng một dòng trong cache (8 byte = 23) nên bộ nhớ

chính có 214/23 = 211 khối

Một dòng trong cache có 8 byte nên cần 3 bit cho phần byte offset, phần tag là 7 bit

số bit để xác định dòng 14-7-3=4 => số dòng trong cache 24 = 16 dòng.

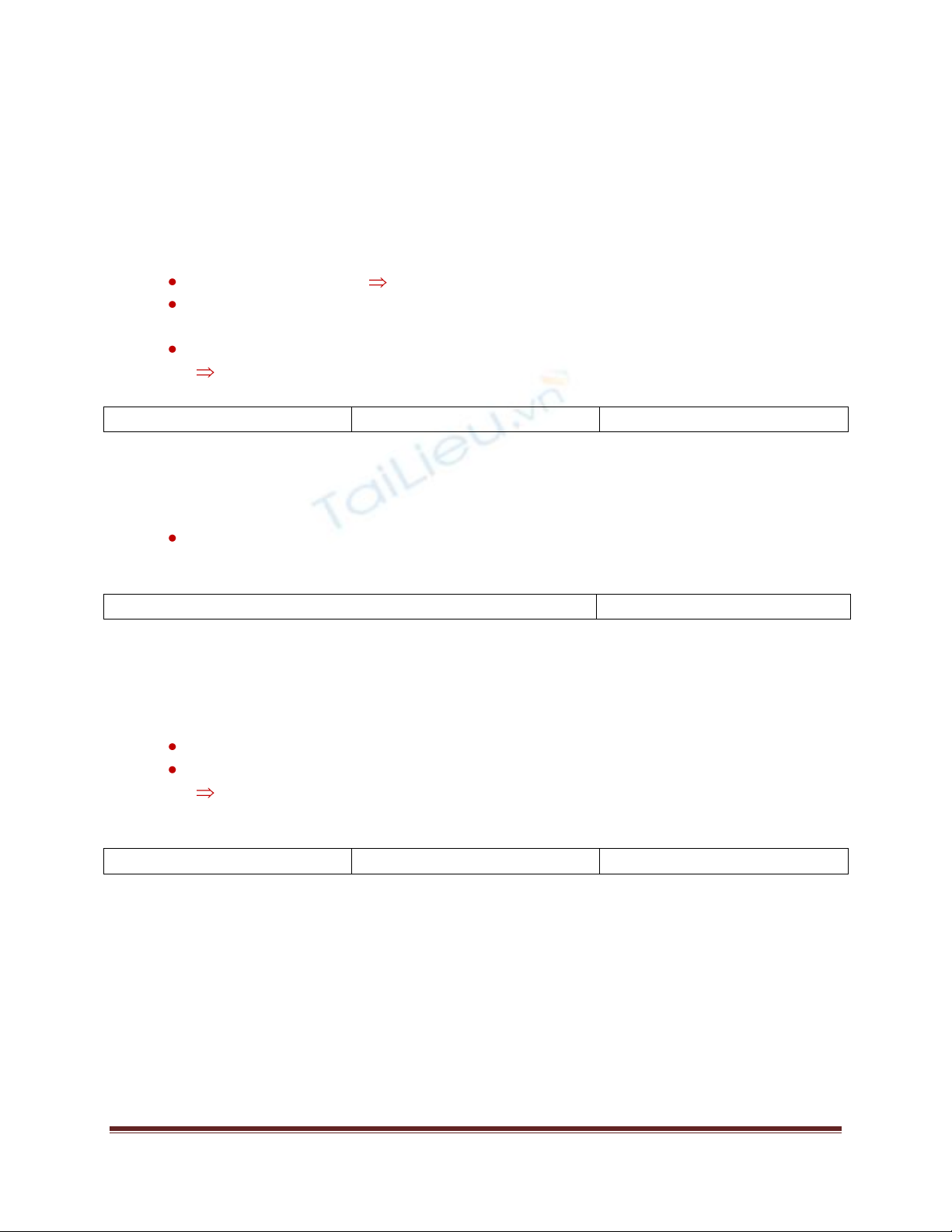

Tag

Line

Byte

7 bit

4 bit

3 bit

b. Giả sử cache dùng phương thức ánh xạ fully-associative. Trình bày khung dạng địa chỉ bộ

nhớ và xác định các thông số sau: số khối trong bộ nhớ chính và số dòng trong cache

Tương tự câu trên, số đơn vị có khả năng định vị địa chỉ là byte, bô nhớ chinh có 211 khối.

Một dòng trong cache có 8 byte nên cần 3 bit cho phần byte offset, phần tag là 14-

3=11 bit. Số dòng trong cache không xác định.

Tag

Byte

11 bit

3 bit

c. Giả sử cache dùng phương thức 4-way set associative với trường tag trong địa chỉ là 8 bit.

Trình bày khung dạng địa chỉ bộ nhớ và xác định các thông số sau: số khối trong bộ nhớ

chính, số dòng trong cache, số tập hợp trong cache

Số đơn vị có khả năng định vị địa chỉ là byte.

Bộ nhớ chinh có 211 khối.

Một dòng trong cache có 8 byte nên cần 3 bit cho phần byte offset, phần tag là 8 bit

số bit để xác định tập hợp là 14-8-3=3 bit => có 23 tập hợp trong cache, mỗi tập

hợp có 4 dòng => có tất cả 23 * 4 = 25 dòng trong cache.

Tag

Set

Byte

8 bit

3 bit

3 bit

Kiểm tra cuối HK – Kiến trúc Máy tính – CS2009 Trang 4/2

Bài 4: (1.5 điểm) Một số bộ xử lý có thanh ghi cờ đặc biệt để chứa các bit trạng thái như: bit

carry, bit overflow, … Mô tả sự khác nhau về chức năng giữa bit carry và bit overflow.

Cho ví dụ một tác vụ số học để minh họa sự khác nhau này.

Cờ carry được thiết lập khi tác vụ số học tạo ra bit carry vượt khỏi vị trí MSB của các toán hạng.

Cờ overflow được thiết lập khi tác vụ số học tạo ra bit carry vượt khỏi vị trí MSB của thanh ghi

vật lý chứa toán hạng.

Overflow xảy ra khi kích thước thanh ghi không đủ lớn để giữ kết quả của tác vụ số học, trong

khi cờ carry được dùng để chỉ thị vị trí MSB của giá trị kết quả lớn hơn (hoặc nhỏ hơn trong

trường hợp mượn) giá trị toán hạng 1 bit.

Ví dụ cộng 2 số nguyên 0x0100 và 0x0110 được lưu trong các thanh ghi 16 bit, kết quả thu được

0x1010, cờ carry được thiết lập, nhưng cờ overflow lại không có.

Kiểm tra cuối HK – Kiến trúc Máy tính – CS2009 Trang 5/2

Bài 5: (2 điểm) Cho đoạn chương trình sau:

loop: sw $t0, 0($t0)

lb $t1, 0($t0)

beq $t1, $t2, exit

addi $t0, $t0, 1

j loop

exit:

Giả sử trước khi thực thi đoạn chương trình trên giá trị của thanh ghi

$t0 = 0xFFFFFFF1

$t2 = 0x00000001

Xác định thời gian bộ xử lý MIPS đơn chu kỳ thực thi đoạn chương trình trên. Cho biết:

Thời gian thực thi của lệnh lb bằng thời gian thực thi của lệnh lw

Thời gian thực thi của lệnh addi bằng thời gian thực thi của lệnh add

Thời gian thực thi của các khối chức năng chính như sau:

Memory (đọc hoặc ghi): 100ps

Register file (đọc hoặc ghi): 20ps

ALU và các bộ cộng: 30ps

Thời gian thực thi bằng 0 đối với các bộ chọn kênh (multiplexor), bộ điều khiển (control

unit), bộ mở rộng dấu (sign extension unit), truy xuất thanh ghi PC.

Đáp án:

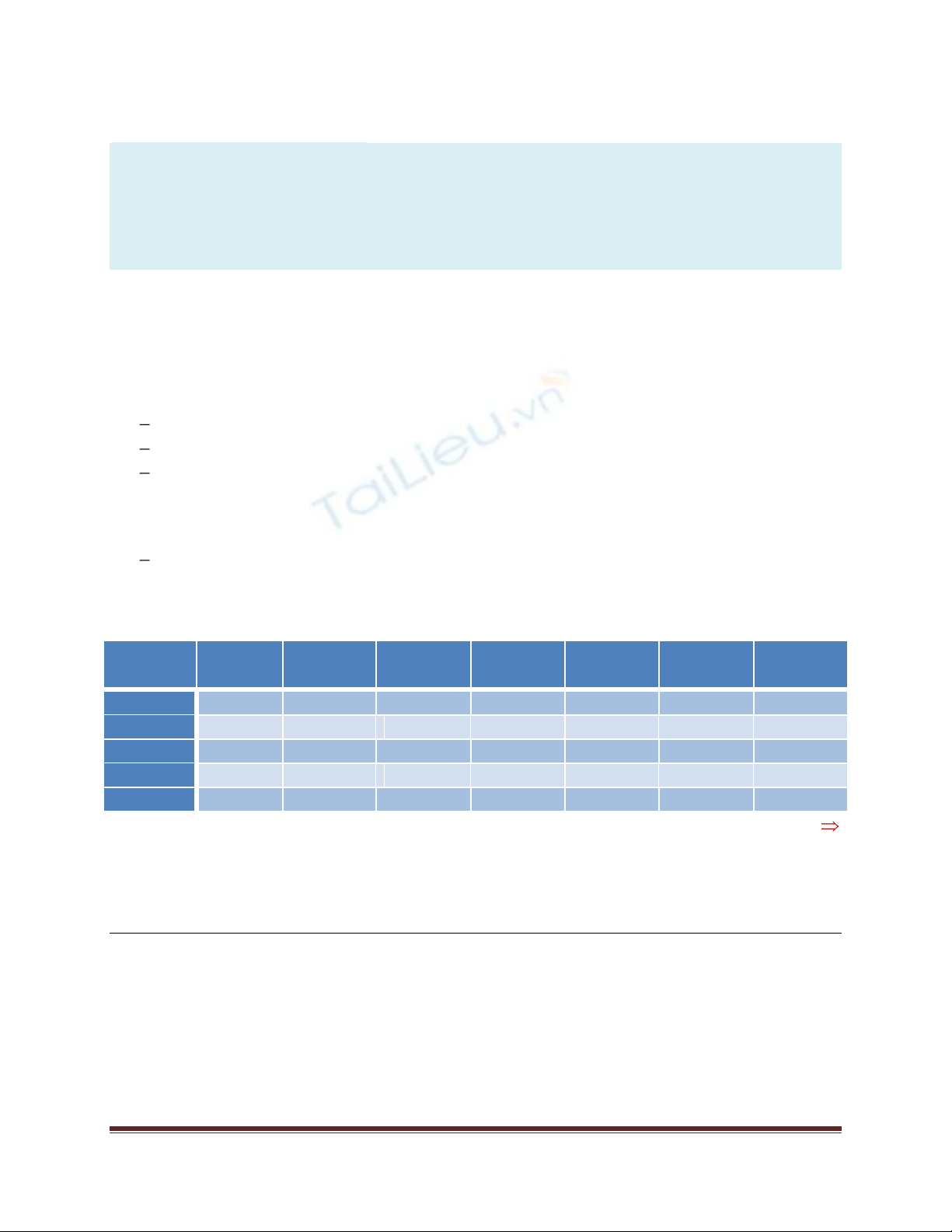

Thời gian thực thi của từng câu lệnh:

Câu lệnh

Số lần

thực thi

Nạp lệnh

Đọc từ

thanh ghi

Tác vụ

của ALU

Truy xuất

bộ nhớ

Ghi vào

thanh ghi

Thời gian

thực thi

sw

17

100

20

30

100

250

lb

17

100

20

30

100

20

270

beq

17

100

20

30

150

addi

16

100

20

30

20

170

j

16

100

100

($t0 và $t1 có cùng giá trị chạy từ 0xFFFFFFF1 đến 0xFFFFFFFF, 0x00000000, 0x00000001

17 giá trị; hai lệnh sau lệnh beq sẽ không thực hiện lần cuối)

Tổng thời gian thực thi = (250+270+150)*17 + (170+100)*16 = 15.710ps

![Giáo trình Sửa chữa máy in và thiết bị ngoại vi - Trường Cao đẳng Cơ điện Hà Nội [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251231/gaupanda090/135x160/47191775188546.jpg)