1

P&I Ch5-Digi In/Out 1

Ch 5. DIGITAL INTERFACING

Ghép nối hệtrung tâm với Thiết bịngoại vi qua các tín

hiệu logic 1/0

- PARALLEL IN/OUT

- PORTS: PRINCIPLE, PPI, CENTRONICS/LPT

- PCMCIA, DUAL PORTED RAM.

- INTERCACING TO DEVICES: KEY PAD, LED,

TEXT PANEL, ENCODER, STEP MOTOR, ...

- HI-POWER INTERFACE: RELAY, SCR, TRIAC,

POWER MOSFET, IGBT...

- SERIAL IN/OUT: SYNC, ASYNC,

- RS-232, RS-485, RS-422

- MODEM...

P&I Ch5-Digi In/Out 2

5.1. parallel interface: 5.1.1. nGuyªn lý

•In/Out nhiều bit đồng thời, nhanh, gần

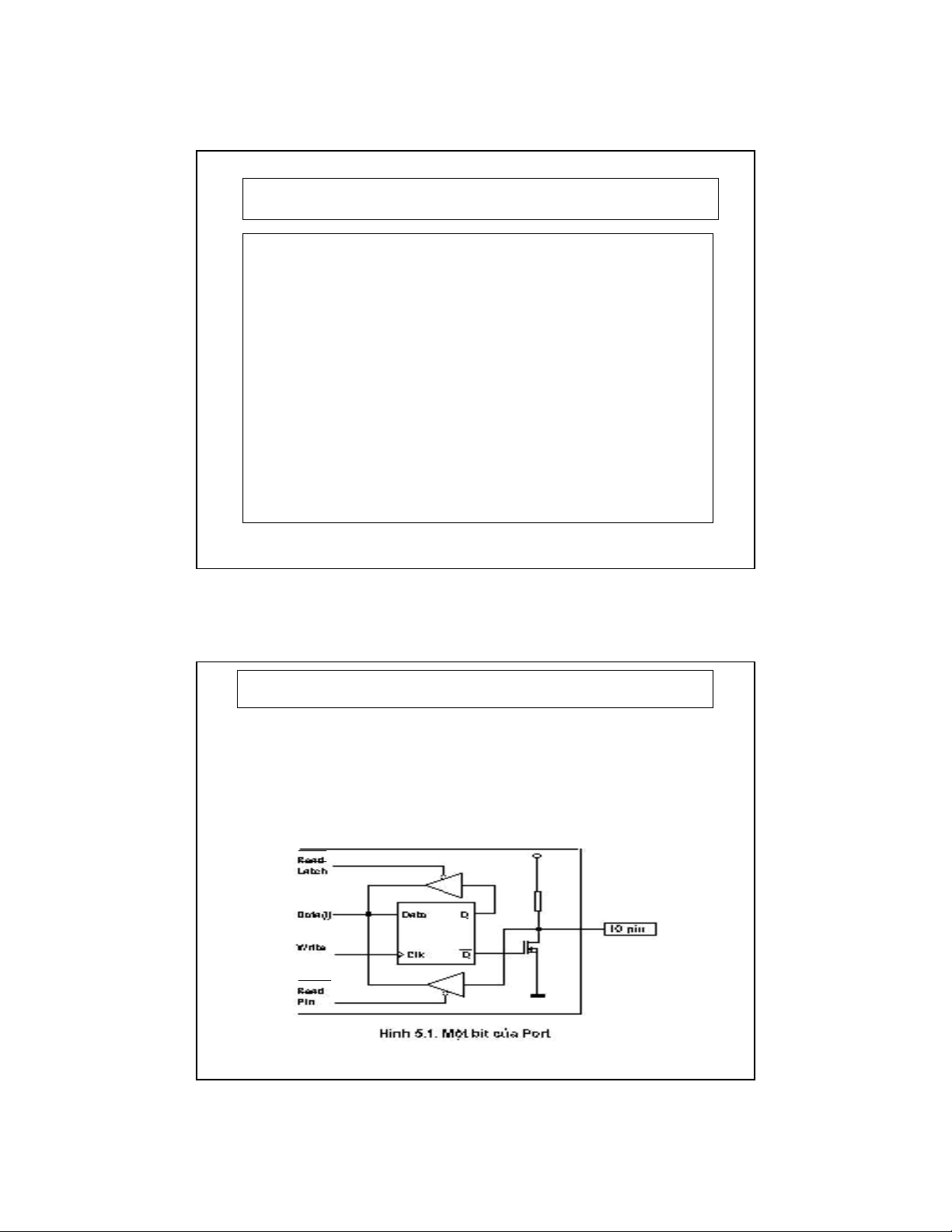

•a. A Port Line (1bit port):

– Output Port: Latched Output (chốt ra), D_Flip-Flops

– Unlatched Input, hình 5.1. single IO line/pin

2

P&I Ch5-Digi In/Out 3

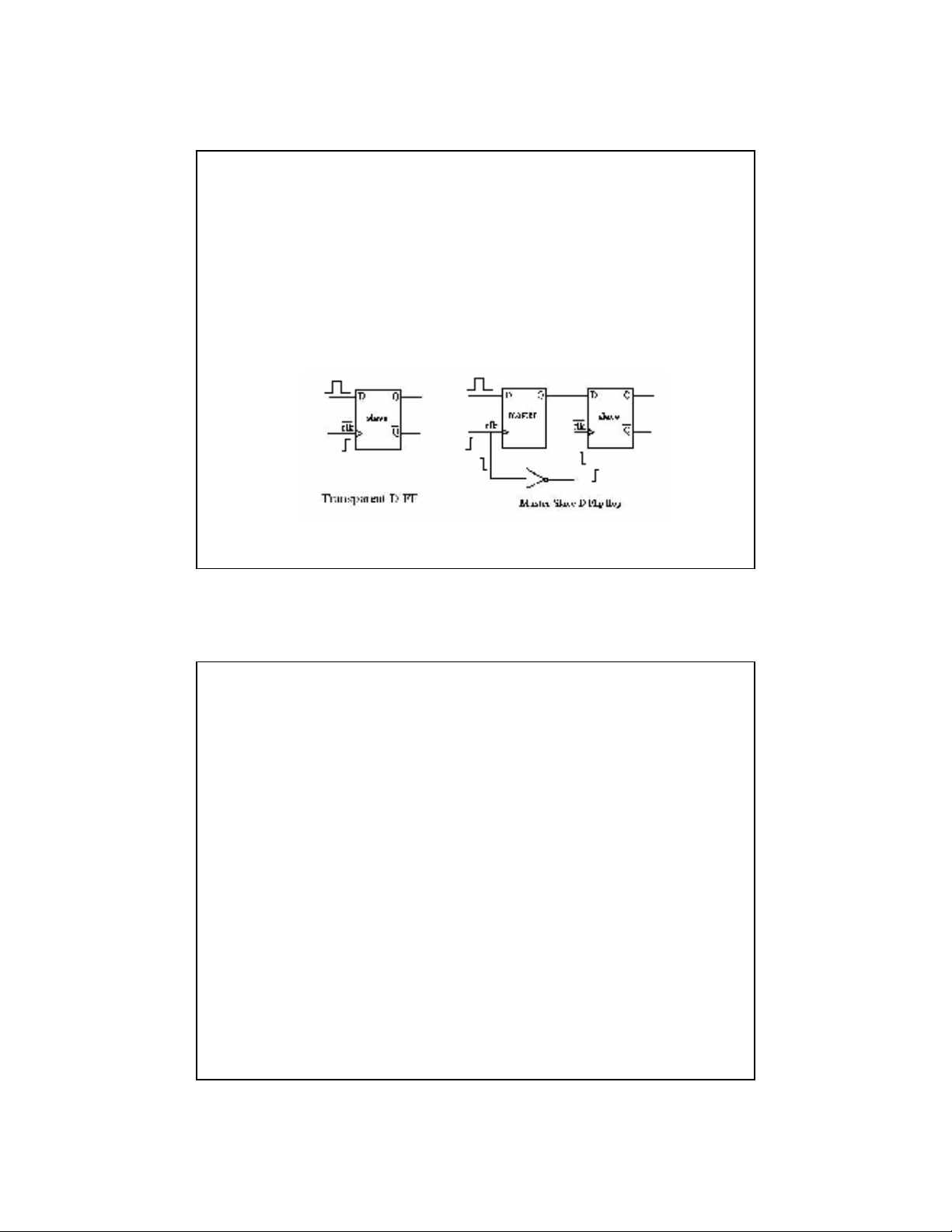

• D Flip-Flop (D trigger):

– Là 1 trong những phần tử cơ bản của hệ

dãy,

– D – data, lưu giữ1 bit sốliệu.

– 4/6/8 D flip-flop => tạo ra 4/6/8 bit register,

nhiều registers đóng trong 1 chip là SRAM.

P&I Ch5-Digi In/Out 4

– Output:

• Q - ứng với giá trịdata input vào thờiđiểm có clock

• /Q – đảo của Q.

– Input:

• Data bit: 1 hoặc 0

• Clock, thường là sườn lên, ghi nhận giá trịcủa data

và lưu lại cho đến khi có bit sốliệu khác ghi đè lên.

• [Có thểcó] clear – xóa; Preset – đặttrước

– Có 2 loại: Transparent (HC373) và Master-

Slave (HC374)

3

P&I Ch5-Digi In/Out 5

H. 501 b, c

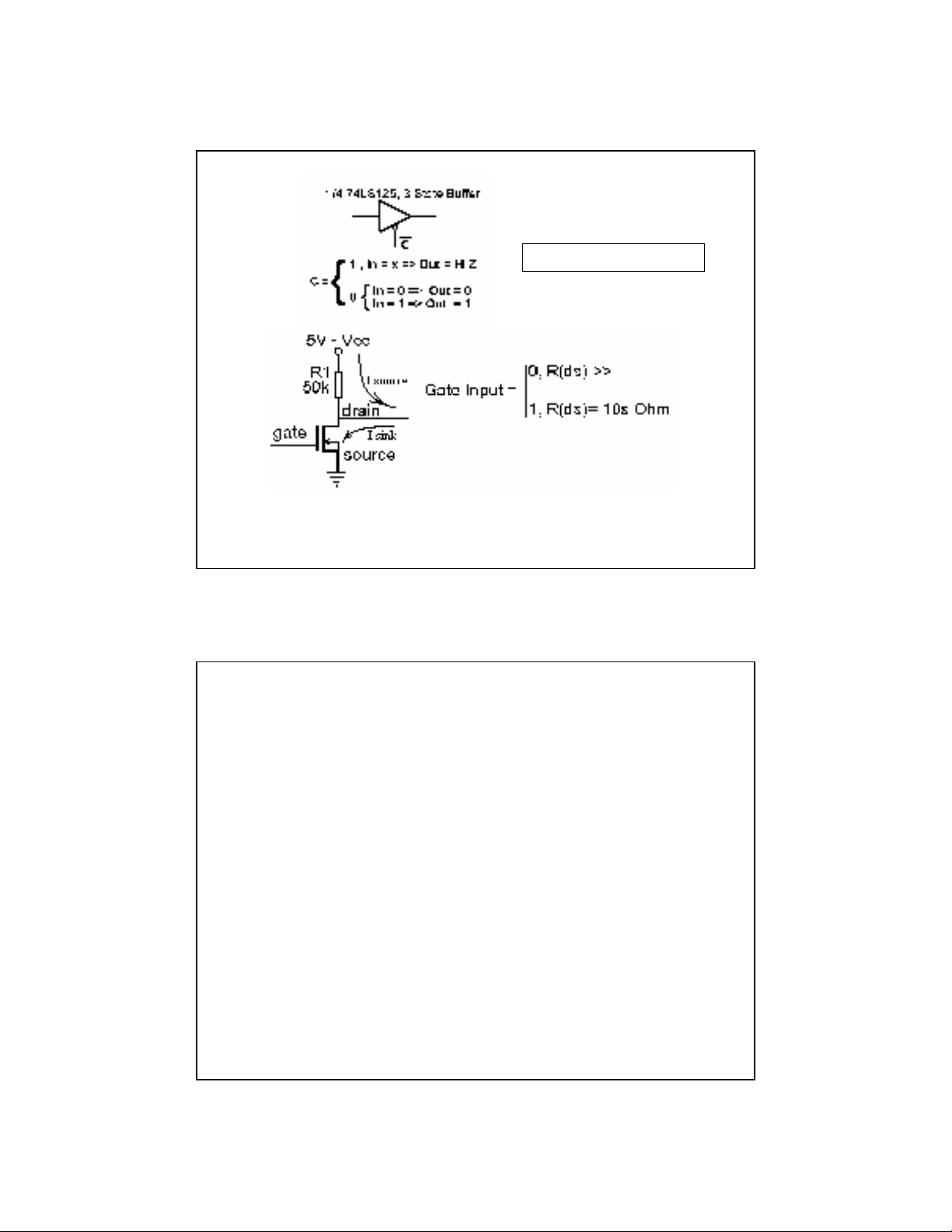

MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

P&I Ch5-Digi In/Out 6

• Write pin: bit 0 or 1, clock =

– Write bit 0: D flip-flop => Q = 0; -Q = 1 =>

gate = 1 => R(ds) MOSFET = ON => pin = 0

– Write bit 1 D flip-flop => Q = 1; -Q = 0 =>

gate = 0 => R(ds) MOSFET = OFF => pin = 1

• Read pin: (Input line– out “1” firstly)-

ReadPin = 0 (!) => open 3 state lower

buffer => 1/0 from pin => data bus (i)

• ReadLatch (Reading bit out previously) :

-ReadLatch = 0 (!) => open 3 state higher

buffer => 1/0 from pin => data bus (i)

4

P&I Ch5-Digi In/Out 7

• Ý nghĩa Read Latch, ví dụthông qua việc tạo 1

xung out, 2ms :

– x86, LPT port, bit0, g/n remainders

• mov dx, 378h ; LPT 1 data out port

• in al, dx ;

• or al,1 ;

• out dx,al ; set bit 0

• call delay(2) ;

• and al, 0feh ; reset bit

• out dx,al

– Atmega64, PA0:

• orl PA0, 1

• call delay(2)

• anl PA0, 0feh

P&I Ch5-Digi In/Out 8

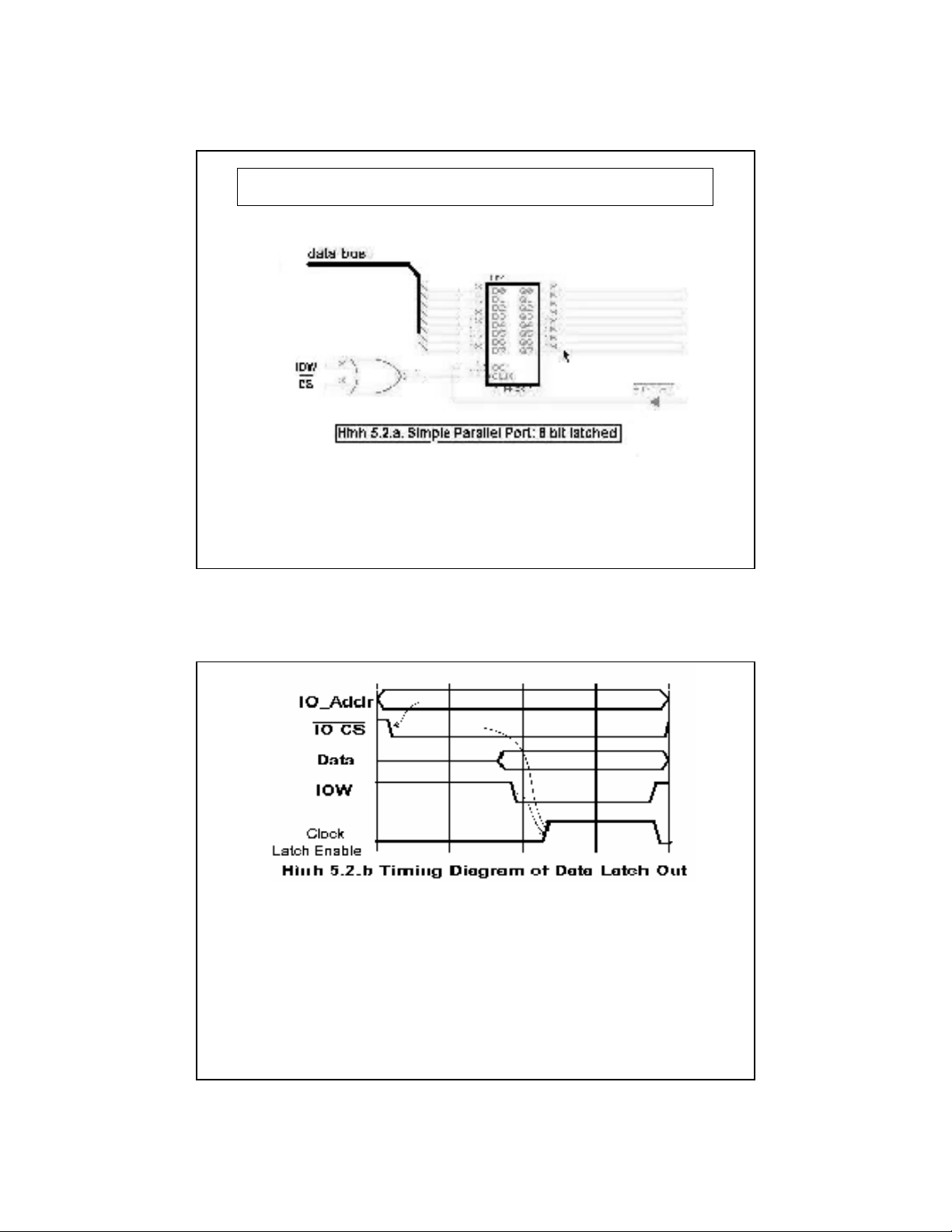

5.1. PARALLEL INTERFACE: 5.1.1. NGUYÊN LÝ

Simple In-Out Ports:

Cổng ra đơn giản có chốt (latched output port,

based on 74 HC 374/HC373/HC273/HC574...,

8 bit Register), (fig. 5.2)

Cổng vào đơn giản không chốt (unlatched input

port, based on 3 state buffer - 74HC244)

Cổng vào có chốt (Latched Input Port), chú ý

status flag

5

P&I Ch5-Digi In/Out 9

74LS273/373/374/574…

Ứng dụng: ghép nối DAC, LED display…

5.1. PARALLEL INTERFACE: 5.1.1. NGUYÊN LÝ

P&I Ch5-Digi In/Out 10

Port[Parallel_Out]:= solieu; Lệnh Pascal

Out Port: 74 HC 374:

CPU phát địa chỉra IO space => có t/h -IO CS

Phát data và -IOW => có t/h Clock = (Rising Edge) =>

data được chốt vào HC374

Ng/vi => OutControl = 0 => open 3 state output