5/14/2013

1

Chương 5:VI MẠCH ĐIỀU KHIỂN

TRONG MÁY VI TÍNH PC

Phạm Văn Thành

Nội dung

I. Vi mạch điều khiển trong máy tính

XT/AT

II. Vi mạch điều khiển trong máy tính

PC hiện đại.

2

5/14/2013

2

Nội dung

I. Vi mạch điều khiển trong máy tính

XT/AT

II. Vi mạch điều khiển trong máy tính

PC hiện đại.

3

máy tính XT/AT

I

.

Vi mạch điều khiển trong

máy tính XT/AT

1. Vi mạch định thời lập trình được

PIT/8253, PIT/8254

2. Vi mạch giao diện ngoại vi lập trình được

8255

3. Vi mạch điều khiển ngắt lập trình được

8259A

4. Vi mạch điều khiển truy nhập bộ nhớ trực

tiếp DMAC 8237

4

5/14/2013

3

trong máy tính XT/AT

I

.

Vi mạch điều khiển

trong máy tính XT/AT

Vi mạch định thời lập trình được (Programmable

Interval Timer) PIT/8253, PIT/8254:

•Là một vi mạch phụ rất quan trong trong các thế

hệ vi xử lý của Intel.

•Có thể đáp ứng được các yêu cầu ứng dụng khác

nhau trong hệ vi xử lý: đếm thời gian, đếm sự

kiện, đếm tần số, tạo ra dãy xung, .v.v.

•Có ba bộ đếm 16 bit và một thanh ghi điều khiển

(8254).

•Các đường A0 và A1 định địa chỉ 3 bộ đếm và

thanh ghi điều khiển.

5

trong máy tính XT/AT

I.

Vi mạch điều khiển

trong máy tính XT/AT

•Các địa chỉ cổng cứng của vi mạch này trong máy vi

tính cá nhân:

040h: bộ đếm 0

041h: bộ đếm 1

042h: bộ đếm 2

043h: Thanh ghi điều khiển: xác định chế độ làm việc cho hệ

thống

•Nội dung ban đầu của ba bộ đếm đều có thể lập trình

từ CPU để thay đổi.

•Có thể điều khiển được hoạt động của các bộ đếm

bằng tín hiệu từ bên ngoài thông qua chân cổng (gate)

để cho phép bắt đầu đếm (gate =1) hay để buộc kết

thúc quá trình đếm (gate =0).

6

Vi mạch định thời lập trình được

PIT/8253, PIT/8254

5/14/2013

4

trong máy tính XT/AT

I.

Vi mạch điều khiển

trong máy tính XT/AT

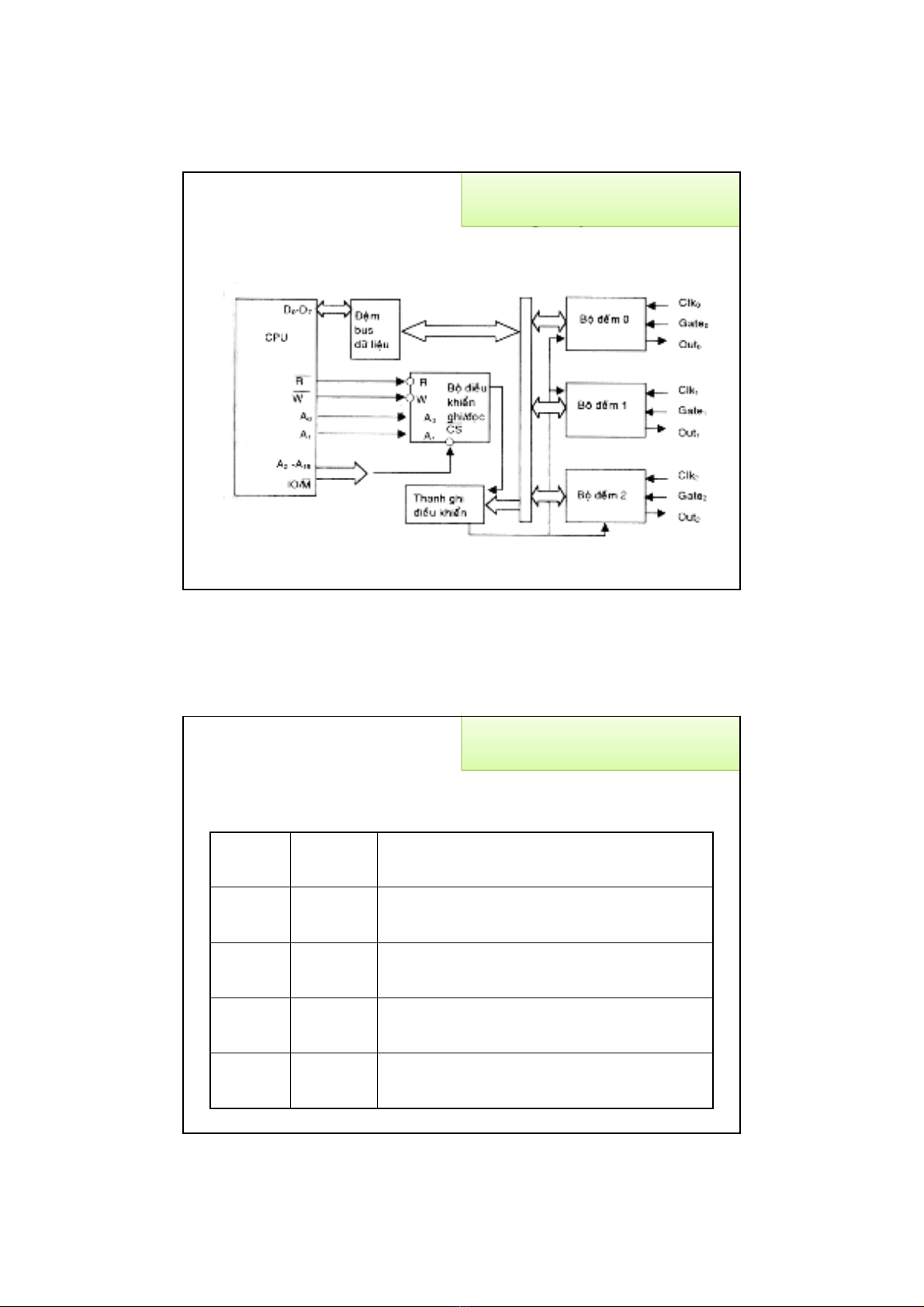

Sơ đồ khối của 8253/8254:

7

Vi mạch định thời lập trình được

PIT/8253, PIT/8254

trong máy tính XT/AT

I

.

Vi mạch điều khiển

trong máy tính XT/AT

Sơ đồ khối của 8253/8254:

8

Vi mạch định thời lập trình được

PIT/8253, PIT/8254

A1A0Chức năng

0 0 Chọn bộ đếm 0

0 1 Chọn bộ đếm 1

1 0 Chọn bộ đếm 2

1 1 Chọn thanh ghi điều khiển

5/14/2013

5

trong máy tính XT/AT

I.

Vi mạch điều khiển

trong máy tính XT/AT

Sơ đồ khối của 8253/8254:

9

Vi mạch định thời lập trình được

PIT/8253, PIT/8254

Bảng chức năng theo các cửa vào điều khiển nhưsau :

A1 A0 R W CS

0 0 0 1 0 Đọc ra từbộ đếm 0

0 1 0 1 0 Đọc ra từbộ đếm 1

1 0 0 1 0 Đọc ra từbộ đếm 2

0 0 1 0 0 Nạp vào bộ đếm 0 bằng từxuất phát

0 1 1 0 0 Nạp vào bộ đếm 1 bằng từxuất phát

1 0 1 0 0 Nạp vào bộ đếm 2 bằng từxuất phát

1 1 1 0 0 Ghi vào từ điều khiển

x x x x 1 Bus data ở trạng thái ngắt ( R cao )

x x 1 1 0 Bus data ở trạng thái điện trởcao

trong máy tính XT/AT

I.

Vi mạch điều khiển

trong máy tính XT/AT

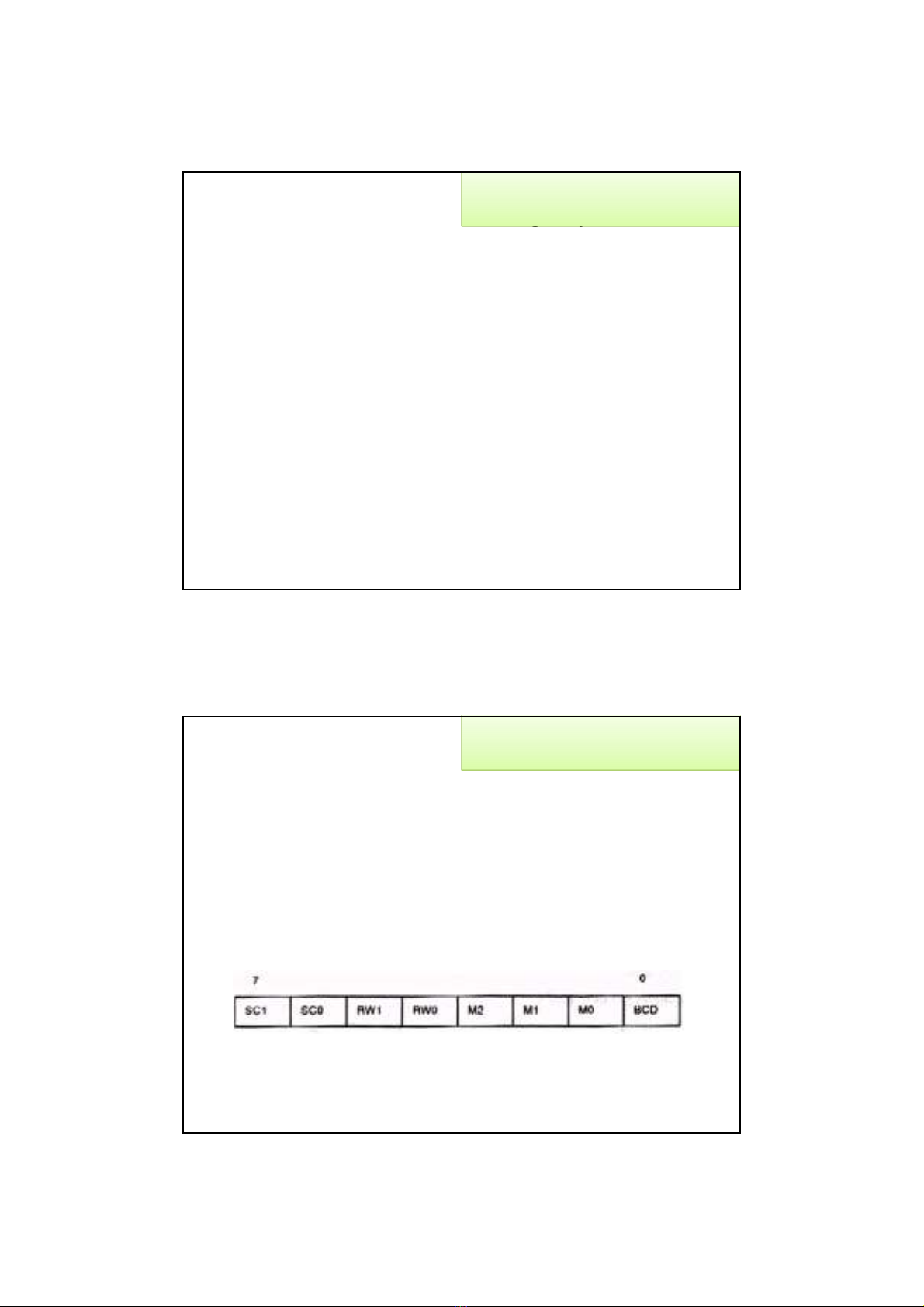

a. Khởi động PIT8253/8254

–Vi mạch 8254 dùng thanh ghi điều khiển để định

nghĩa chế độ làm việc của ba bộ đếm.

–Để khởi động PIT ta phải ghi từ điều khiển CW

(control word) vào thanh ghi từ điều khiển.

–Dạng thức của thanh ghi từ điều khiển

10

Vi mạch định thời lập trình được

PIT/8253, PIT/8254