b Tạo ra các chương trình để nạp vào ROM của hệ thống vi xử lý

c Thực hiện chương trình nguồn

d Tạo ra chương trình mã máy từ chương trình nguồn.

96/ Kể cả cổng điều khiển 8255 sẽ có số cổng là:

a 5

b 4

c 3

d 6

97/ Đối với 8255 các tín hiệu A1, A0 là các ngõ:

a Ra

b Không kết nối

c Vào

d Hai chiều.

98/ Sau khi khởi động ở chế độ 0, một cổng vào ra của 8255 có thể:

a Luôn ở mức cao.

b Không điều khiển được.

c Truyền dữ liệu theo một chiều

d Truyền dữ liệu theo hai chiều.

99/ Nếu cấp cho 8255 các tín hiệu: CS=1; A1=0; A0=1; RD=0; WR=1 thì sẽ có thể:

a Không đọc ghi 8255 được

b Đọc dữ liệu từ cổng B của 8255.

c Đọc dữ liệu từ cổng C của 8255.

d Đọc dữ liệu từ cổng A của 8255.

100/ Trong chế độ 1 tín hiệu OBF là một tín hiệu:

a Hai chiều.

b Vào

c Không sử dụng.

d Ra

101/ Ở một cổng vào của 8255 trong chế độ 1 tín hiệu nào tác động sẽ xoá tín hiệu INTR.

a IBF

b RD

c WR

d ACK

102/ Ở một cổng vào của 8255 trong chế độ 1 tín hiệu nào tác động sẽ xoá tín hiệu IBF.

a INTR

b WR

c RD

d ACK

103/ Trong chế độ 1 của 8255 thì INTE là:

a Là một bit bên trong của 8255

b Một ngõ vào.

c Là tín hiệu hai chiều

d Là một ngõ ra.

17

104/ Ở một cổng ra của 8255 trong chế độ 1 tín hiệu INTR sẽ tác động mức 1 khi:

a OBF=1; ACK=0; INTE=1

b OBF=1; ACK=1; INTE=0

c OBF=0; ACK=1; INTE=1

d OBF=1; ACK=1; INTE=1

105/ Từ điều khiển 0000 0010B là từ điều khiển gì của 8255:

a Từ điều khiển xoá bit PC1 của cổng C

b Từ điều khiển chế độ 0 với cổng B là ngõ vào, các cổng còn lại là ngõ ra.

c Từ điều khiển ở chế độ 2 với các cổng là ngõ ra.

d Từ điều khiển lập bit PC1 của cổng C

106/ Từ điều khiển để cổng A output, cổng B input, PC0-PC3 input, PC4-PC7 output chế độ 0

sẽ là:

a 80H

b 81H

c 82H

d 83H

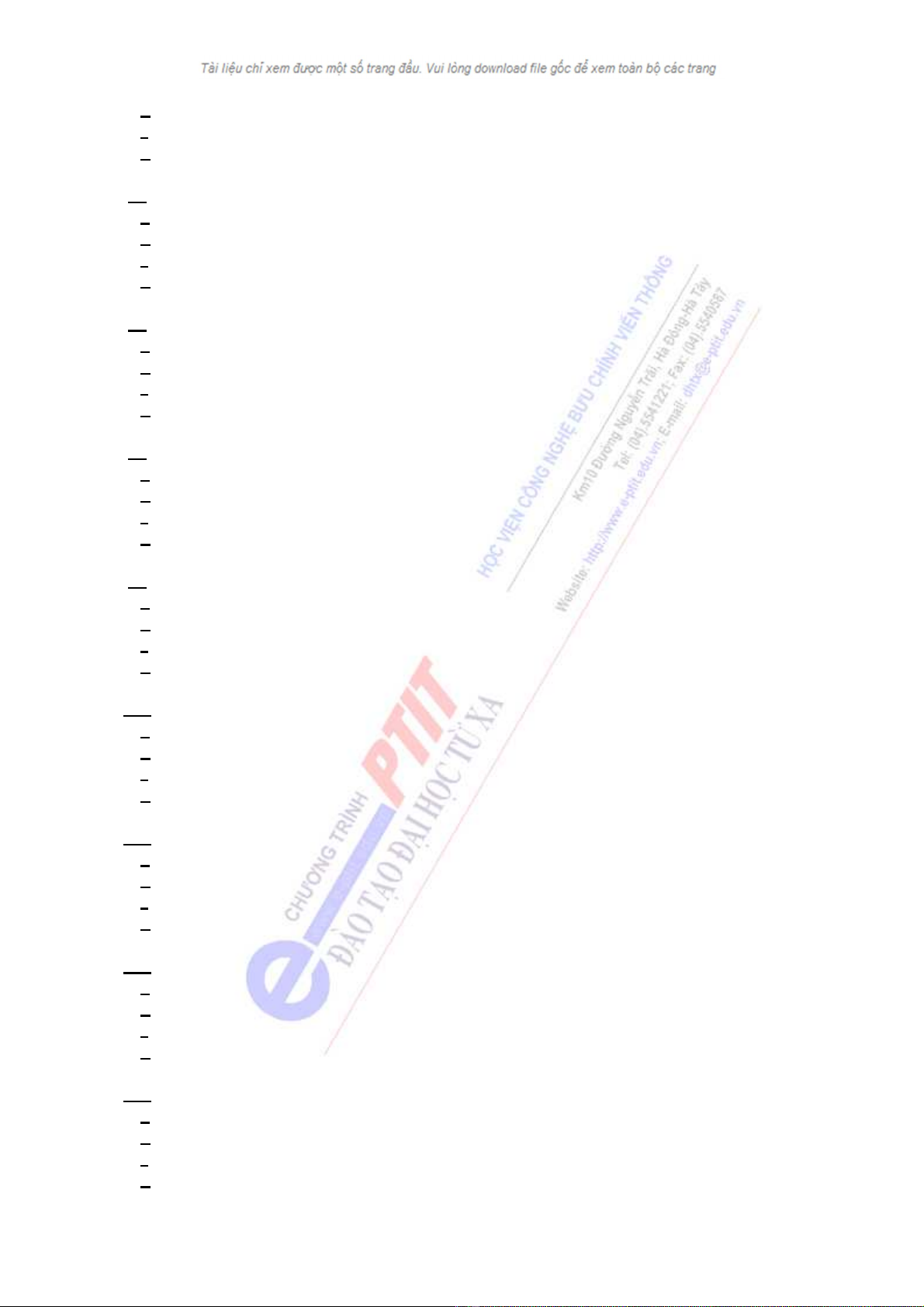

107/ Trong sơ đồ kết nối dưới các cổng A, B, C và điều khiển sẽ có địa chỉ lần lượt là:

:

a C1H, C3H, C5H, C7H

b C1H, C2H, C3H, C4H

c C0H, C1H, C2H, C3H

d C0H, C2H, C4H, C6H

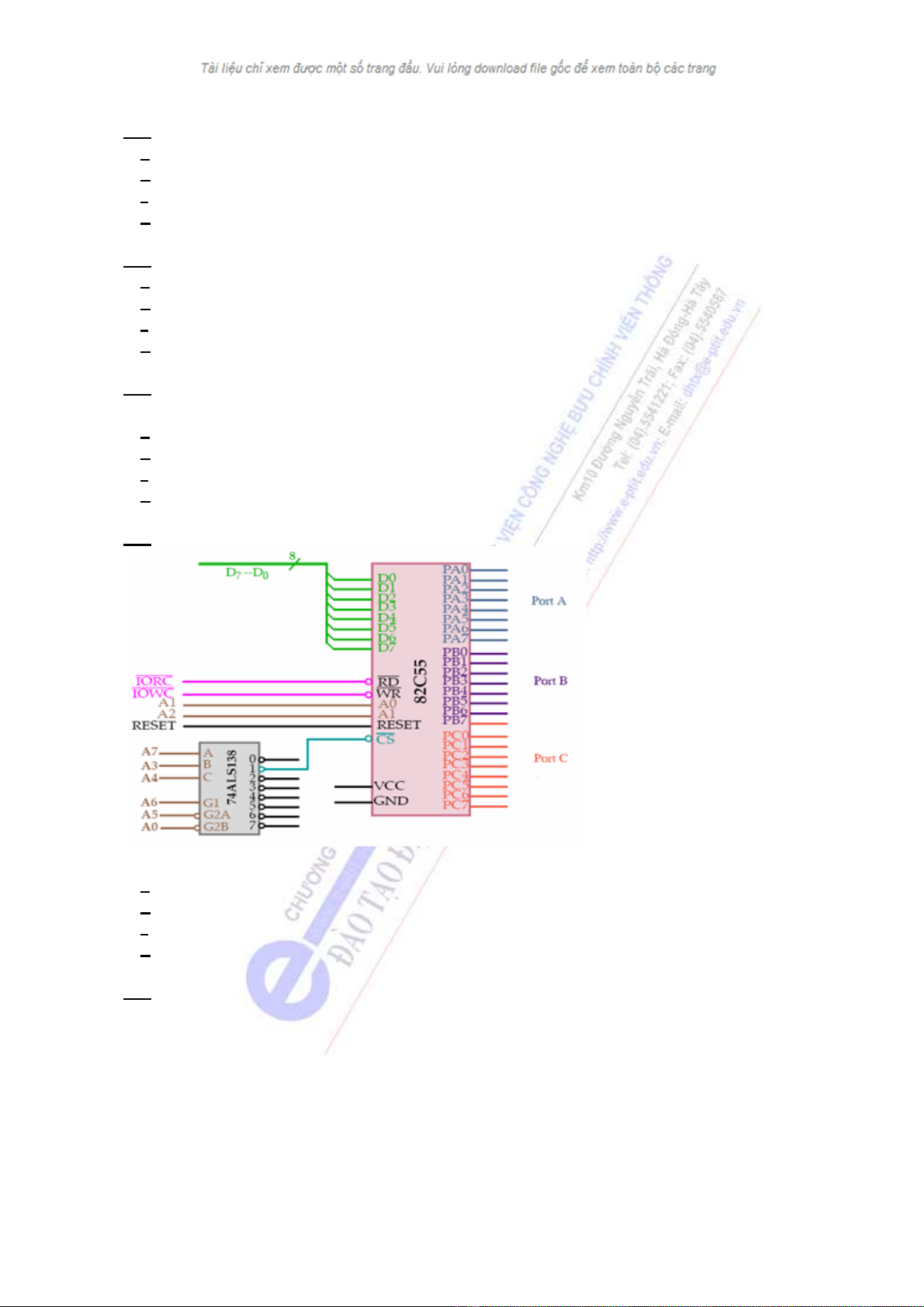

108/ Với mạch kết nối như hình vẽ dưới các cổng A, B, C và điều khiển sẽ lần lượt có địa chỉ

là:

18

:

a Cả 03 đáp án còn lại đều đúng

b 70H, 72H, 74H, 76H

c 00H, 02H, 04H, 06H

d 01H, 03H, 05H, 07H

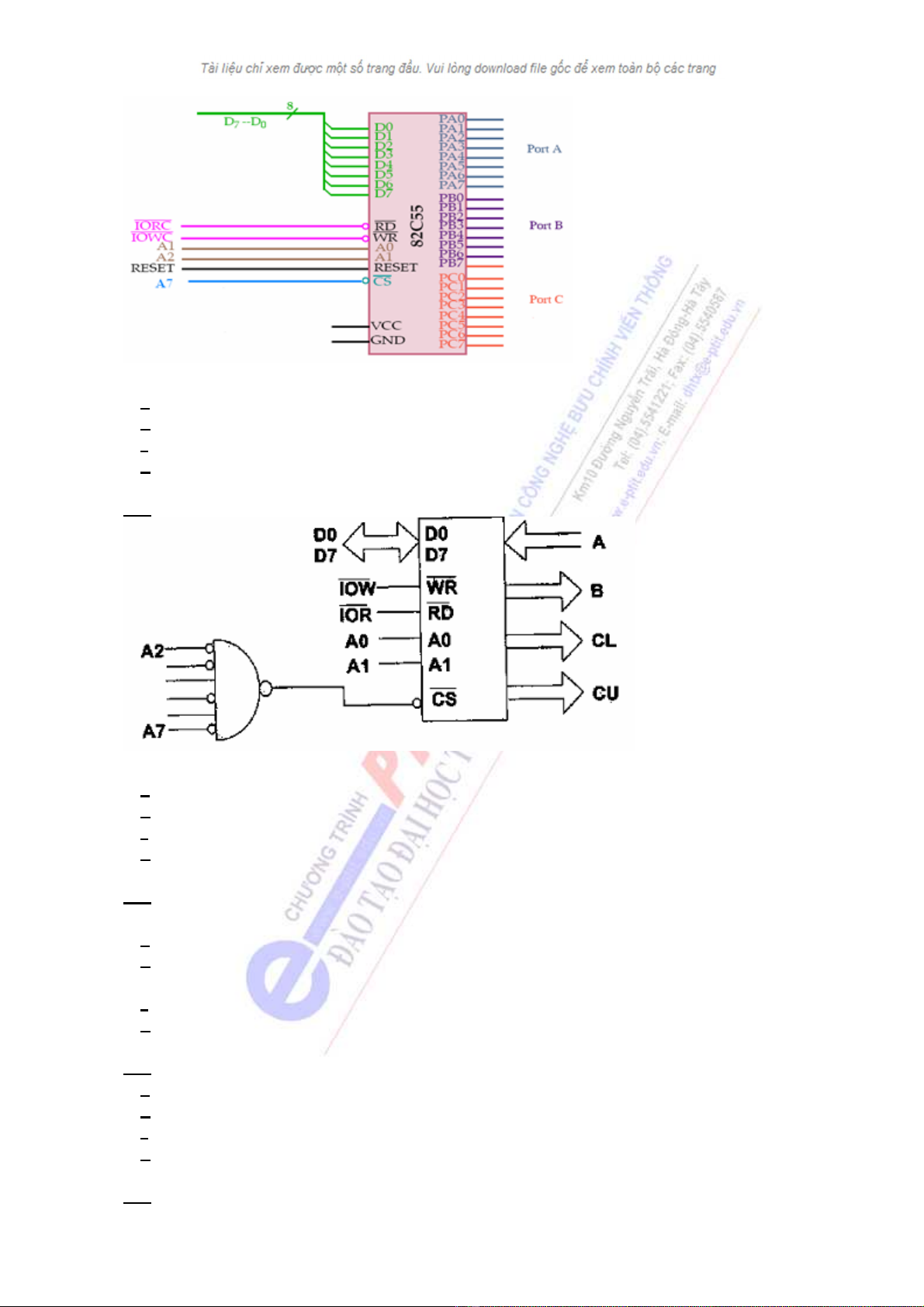

109/ Với sơ đồ kết nối như hình vẽ dưới cổng điều khiển sẽ có địa chỉ là:

:

a 52H

b 54H

c 53H

d 55H

110/ Giả sử cổng A của 8255 có địa chỉ là 70H, để đọc dữ liệu từ cổng A có thể sử dụng các

lệnh nào sau đây:

a IN 70H,AL

b MOV DX,70H

IN DX,AL

c IN AL,70H

d Cả ba đáp án còn lại đều đúng.

111/ 8551 là bộ truyền nhận nối tiếp theo kiểu:

a Song công

b Đơn công

c Bán song công

d Thanh ghi dịch

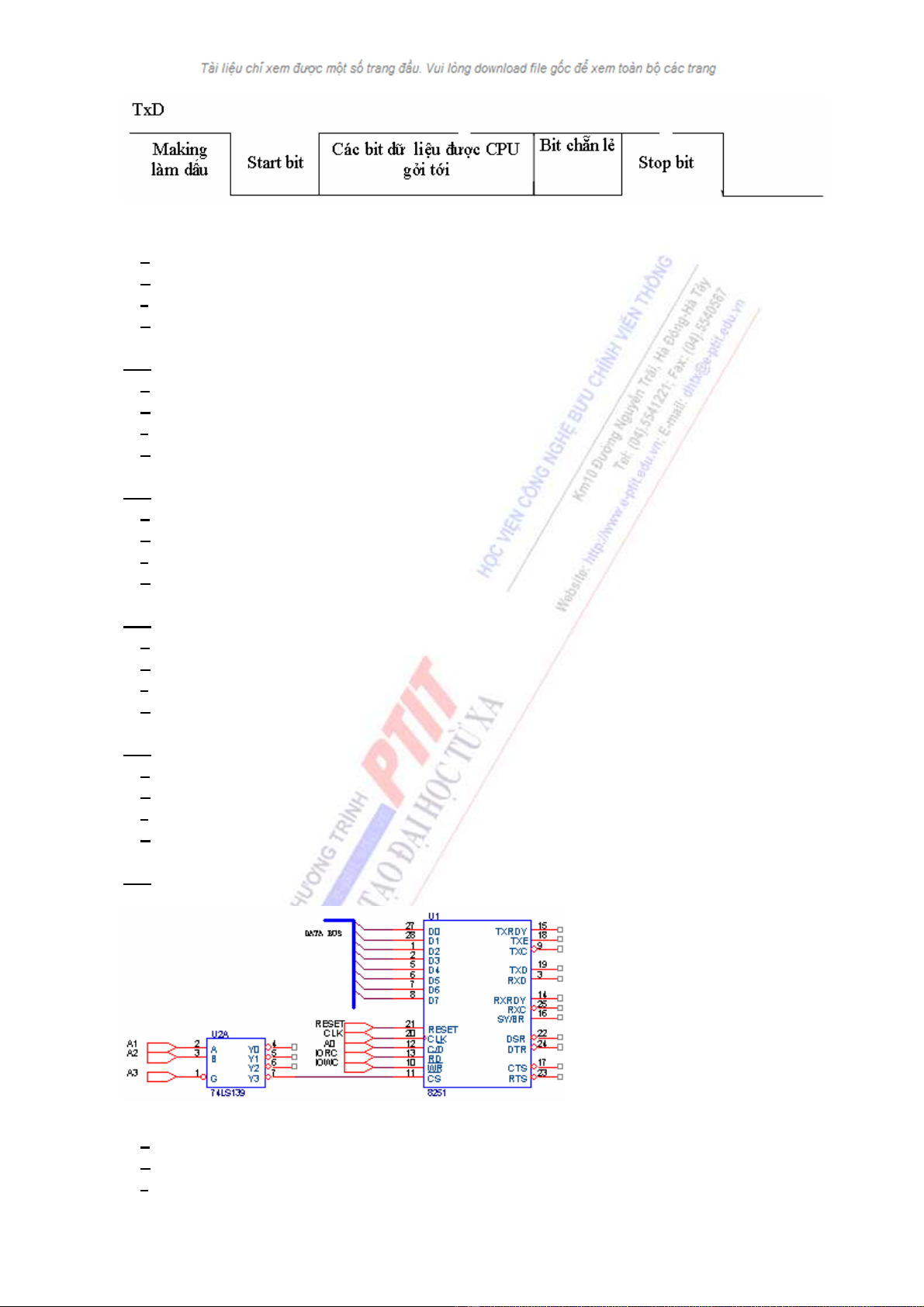

112/ Hình vẽ sau biểu diển cho khung truyền dữ liệu của 8251 ở chế độ :

19

a Thanh ghi dịch.

b Cận đồng bộ

c Cả đồng bộ và cận đồng bộ

d Đồng bộ

113/ Trong khung truyền cận đồng bộ bit Stop có thể chiếm:

a 1.5 bit

b Cả ba đáp án còn lại đều đúng

c 1 bit

d 2 bit

114/ 8251 có mấy địa chỉ có thể đọc ghi.

a 3

b 4

c 1

d 2

115/ Tín hiệu C/D của 8251 có thể nối tới BUS nào của hệ thống?

a Điều khiển

b Dữ liệu

c Địa chỉ

d Tới bộ giải mã địa chỉ.

116/ Tín hiệu TxEmpty của 8251 là một tín hiệu:

a Hai chiều

b Không sử dụng.

c Ra

d Vào

117/ Nếu kết nối 8251 với BUS hệ thống như hình vẽ dưới thì khi đọc từ trạng thái của 8251

có thể dùng địa chỉ bao nhiêu:

u?

a F0H

b 03H

c 07H

20

d 30H

118/ Khi lập trình cho 8251 giá trị đầu tiên cần gửi tới 8251 là:

a Ký tự đồng bộ

b Từ lệnh

c Một dữ liệu bất kỳ.

d Từ chế độ

119/ Khi khởi động 8251 các bit B2B1 trong từ chế độ sử dụng để:

a Xác định tốc độ truyền nhận dữ liệu

b Số lượng bit stop

c Không sử dụng.

d Xác định độ dài dữ liệu truyền.

120/ Bit ESD trong từ chế độ của 8251 sử dụng để:

a Xác định có cho phép kiểm tra chẵn lẻ không

b Xác định số ký tự đồng bộ

c Xác định kiểm tra chẵn hay kiểm tra lẻ.

d Xác định chế độ đồng bộ

121/ Bit RTS trong từ lệnh của 8251 sử dụng để:

a Xoá lỗi xảy ra khi truyền nhận dữ liệu

b Cho phép tìm từ đồng bộ.

c Reset lại 8251

d Tác động một ngõ ra của 8251

122/ Bit OE trong từ trạng thái của 8251 là một bit để:

a Báo xảy ra lỗi

b Báo bộ đệm truyền rỗng

c Báo bộ đệm nhận rỗng.

d Báo 8251 chưa được khởi động xong.

123/ Trong các hệ thồng vi điều khiển thì:

a CPU, bộ nhớ và vào ra nằm trong một chip

b CPU, bộ nhớ và vào ra đều là các chip riêng

c Chỉ có CPU và bộ nhớ nằm trong một chip.

d Chỉ có CPU và vào ra nằm chung một chip

124/ Số lượng cổng vào ra song song của 8051 là:

a 2

b 3

c 4

d 5

125/ Tín hiệu EA của 8051 là một tín hiệu:

a Cấp clock của 8051.

b Ra của 8051

c Hai chiều của 8051

d Vào của 8051

126/ Sau khi khởi động thanh ghi SP của 8051 có giá trị bằng:

21

![Đề thi Vi xử lý học kì 1 năm 2024-2025 có đáp án [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250401/lakim0906/135x160/6811743476334.jpg)

![Bài giảng Tổ chức - Cấu trúc Máy tính II Đại học Công nghệ Thông tin (2022) [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/8531747304537.jpg)