Bài gi ng môn h c: K thu t ghép n i máy tínhả ọ ỹ ậ ố

Bài m đ uở ầ 3

Ch ng 1Đ i c ng v k thu t ghép n i máy tínhươ ạ ươ ề ỹ ậ ố ...................................................... 4

1.1Yêu c u trao đ i tin c a máy vi tính đ i v i môi tr ng bên ngoàiầ ổ ủ ố ớ ườ .............................................. 4

1.1.1.Yêu c u trao đ i tin v i ng i đi u hànhầ ổ ớ ườ ề ............................................................................... 4

1.1.2.Yêu c u trao đ i tin v i thi t b ngoài thông d ngầ ổ ớ ế ị ụ ................................................................. 4

1.1.3.Yêu c u trao đ i tin trong m ng máy tínhầ ổ ạ ............................................................................... 4

1.2D ng và các lo i tin trao đ i gi a máy vi tính và thi t b ngoài (TBN)ạ ạ ổ ữ ế ị ......................................... 4

1.2.1.D ng tin (s )ạ ố ............................................................................................................................. 4

1.2.2.Các lo i tinạ ................................................................................................................................ 5

1.3Vai trò nhi m v và ch c năng c a kh i ghép n i (KGN)ệ ụ ứ ủ ố ố ............................................................ 5

1.3.1.Vai trò ........................................................................................................................................ 5

1.3.2.Nhi m vệ ụ .................................................................................................................................. 5

1.3.3.Ch c năngứ ................................................................................................................................. 6

1.4C u trúc chung c a m t kh i ghép n iấ ủ ộ ố ố ........................................................................................... 7

1.5Ch ng trình ph c v trao đ i tin cho kh i ghép n iươ ụ ụ ổ ố ố .................................................................... 8

Ch ng 2Giao ti p v i tín hi u t ng tươ ế ớ ệ ươ ự ........................................................................ 9

2.1Khái ni m tín hi u analog và h đo l ng đi u khi n sệ ệ ệ ườ ề ể ố ............................................................. 9

2.2Chuy n đ i tín hi u s sang t ng t DACsể ổ ệ ố ươ ự ................................................................................. 9

2.2.1.Các tham s chính c a m t DACố ủ ộ ..................................................................... 10

2.2.2.DAC chia đi n tr (Resistive Divider DACs)ệ ở ........................................................................ 11

2.2.3.DAC tr ng s nh phân (Binary Weighted DACs)ọ ố ị ................................................................. 11

2.2.4.DAC đi u bi n đ r ng xung (PWM DACs)ề ế ộ ộ ....................................................................... 12

2.3Chuy n đ i tín hi u t ng t - s ADCs: ể ổ ệ ươ ự ố ................................................................................... 12

2.3.1.Các tham s chính c a m t ADCố ủ ộ ........................................................................................... 13

Ch ng 3Th t c trao đ i tin c a máy vi tínhươ ủ ụ ổ ủ ............................................................... 14

3.1Các ch đ trao đ i tin c a máy vi tínhế ộ ổ ủ ......................................................................................... 14

3.2Trao đ i tin ng t vi x lýổ ắ ử ............................................................................................................... 15

3.2.1.Các lo i ng t c a máy vi tính PCạ ắ ủ .......................................................................................... 15

3.2.2.X lý ng t c ng trong IBM - PC:ử ắ ứ .......................................................................................... 18

3.2.3.L p trình x lý ng t c ng:ậ ử ắ ứ ..................................................................................................... 21

3.3Trao đ i tin tr c ti p kh i nhổ ự ế ố ớ ...................................................................................................... 24

3.3.1.C ch ho t đ ng:ơ ế ạ ộ ................................................................................................................. 24

3.3.2.Ho t đ ng c a DMAC:ạ ộ ủ .......................................................................................................... 24

3.3.3.Chip đi u khi n truy nh p b nh tr c ti p DMAC 8237 (Direct Memory Accessề ể ậ ộ ớ ự ế

Controller) ........................................................................................................................................ 25

Ch ng 4Rãnh c m m r ngươ ắ ở ộ ......................................................................................... 31

4.1Đ t v n đặ ấ ề ..................................................................................................................................... 31

4.2Bus PC ............................................................................................................................................. 31

4.3Bus ISA (16 bit) .............................................................................................................................. 32

4.4Bus PCI ........................................................................................................................................... 32

4.5Ghép n i qua khe c m m r ngố ắ ở ộ .................................................................................................... 33

4.5.1.M t s đ c đi m c a Card ISAộ ố ặ ể ủ ............................................................................................ 33

4.5.2.Gi i mã đ a ch và k t n i Bus d li uả ị ỉ ế ố ữ ệ ................................................................................. 33

5.1Kh i ghép n i song song đ n gi nố ố ơ ả ................................................................................................ 35

5.2Các vi m ch đ m, ch t (74LS245, 74LS373)ạ ệ ố ............................................................................... 36

1

5.2.1.Vi m ch đ m 74LS245:ạ ệ ......................................................................................................... 36

5.2.2.Vi m ch ch t 74LS373:ạ ố ......................................................................................................... 36

5.3Vi m ch PPI 8255Aạ ........................................................................................................................ 37

5.3.1.Gi i thi u chungớ ệ ..................................................................................................................... 37

5.3.2.Các l nh ghi và đ c các c ng và các thanh ghi đi u khi nệ ọ ổ ề ể .................................................. 38

5.3.3.Các t đi u khi nừ ề ể ................................................................................................................... 38

5.3.4.Ghép n i 8255A v i MVT và TBNố ớ ........................................................................................ 42

5.4Ghép n i song song qua c ng máy inố ổ ............................................................................................ 46

5.4.1.Gh i thi u chungớ ệ .................................................................................................................... 46

5.4.2.C u trúc c ng máy inấ ổ ............................................................................................................. 47

5.4.3.Các thanh ghi c a c ng máy in:ủ ổ ............................................................................................. 49

5.4.4.EPP - Enhanced Parallel Port .................................................................................................. 51

6.1Đ t v n đặ ấ ề ..................................................................................................................................... 57

6.2Yêu c u và th t c trao đ i tin n i ti p:ầ ủ ụ ổ ố ế ....................................................................................... 57

6.2.1.Yêu c u: ầ ................................................................................................................................. 57

6.2.2.Trao đ i tin đ ng b : Synchronousổ ồ ộ ........................................................................................ 58

6.2.3.Trao đ i tin không đ ng b - Asynchronous:ổ ồ ộ ........................................................................ 58

6.3Truyên thông nôi tiêp s dung giao diên RS-232: ! ! ư" # # .......................................................................... 59

6.3.1.Qua trinh truyên môt byte d liêu:! # ư$ # .......................................................................................... 59

6.3.2.Công nôi tiêp RS 232" ! ! .............................................................................................................. 60

Tài li u tham kh o:ệ ả ......................................................................................................... 77

2

Bài m đ uở ầ

3

Ch ng 1: Đ i c ng v k thu t ghép n i máy tínhươ ạ ươ ề ỹ ậ ố

Ch ng 1ươ Đ i c ng v k thu t ghép n i máy tínhạ ươ ề ỹ ậ ố

1.1 Yêu c u trao đ i tin c a máy vi tính đ i v i môi tr ng bên ngoàiầ ổ ủ ố ớ ườ

1.1.1. Yêu c u trao đ i tin v i ng i đi u hànhầ ổ ớ ườ ề

Ng i đi u hành (ng i s d ng) máy vi tính (MVT) c n đ a l nh (d i d ng ch ) và sườ ề ườ ử ụ ầ ư ệ ướ ạ ữ ố

li u thông qua bàn phím. Khi ng i đi u hành b m vào các phím c a bàn phím nh ng mãệ ườ ề ấ ủ ữ

đ c t o ra và đ c truy n vào b nh c a MVT và đ ng th i hi n th lên màn hình các chượ ạ ượ ề ộ ớ ủ ồ ờ ể ị ữ

và con s đã b m. ố ấ

1.1.2. Yêu c u trao đ i tin v i thi t b ngoài thông d ngầ ổ ớ ế ị ụ

Các thi t b đ a tin vàoế ị ư

Các thi t b đ a tin raế ị ư

Các b nh ngoàiộ ớ

Yêu c u trao đ i tin v i thi t b ngoài khácầ ổ ớ ế ị

Trong h đo v t lý, MVT c n nh n các tin v t lý( nhi t đ , áp xu t, l c, dòng đi n, vv )ệ ậ ầ ậ ậ ệ ộ ấ ự ệ

d i d ng tín hi u đi n thông qua d u dò b phát hi n (detector ), c m bi n (sensor ), bướ ạ ệ ệ ầ ộ ệ ả ế ộ

chuy n đ i (tranducer ). H n n a MVT còn nh n các tin v tr ng thái s n sàng hay b n c aể ổ ơ ữ ậ ề ạ ẵ ậ ủ

các thi t b đo.ế ị

Trong h đo - đi u khi n, MVT c n:ệ ề ể ầ

Nh n tin v s li u đo, v tr ng thái thi t b đoậ ề ố ệ ề ạ ế ị

Đ a tin v s ch p nh n trao đ i tin v i thi t b ngoài, v l nh đi u khi n các c c uư ề ự ấ ậ ổ ớ ế ị ề ệ ề ể ơ ấ

ch p hành (Các đ ng c servo, các van đóng m , các thi t b đóng ng t m ch đi n, vv )ấ ộ ơ ở ế ị ắ ạ ệ

và các thông s k thu t cho thi t b .ố ỹ ậ ế ị

Trong các h l u tr và bi u di n tin, MVT c n đ a tin ra đ :ệ ư ữ ể ễ ầ ư ể

L u tr trên băng t , đĩa t , băng gi y và đĩa compacư ữ ừ ừ ấ

Bi u di n k t qu đo d i d ng b ng s li u, d ng đ th trên gi y c a máy v hayể ễ ế ả ướ ạ ả ố ệ ạ ồ ị ấ ủ ẽ

trên màn hình c a thi t b đ u cu i.ủ ế ị ầ ố

1.1.3. Yêu c u trao đ i tin trong m ng máy tínhầ ổ ạ

M t máy tính trong m ng c n trao đ i tin v i nhi u ng i s d ng m ng, v i nhi u máyộ ạ ầ ổ ớ ề ườ ử ụ ạ ớ ề

vi tính khác, v i nhi u thi t b ngoài nh : các thi t b đ u cu i, các thi t b nh ngoài, cácớ ề ế ị ư ế ị ầ ố ế ị ớ

thi t b l u tr và bi u di n tin.ế ị ư ữ ể ễ

1.2 D ng và các lo i tin trao đ i gi a máy vi tính và thi t b ngoài (TBN)ạ ạ ổ ữ ế ị

1.2.1. D ng tin (s )ạ ố

4

Ch ng 1: Đ i c ng v k thu t ghép n i máy tínhươ ạ ươ ề ỹ ậ ố

MVT ch trao đ i tin d i d ng s v i các m c logic 0 và 1ỉ ổ ướ ạ ố ớ ứ

Thi t b ngoài l i trao đ i tin v i nhi u d ng khác nhau nh d ng s , d ng ký t , d ng t ng t ,ế ị ạ ổ ớ ề ạ ư ạ ố ạ ự ạ ươ ự

d ng âm t n hình sin tu n hoànạ ầ ầ

1.2.2. Các lo i tinạ

•MVT đ a ra thi t b ngoài m t trong 3 lo i tin:ư ế ị ộ ạ

Tin v đ a ch : Đó là các tin c a đ a ch TBN hay chính xác h n, là đ a ch thanh ghiề ị ỉ ủ ị ỉ ơ ị ỉ

đ m c a kh i ghép n i đ i di n cho TBNệ ủ ố ố ạ ệ

Tin v l nh đi u khi n: Đó là các tín hi u đ đi u khi n kh i ghép n i hay TBN nhề ệ ề ể ệ ể ề ể ố ố ư

đóng m thi t b , đ c ho c ghi m t thanh ghi, cho phép hay tr l i yêu c u hành đ ng,ở ế ị ọ ặ ộ ả ờ ầ ộ

vv

Tin v s li u: Đó là các s li u c n đ a ra cho thi t b ngoàiề ố ệ ố ệ ầ ư ế ị

•Máy tính nh n tin vào t TBN v m t trong hai lo i tin:ậ ừ ề ộ ạ

Tin v tr ng thái c a TBN: Đó là tin v s s n sàng hay yêu c u trao đ i tin, v tr ngề ạ ủ ề ự ẵ ầ ổ ề ạ

thái sai l i c a TBNỗ ủ

Tin v s li u: Đó là các s li u c n đ a vào MVTề ố ệ ố ệ ầ ư

1.3 Vai trò nhi m v và ch c năng c a kh i ghép n i (KGN)ệ ụ ứ ủ ố ố

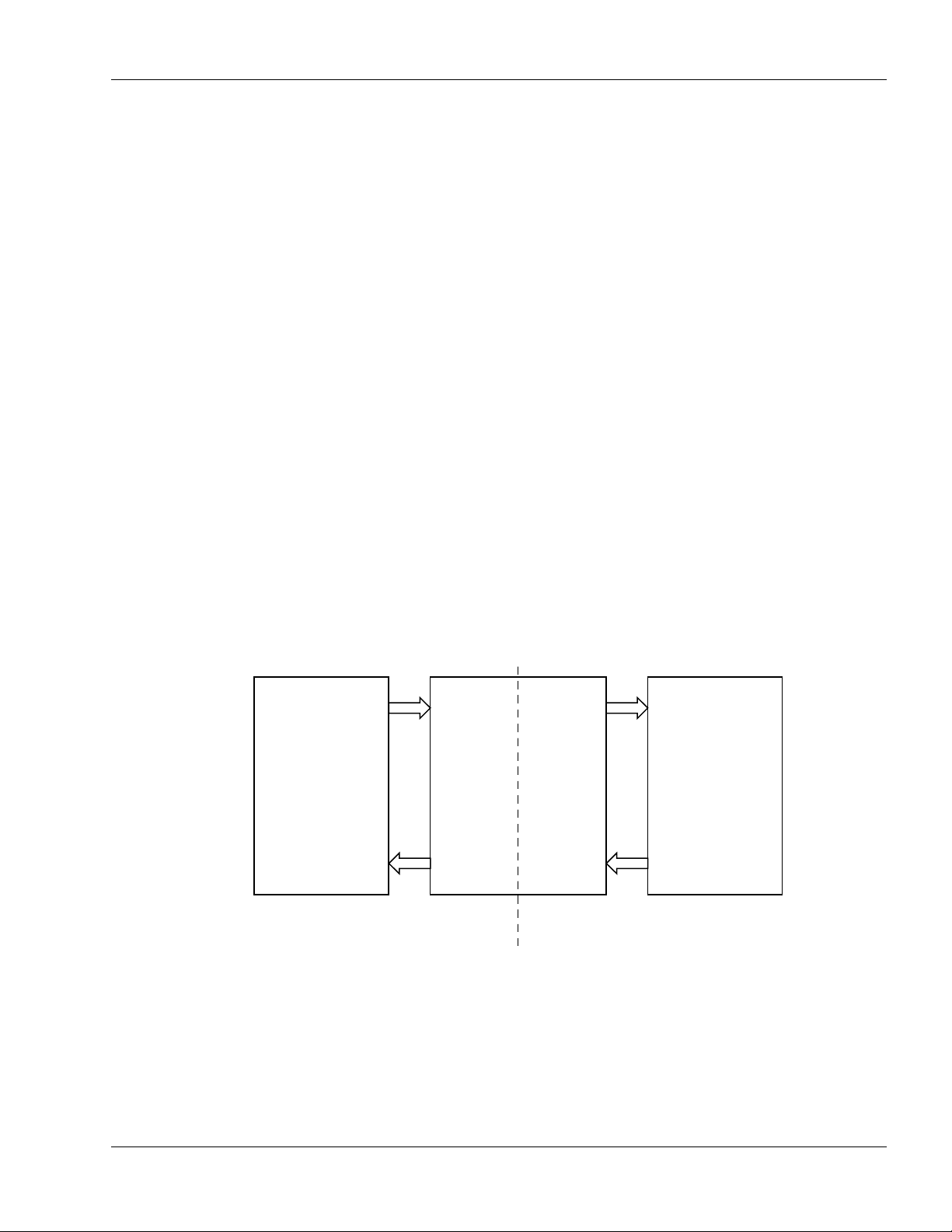

1.3.1. Vai trò

Kh i ghép n i n m gi a MVT và TBN đóng vai trò bi n đ i và trung chuy n tin gi aố ố ằ ữ ế ổ ể ữ

chúng

1.3.2. Nhi m vệ ụ

•Ph i h p v m c và công su t tín hi uố ợ ề ứ ấ ệ

- M c tín hi u c a MVT th ng là m c TTL (0V – 5V) trong khi TBN có nhi u m c khácứ ệ ủ ườ ứ ề ứ

nhau, thông th ng cao h n (± 15V, ± 48V)ườ ơ

Ngu n ồ

phát

MVT

Ngu n ồ

nh nậ

Ngu n ồ

nh nậ

TBN

Ngu n ồ

phát

Ngu n ồ

phát

Ngu n ồ

nh nậ

Ngu n ồ

nh nậ

Ngu n ồ

phát

Ghép n i đ ng ố ườ

dây MVT

Ghép n i đ ng ố ườ

dây TBN

V trí và vai trò c a kh i ghép n iị ủ ố ố

5