9/5/2011

1

Phần II:

Field Programmable Gate Array

Application Specific Integrated Circuit

• Tổng quan (1)

• Kiến trúc (2)

• Qui trình thiết kếFPGA, ASIC (1)

• Giới thiệu công cụthiết kếvà triển khai (4)

1/4

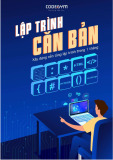

1980s, VLSI xuất hiệnthiết kếIC theo nhu cầu.

Độ phức

tạp tăng

40% mỗi

năm.

Nhu cầu

thiết kế

tăng 15%

mỗi nămMứcñộ tích hợp của PCB trên mỗi die

2/4

Silicon, 2010

29email ktmt@soict.hut.edu.vn

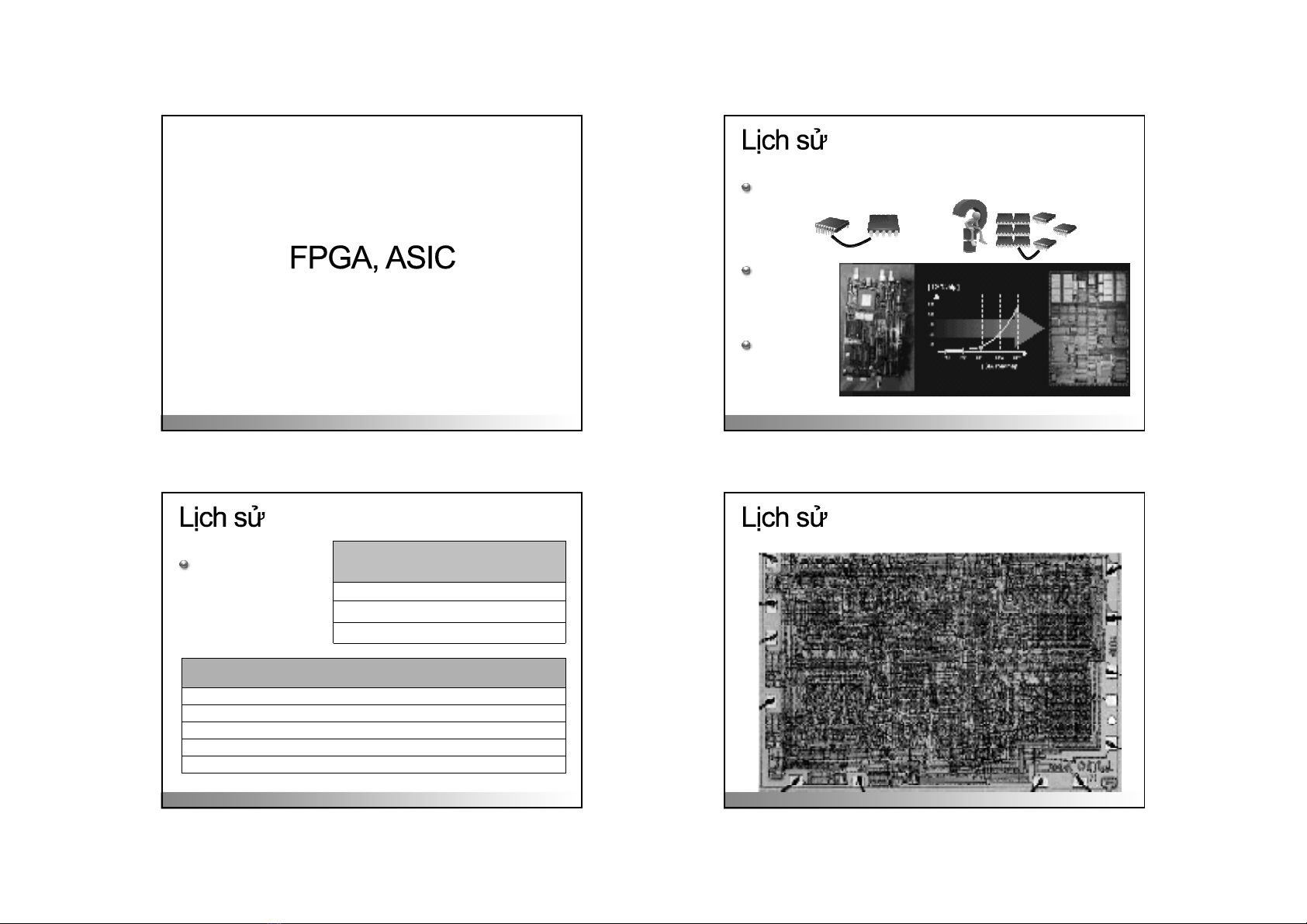

Mậtñộ

(Gb/cm2)

Tốcñộ truy

xuất (ns)

DRAM 8.5 10

DRAM (logic) 2.5 10

SRAM (cache) 0.3 1.5

Mậtñộ

(Mgate/cm2)

Năng lượng

(W/cm2)

Xung ñồng hồ

(GHz)

Custom 25 54 3

Std. Cell 10 27 1.5

Gate 5 18 1

Single-Mask GA 2.5 12.5 0.7

FPGA 0.3 4.5 0.25

Die Area: 2.5x2.5 cm

Voltage: 0.6 V

Technology:0.07 µm

3/4

30email ktmt@soict.hut.edu.vn

Intel 4004 (1971) - thiết kếthủcông

9/5/2011

2

4/4

ASIC ra ñời so nhu cầu vềcác hoạtñộng thiết kế

ngày càng tăng.

Hội nghịcác vi mạch tùy biến theo khách hàng

của IEEE ñưa ra các tài liệu hướng dẫn phát triển

custom IC.

Thiết kế= IC chuẩn + custom IC

Từcustom IC thuật ngữApplication Specific IC

31email ktmt@soict.hut.edu.vn

1/3

ASIC không ñồng nhất với custom IC.

IC chuẩn: ROM, RAM, DRAM, Processor, etc.

ASIC: chip cho ñồ chơi biết nói, chip cho 1 vệtinh, chip

cho bộxửlý dưới dạng cell cùng với mạch logic.

Qui tắc phổbiến: “Nếu một IC xuất hiện trong

sách tra cứu, thì ñó không phải là ASIC”.

ASIC, IC chuyên dụng.

Application Specific Standard Product.

1/2

ASIC ñem lại cơhội sản xuất với sốlượng lớn;

các bộphậnñược tiêu chuẩn hóa ñể nhanh chóng

trởthành sản phẩm thương mại.

Giá thành giảm theo sốlượng.

None Reducing Cost.

Quy trình Cost Down trong các nhà máy.

Hiệu quảkinh tếtrong thiết kế

Thực hiện prototype nhanh với sốlượng thấp.

Thiết kếtheo nhu cầu, chuyên sâu, sốlượng lớn.

33email ktmt@soict.hut.edu.vn

2/2

Có công cụCAD cần thiếtñể ñạtñược hiệu quả

trong chiến lược thiết kế:

Thiết kếmức hệthống: VHDL

Thiết kếmức vật lý, từVHDL tới silicon, timing closure

(Monterey, Magma, Synopsys, Cadence, Avant!)

Chiến lược thiết kế: Hierarchy - phân cấp;

Regularity; Modularity - mô ñun; Locality.

34email ktmt@soict.hut.edu.vn

9/5/2011

3

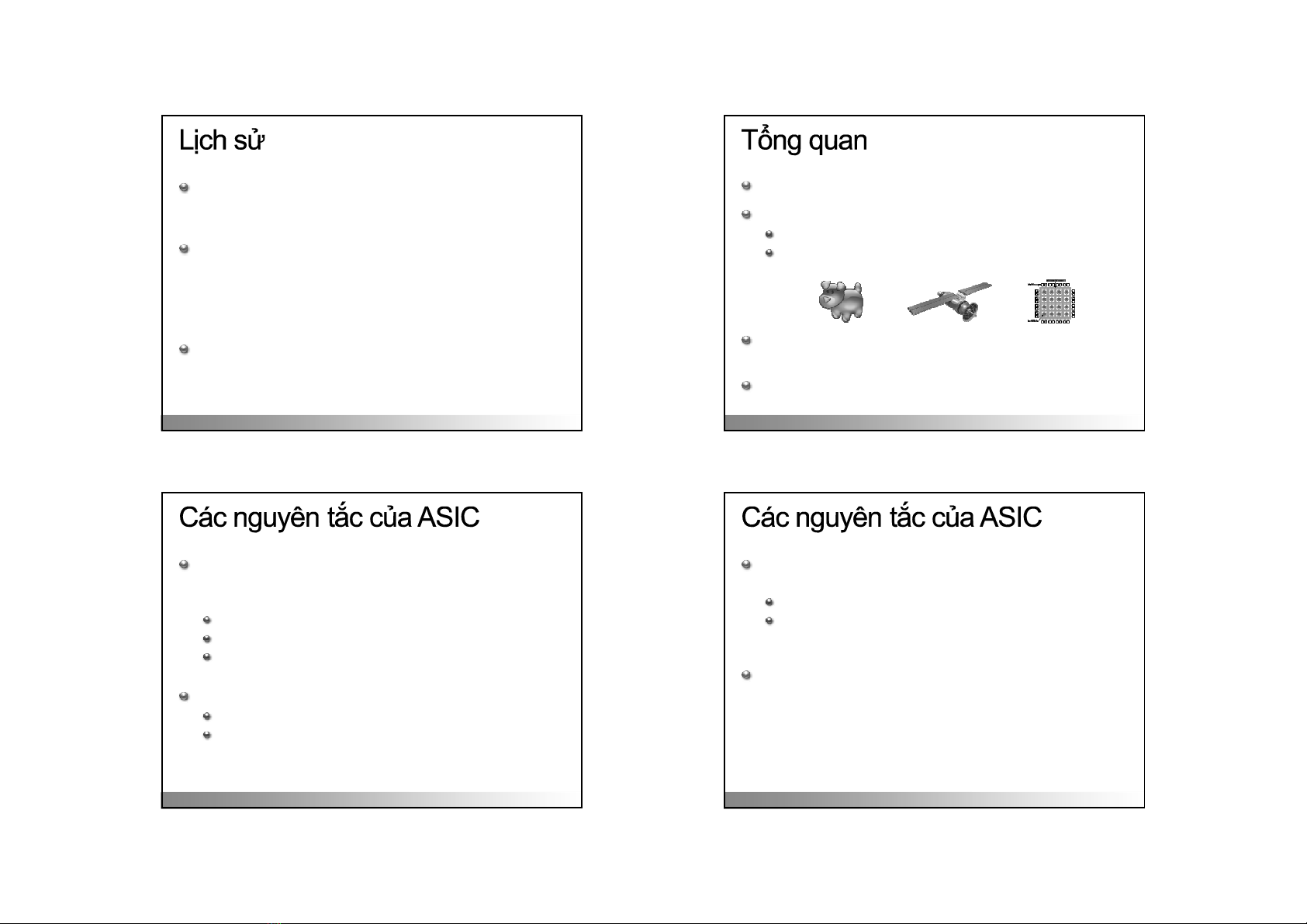

Thiết kếlà một quá trình liên tục cân ñối các tham

số ñầu vào, ñể ñạtñược hiệu quảmong ñợi.

35email ktmt@soict.hut.edu.vn

• chức năng, thời gian, tốcñộ, năng lượng

Hiệu năngHiệu năng

• chi phí sản xuất

Kích thước dieKích thước die

• lập lịch và chi phí nghiên cứu

Thời gian thiết kếThời gian thiết kế

• lập lịch, chi phí nguồn lực, chi phí sản xuất

Test và Stability TestTest và Stability Test

36email ktmt@soict.hut.edu.vn

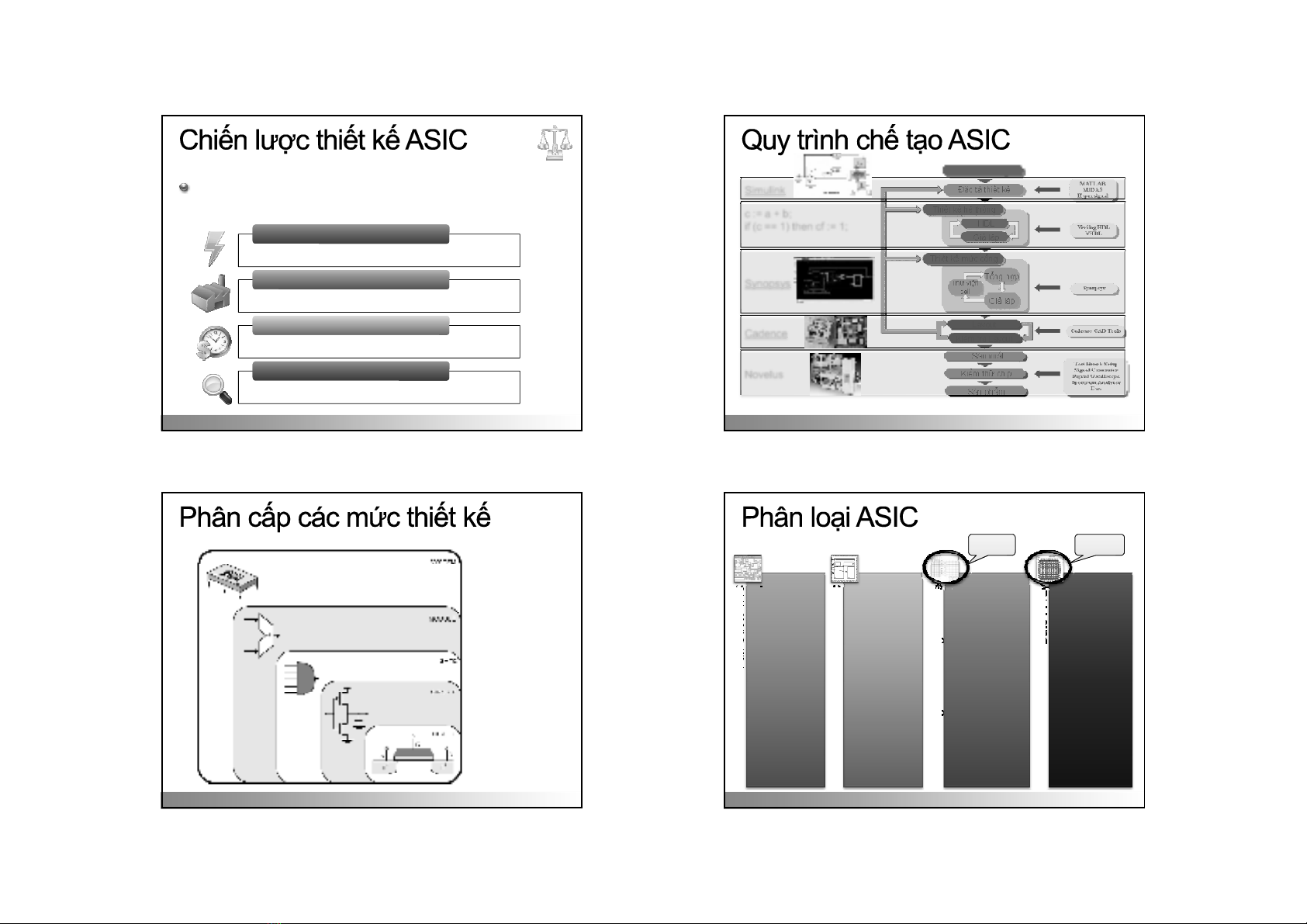

Ý tưởng thiết kế

Đặc tảthiết kế

Thiết kếhệthống

HDL

Giảlập

Thiết kếmức cổng

Tổng hợp

Giảlập

Thưviện

cell

Layout

Kiểm tra Layout

Sản xuất

Kiểm thửchip

Sản phẩm

c := a + b;c := a + b;

if (c == 1) then if (c == 1) then cfcf := 1;:= 1;

SimulinkSimulink

SynopsysSynopsys

CadenceCadence

NovelusNovelus

37email ktmt@soict.hut.edu.vn

Mức thiết bị

Mức mạch

Mức cổng

Mức mô-ñun

chức năng

Mức hệthống

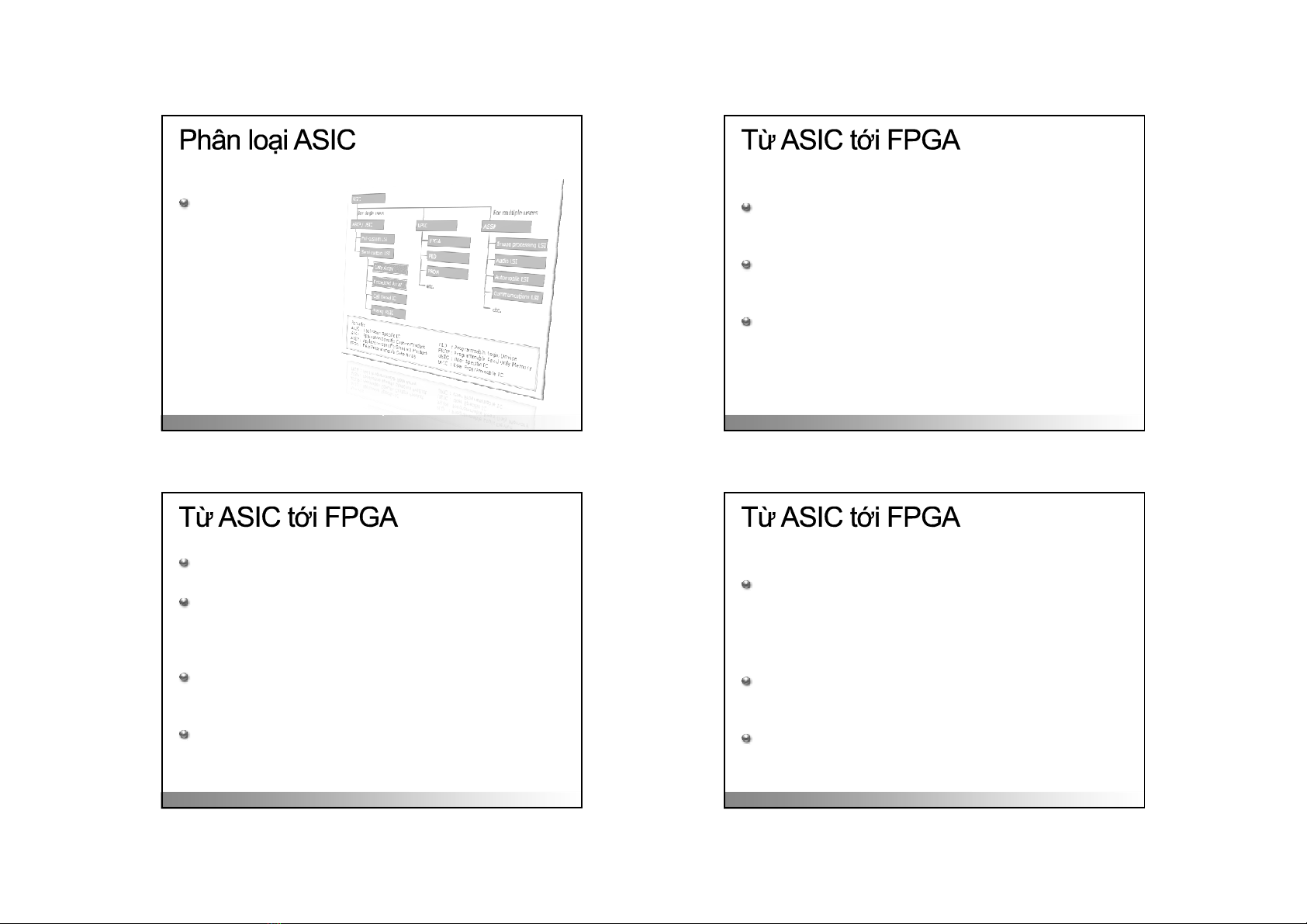

1/2

38email ktmt@soict.hut.edu.vn

Full Custom IC

• Thiết kếrất

phức

tạp, hàng

trăm man-

year

• ~ 25M gate

• Phải sản

xuất với số

lượng cực

lớn mới

Cell Base IC

• Các cell là

Flip-

Flop, gate,

hoặc bộxử

lý ñãñược

ñịnh nghĩa

trước, ñược

tái sửdụng

lại,

• Sản xuất

với số

lượng 100k

sản phẩm/

năm

Programable Logic Device

• Dựa trên

công nghệ

ROM/PROM,

cấu tạo chỉ

gồm các lớp

cổng

AND, OR và

một sốFlip

Flop.

• Sản phẩm

khá ñơn giản

với khoảng

1K gate.

• Sản xuấtñơn

lẻ ñược

Gate Array

• Các trans tạo

sẵn thảnh

mảng, và

nhà thiết kế

thực hiện

việc tạo các

liên kết nối

giữa chúng

bằng cách

sửdụng các

thưviện cell

và CAD.

• Sản xuấtñơn

lẻ ñược.

FPGAFPGACPLDCPLD

9/5/2011

4

2/2

39email ktmt@soict.hut.edu.vn

FPGA, PLD,

CPLD ñược

xếp vào nhóm

các IC lập trình

ñược bởi

người dùng

1/4

40email ktmt@soict.hut.edu.vn

Phát sinh thứ1:

Một khi chip ASIC càng mạnh thì thiết kếcàng

tinh vi, phức tạp, càng tiềm tàng những sai sót

lớn.

Các phần mềm hỗtrợ, giảlập chưa thực sự

phản ánh hếtñược hoạtñộng thực tếcủa hệ

thống.

Để kiểm tra thiết kế, người kĩsưbuộc phảiñặt

các nhà sản xuất sản xuất chip ñơn lẻvà kiểm

tra trên các ứng dụng, môi trường thựctốn

thời gian, và tiền bạc.

cần hệnền kiểm thửphần cứng nhanh chóng.

2/4

41email ktmt@soict.hut.edu.vn

Năm 1984, Ross Freeman, Bernard

Vonderschmitt, ñồng sáng lập công ty Xillinx.

Năm 1985, Xilinx ñưa ra dòng FPGA thương mại

ñầu tiên, XC2064. Năm 2006, Freeman ñược

vinh danh tại National Inventors Hall of Fame vì

sáng chếnày.

FPGA dựa trên các công nghệnền tảng như

PROM và PLD, nhưng với kiến trúc mới hiệu

quảhơn.

Các thiết kếIC ñược thửnghiệm prototype trên

các chip FPGA ngay lập tứctiết kiệm thời

gian và tiền bạc.

3/4

42email ktmt@soict.hut.edu.vn

Phát sinh thứ2:

Các nhà sản xuất lớn chỉcung cấp các chip

thông dụng trên thịtrường, với sốlượng lớn.

bỏqua nhu cầu vềcác IC chuyên dụng có số

lượng thấp, nhưng tổng nhu cầu thì rất lớn.

Phát sinh thứ3:

Ban ñầu, các chip lập trình ñược có giá thành

khá cao và tốcñộ chậm, chỉsửdụng trong các

phòng thí nghiệm.

Khi công nghệsản xuất phát triển vượt bậc, thì

các chip lập trình ñược ngày càng mạnh và rẻ

ứng dụng ñại trà.

9/5/2011

5

4/4

43email ktmt@soict.hut.edu.vn

Hệquả: Chân trời mới

FPGA không chỉlà chip prototype trong các

phòng thí nghiệm, mà thực sựtrởthành sản

phẩm thường mạiñại chúng.

Thịtrường phần cứng ñược cung cấp một dòng

sản phẩm có thểthiết kếvà sửdụng ñược ngay.

Các công ty vừa nhỏ, các kỹsưhoạtñộng ñộc

lập, không phải lệthuộc vào các IC của các nhà

sản xuất lớntựdo sáng tạo.

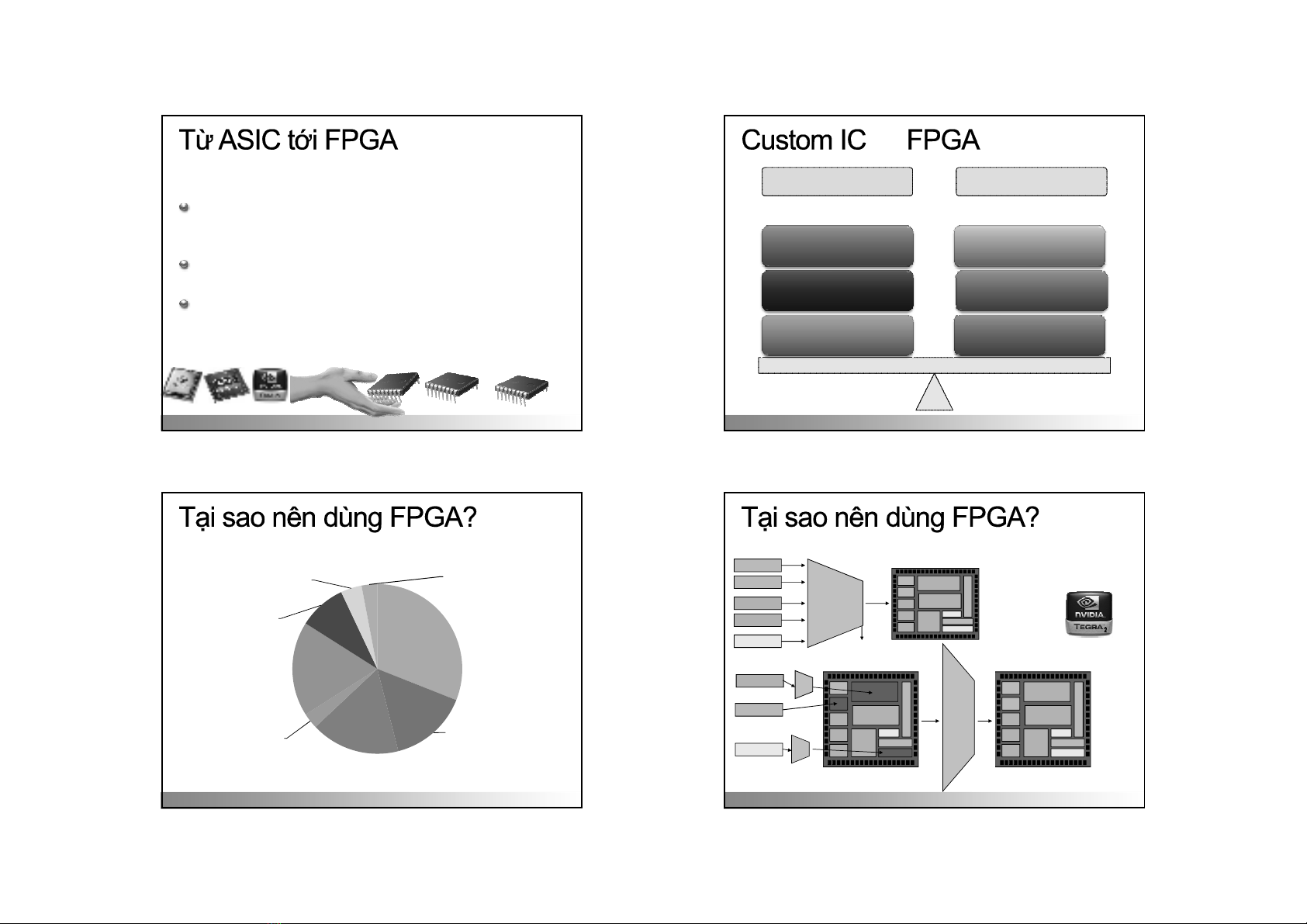

vsvs

44email ktmt@soict.hut.edu.vn

CustomICCustomIC FPGAFPGA

Sản xuất nhỏ

Tốiưu tính năng

Chi phí chếtạo thấp

Sản xuất lớn

Tốiưu tốcñộ, năng

lượng…

Chi phí chếtạo lớn

1/2

45email ktmt@soict.hut.edu.vn

Flexibility &

Expandability

31%

Best

Performance

(thoughput

speed)

15%

Lowest Cost

17%

Lowest

Power

3%

Complete

Solution

18%

Quality,

Reliability

9%

Easiest to

use

4%

Other

3%

Nguyên nhân sử dụng chip ASIC prototyping

1/2

46email ktmt@soict.hut.edu.vn

Hard IP

Hard IP

Soft IP

Soft IP

Others

... ...

EDA

Tools

System On Chip IP-based

Platform-based

EDA

Integrator

Application specific integration platform

EDA

Tools

Derivative

Hard IP

Others

Soft IP EDA

Tools

![Giáo trình Thiết kế logo căn bản (Ngành Thiết kế đồ họa Trung cấp) - Trường Cao đẳng Xây dựng số 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2024/20240624/gaupanda039/135x160/3561719229819.jpg)

![Giáo trình Design thị giác (Thiết kế đồ họa Trung cấp) - Trường Cao đẳng Xây dựng số 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2024/20240624/gaupanda039/135x160/7481719229857.jpg)

![Giáo trình AutoCAD Pro Design: Phần 2 - Dương Đức Cảnh [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1030337256.jpg)

![Giáo trình AutoCAD Pro Design: Phần 1 - Dương Đức Cảnh [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1724121258.jpg)

![Câu hỏi trắc nghiệm Lập trình C [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251012/quangle7706@gmail.com/135x160/91191760326106.jpg)