9/5/2011

1

49email ktmt@soict.hut.edu.vn

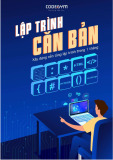

AB C Yêu cầu: F = AB = ABC + ABC

PAL thương mại

LậpLập

trìnhtrình

Programable

Array Logic (a)

Programable

ROM (b)

50email ktmt@soict.hut.edu.vn

Programable Logic Array, cảmatrận AND và OR

ñều lập trình ñược.

Tiết kiệm dung lượng ma trận.

Bịhạn chếbởi sốlượng các cổng AND khi số ñầu vào

của cổng OR lớn hơn sốcổng AND.

Trễtruyền lan lớn hơn và mậtñộ tích hợp nhỏ.

Generic Array Logic nâng

cấp từPAL, gồm một ma

trận AND lập trình ñược

(cấu tạo từEEPROM) và

ma trận OR cố ñịnh.

Tuy nhiên, các cổng OR

nằm trong các macrocell

ñược nối với flip-flop và các

bộdồn kênh ñể có thểchọn

tín hiệu ra.

Tên gọi chung của các thiết

bịnhưPAL, PLA, GAL… là

Programable Logic Device

51email ktmt@soict.hut.edu.vn

Ví dụ: Dùng GAL ñiều khiển

ñèn giao thông:

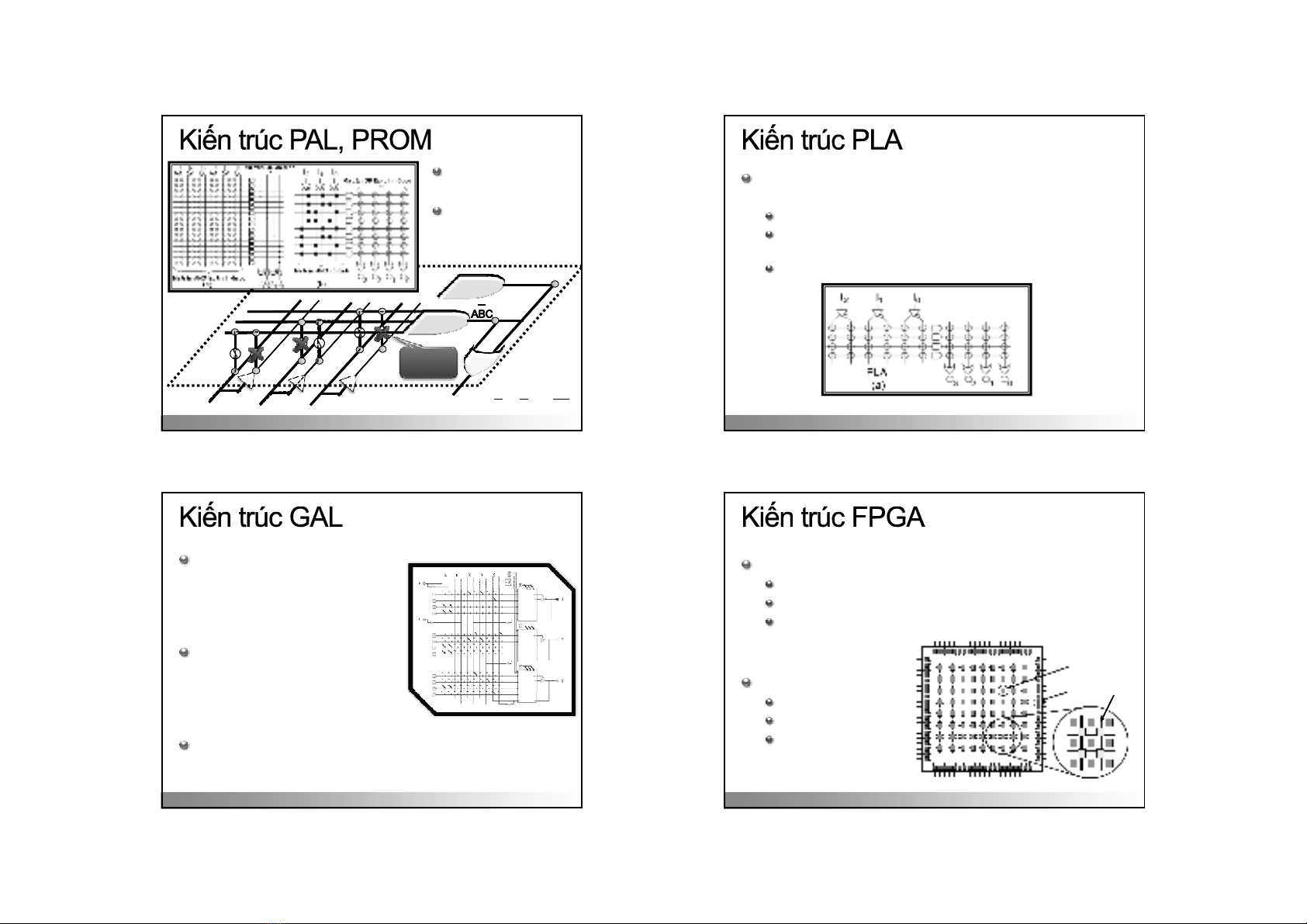

FPGA gồm 3 thành phần chính

Khối logic – Logic Block (LB): ñơn vịxửlý.

Khối Vào ra – IO cell: giao tiếp với bên ngoài.

Liên kết nối – Interconnection: liên kết các ñơn vịxửlý.

Thành phần khác

Buffer

ClockDll

…

52email ktmt@soict.hut.edu.vn

Configurable

Logic Block

I/O Block Connec

t

Connect

9/5/2011

2

1/3

Cả3 thành phần: khối logic, khối vào ra, liên kết

nối, ñều lập trình ñược.

Lập trình cho khối logic là hành ñộng: “có kết nối

hay không phần tửlogic A với phần tửlogic B?”

Lập trình cho khối vào ra là hành ñộng: “có kết nối

hay không ñầu ra logic A với chuẩn ngoại vi B?”

Lập trình cho liên kết nối là hành ñộng: “có kết nối

hay không khối logic A với khối logic/vào ra B?”

53email ktmt@soict.hut.edu.vn

2/3

Với FPGA, lập trình là quá trình ñịnh tuyếngiữa

các phần tửlogic, flipflop… ñãñược chếtạo cố

ñịnh sẵn, ñể thực thi một tác vụnào ñó.

Một tuyếnñềuñược chếtạo sẵn, và ñính kèm một

khóa ñóng mở. Tuyếnñược thiết lập hoặc

hủy, tương ứng với trạng thái khóa ñóng hay mở.

Mỗi trạng thái của khóa ñóng/mở ứng với một bit

nhớtrạng thái 0/1 tương ứng.

Tập hợp các bít nhớtạo thành bộnhớcấu hình

cho FPGA.

Bảng ñịnh tuyếnñược lưu trữtrong bộnhớ.

Công cụCAD sẽdịch HDL thành bảng ñịnh tuyến.

3/3

55email ktmt@soict.hut.edu.vn

BộBộnhớnhớcấucấu hìnhhình

HDL

• c := a + b;

• if (c == 1) then cf := 1;

RTL

•

BIT file

• 01000100

• 11010101

• 10001001

Phân tích

Ánh xạvào

FPGA cụthểTất cảASIC lập trình ñược, bao gồm FPGA, ñều

chứa các khối logic (cell logic) cơbản giống nhau

tạo thành dải.

56email ktmt@soict.hut.edu.vn

LB

LB

LB

LB

LB

LB

LB

LB

LB

LB

Cell

I/O

Cell

Cell

I/O

Cell

Cell

I/O

Cell

Cell

I/O

Cell

Cell

I/O

Cell

Cell

I/O

Cell

I/

ell

I/O Cell

I/

ell

I/O Cell

I/

ell

I/O Cell

I/

ell

I/O Cell

I/

ell

I/O Cell

I/

ell

I/O Cell

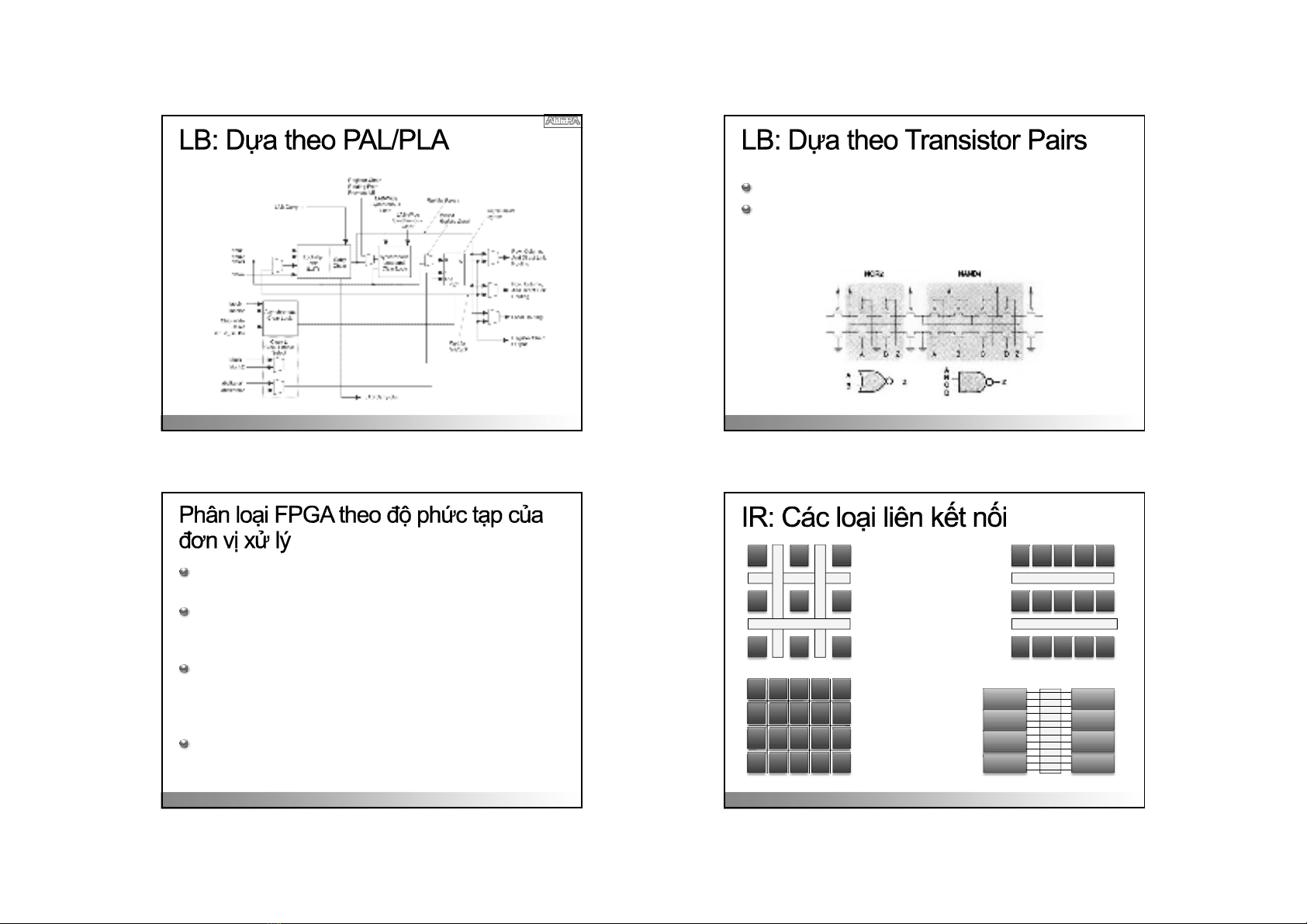

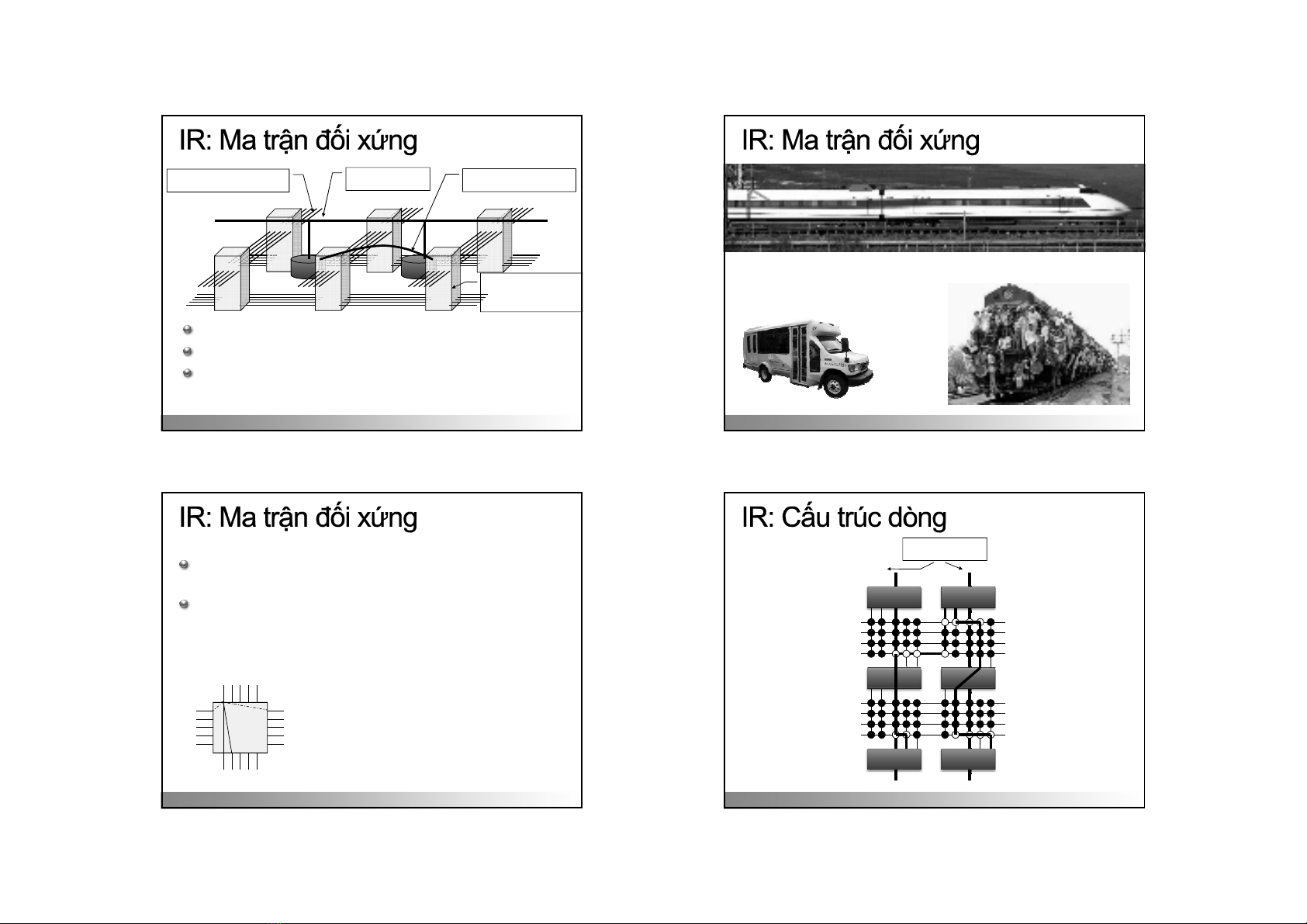

Có 4 loại khối logic:

Dựa vào bảng tìm kiếm

(LUT – Lookup Table) Xilinx

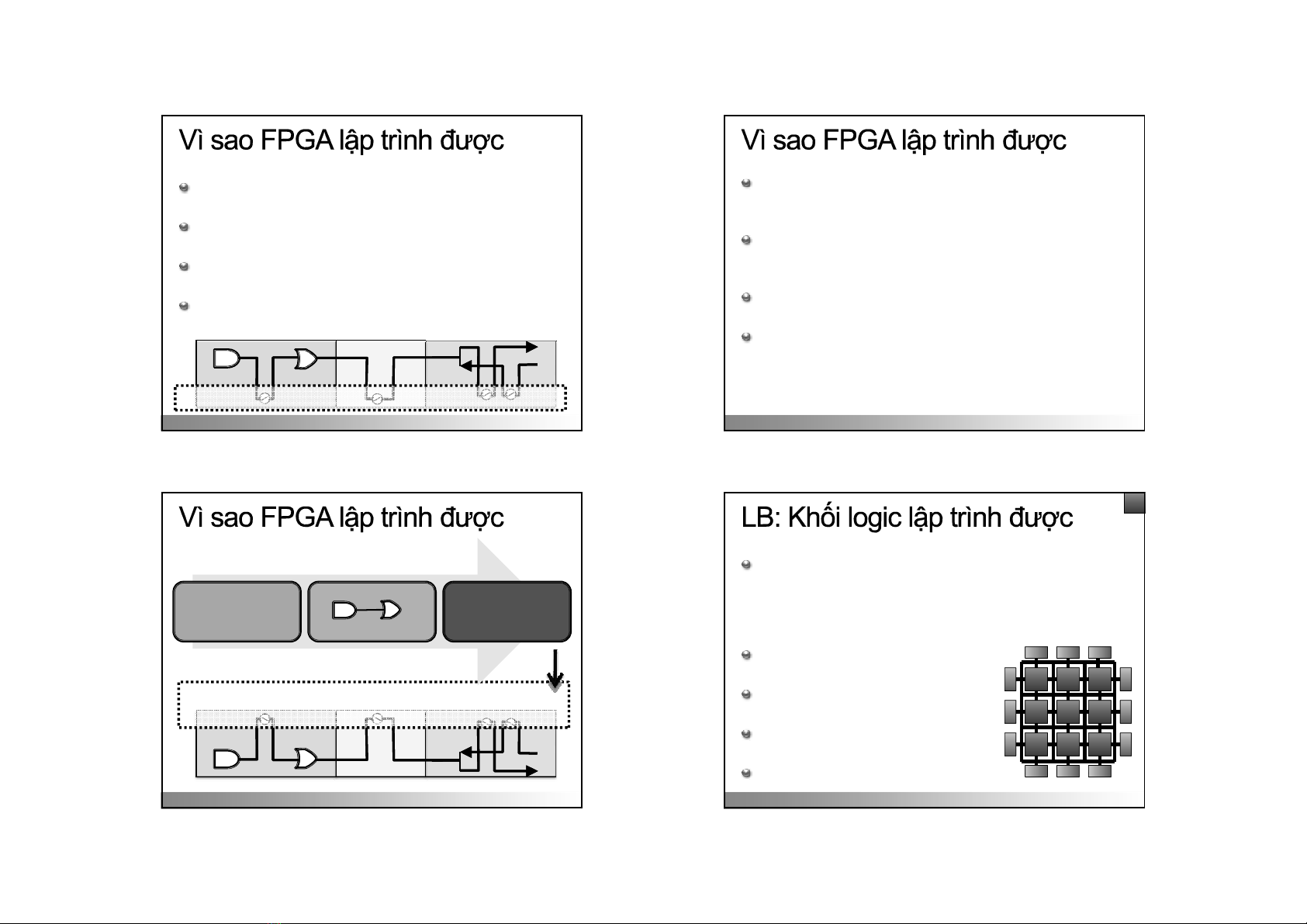

Dựa vào bộghép kênh

(Multiplexers) Actel

Dựa vào PAL/PLA

Altera

Transistor Pairs

9/5/2011

3

57email ktmt@soict.hut.edu.vn

Mux 2x1 có thể

thực hiệnñược

các hàm bên

S

0

1

MUX

A0

A1

SA

Biểu diễn

mức

transistor

Cấu trúc cell logic ACT 1 (ñơn module)

Cell ACT 1 chỉcó

một module logic.

Cell ACT 2, 3 có

nhiều module

logic hơn và có

Flip Flop riêng.

Cấu tạo Flip Flop

1/3

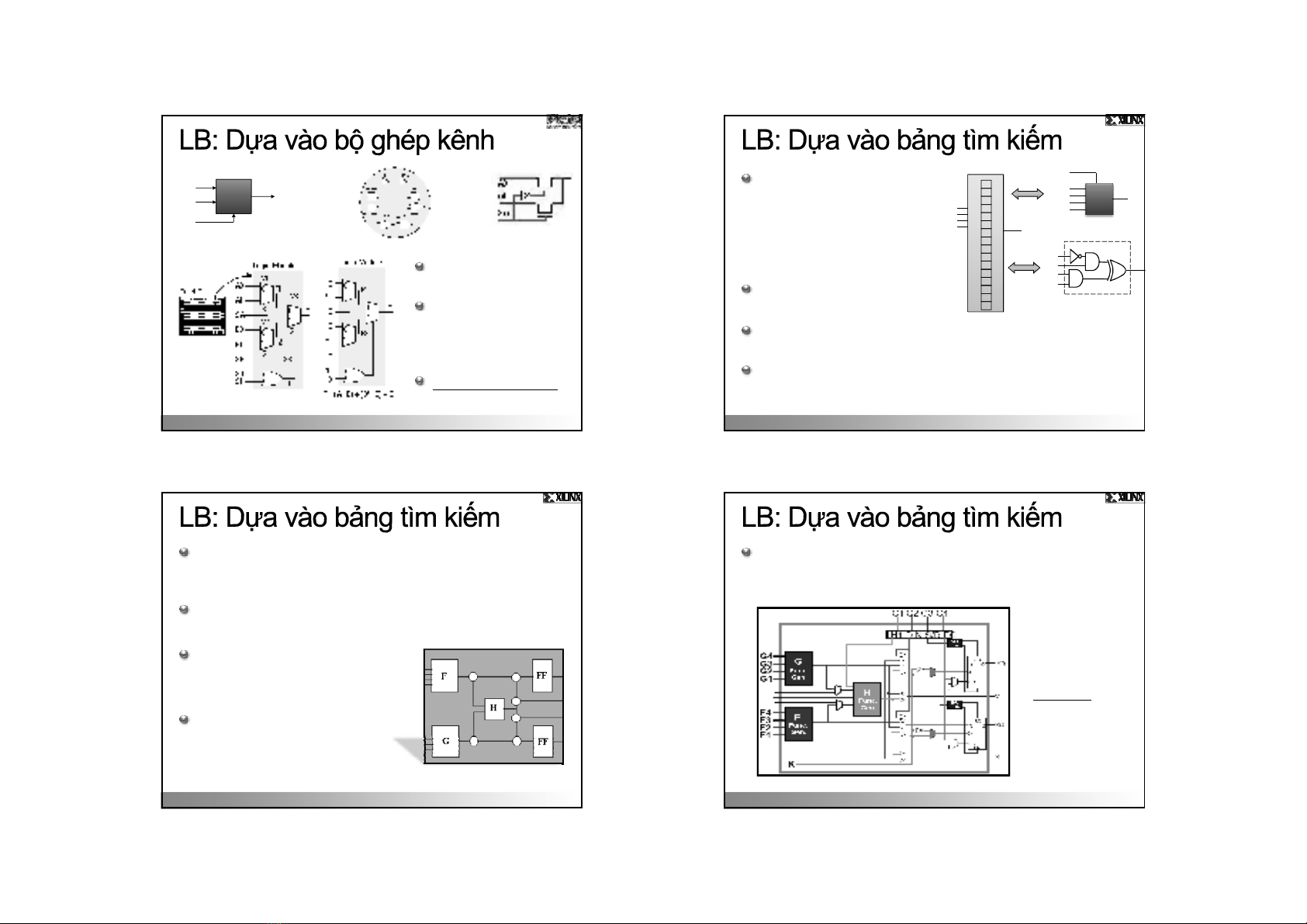

Bảng tìm kiếm, LUT,

Look-Up Table, là một

SRAM có K ñầu vào với

2Kbit nhớ, thực hiện

ñược mọi hàm logic có

K biến.

Thông thường, K = 4.

58email ktmt@soict.hut.edu.vn

G3 GG

FuncFunc..

Gen.Gen.

WE

G4

G2

G1

0

10

11

12

13

14

15

4

5

6

7

8

9

3

2

10

0

0

1

1

1

1

1

0

0

1

0

0

0

0

1

G4

G3

G2

G1 1

RAM 16bit

G3

G4

G2

G1

Tín hiệu ra của một LUT có thểquay trởlại, thành

ñầu vào của chính LUT ñó, hoặc LUT khác.

Trong một LB, thường có 3 LUT và ñược gọi là bộ

thực hiện hàm F, G và H.

2/3

Các LUT F và G tương ñương và ñộc lập với

nhau, thực thi các hàm 4 biến và ñưa kết quảtính

toán ra ngoài CLB, hoặc nhớvào FF.

Nếu phép toán có nhiều hơn 4 biến thì LUT F, G

sẽ ñưa kết quảtới LUT H ñể mởrộng thêm.

59email ktmt@soict.hut.edu.vn

Flip-Flop ñóng vai trò:

• Bit nhớhoặc

• Chốt dữliệu

Hai FF có thểset/reset ñồng

bộ/không ñồng bộ, tích cực

theo sườn âm/dương…

Cấu trúc cơbản của LB dạng LUT

3/3

60email ktmt@soict.hut.edu.vn

Khối logic lập trình

ñược, CLB, của

XC4000 E/X

Sốliệuñưa vào LB có thể ñược xửlý bởi các hàm

4 ñầu vào, có thể ñược chốtở thanh ghi, có thể

ñược chọn kênh, hoặc bởi cả3 thao tác trên.

9/5/2011

4

61email ktmt@soict.hut.edu.vn

LE(LB) của Altera Cyclone II

Còn ñược gọi là CrossPoint FPGA.

Sốlượng cổng ít, ~ 4000

62email ktmt@soict.hut.edu.vn

FPGA kếthừa nhiều ý tưởng thiết kếcủa các sản

phẩm trướcsựquen thuộc trong kiến trúc.

Nhưng sốchức năng, mứcñộ tích hợp, khảnăng

tính toán của từng ñơn vịxửlý trong FPGA có

khác nhau, gồm Coarse /kɔ:s/ , và Fine.

Coarse-grained: Đơn vịxửlý là một tập hợp của

các PLD, các khối cấu hình ñược CLB, thực thi

ñược hàm phức tạp, có yêu cầu tính toán lớn. Ví

dụ: Actel Mux, Xilinx LUT.

Fine-grained: Đơn vịxửlý chỉgồm các khối cấu

hình ñược CLB nhỏ, thực thi các hàm logic ñơn

giản. Ví dụTransistor Pairs.

63email ktmt@soict.hut.edu.vn 64email ktmt@soict.hut.edu.vn

LB

LB LB

LB

LB

LB

LB LB LB

Ma trậnñối xứng

Symmetrical Array

LB

LB LB

LB

LB

LBLB

LB LB

LB

LB LB LBLB LB

Cấu trúc dòng

Row-based

Sea-of-Gates PLD

PLD

PLD

PLD

PLD

PLD

PLD

PLD

PLD phân cấp

Hierarchical

(CPLD)

9/5/2011

5

1/3

Liên kết nối dài, tín hiệu clk liên thông toàn bộdải.

Liên kết nối trực tiếp giữa 2 khối LB.

Liên kết nốiña năng gồm nhiều kết nối và các

chuyển mạch.

65email ktmt@soict.hut.edu.vn

LB

SM

LB

SM

Kết nốiña năng Kết nối trực tiếp

Kết nối dài

SM Ma trận

chuyển mạch

2/3

66email ktmt@soict.hut.edu.vn

Kết nối dài

Kết nối trực tiếp Kết nốiña năng

3/3

Phần lớn các kết nối tạo thành các lưới kết nối

theo hàng và theo cột.

Giao cắt giữa các kết nối theo hàng và theo cột sẽ

tập trung các ñiểm cần lập trình kết nối, tạo thành

ma trận chuyển mạch (Switching Matrix), nằm

phân tán trong FPGA.

67email ktmt@soict.hut.edu.vn

SM

68email ktmt@soict.hut.edu.vn

LB LB

LB LB

LBLB

Kết nối dài

![Giáo trình Thiết kế logo căn bản (Ngành Thiết kế đồ họa Trung cấp) - Trường Cao đẳng Xây dựng số 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2024/20240624/gaupanda039/135x160/3561719229819.jpg)

![Giáo trình Design thị giác (Thiết kế đồ họa Trung cấp) - Trường Cao đẳng Xây dựng số 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2024/20240624/gaupanda039/135x160/7481719229857.jpg)

![Giáo trình AutoCAD Pro Design: Phần 2 - Dương Đức Cảnh [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1030337256.jpg)

![Giáo trình AutoCAD Pro Design: Phần 1 - Dương Đức Cảnh [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2022/20221214/phuongnguyen0520/135x160/1724121258.jpg)

![Câu hỏi trắc nghiệm Lập trình C [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251012/quangle7706@gmail.com/135x160/91191760326106.jpg)