Thi t k logic s ế ế ố

(VLSI design)

B môn KT Xung, s , VXLộ ố

quangkien82@gmail.com

https://sites.google.com/site/bmvixuly/thiet-ke-logic-so

08/2012

Ch ng ươ

I

•Các ki n th c chung (nh c l i t Đi n T S )ế ứ ắ ạ ừ ệ ử ố

•HDL & Automation Design

•IC kh trìnhả

Ch ng ươ

II

•Ngôn ng VHDLữ

•K năng TK: ỹCác kh i MSI, SSI đn gi n đã bi t trong ĐTS: c ng, d ch, thanh ghi, đm ố ơ ả ế ộ ị ế

FSM…

Ch ng ươ

III

•Các thu t toán và s đ đ thi t k m t s kh i LSI thông d ngậ ơ ồ ể ế ế ộ ố ố ụ

•K năng TK: ỹCác kh i LSI, VLSI: CLA, nhân, chia s nguyên, s th c, có d u và không d u, ố ố ố ự ấ ấ

Memory, c u trúc CPU đn gi n.ấ ơ ả

•Bài t p l n môn h cậ ớ ọ

Ch ng ươ

IV

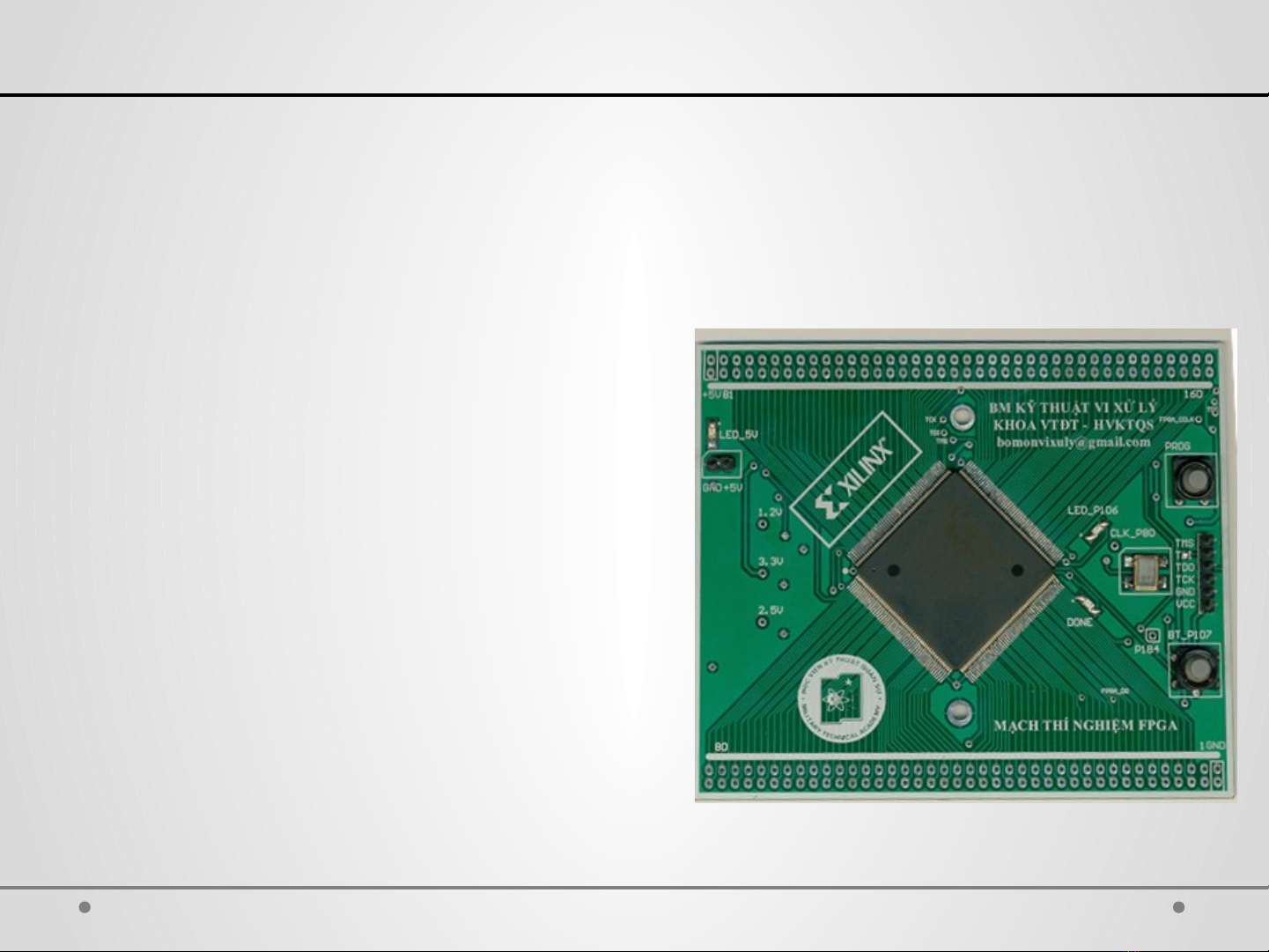

•Công ngh FPGAệ

•Thi t k FPGA trên Xilinx ISEế ế

•K năng TK: ỹHi n th c hóa thi t k các ch ng tr oc trên FPGA, l p trình giao ti p b ng ệ ự ế ế ở ươ ứ ậ ế ằ

VHDL cho các ngo i v đn gi n : UART, PS/2, I2C, SPI, VGA/LCD.ạ ị ơ ả

2

N i dung môn h cộ ọ

2/26

Ch ng IV: Thi t k m ch s trên FPGA ươ ế ế ạ ố quangkien82@gmail.com

M c đích & n i dungụ ộ

•M c đíchụ

•Gi i thi u t ng quan v công ngh FPGA, so sánh FPGA v i các ớ ệ ổ ề ệ ớ

công ngh thi t k và x lý ng d ng cho các bài toán s . Ki n ệ ế ế ử ứ ụ ố ế

trúc t ng quan và Ki n trúc Xilinx FPGA, ổ ế n m đc nguyên lý ắ ượ

làm vi c c a FPGA.ệ ủ

•N i dungộ

•Khái ni m FPGAệ

•Ki n trúc t ng quan FPGAế ổ

•Công ngh tái c u trúc FPGA (SRAM-based)ệ ấ

•So sánh FPGA v i CPLD, SPLD, ASIC, DSPớ

•Các ng d ng c a FPGAứ ụ ủ

•M t đ tích h p và kh năng tài nguyên c a FPGAậ ộ ợ ả ủ

•Ki n trúc c th c a Xilinx Spartan 3Eế ụ ể ủ

3/26

Ch ng IV: Thi t k m ch s trên FPGA ươ ế ế ạ ố quangkien82@gmail.com

Yêu c u chu n b & Tài li u tham kh oầ ẩ ị ệ ả

•Đc tr c TL[1], tr95-237: Ch ng IVọ ướ ươ

•Xem tr c slide bài gi ng s 4.1 t i đa ch : ướ ả ố ạ ị ỉ

https://sites.google.com/site/bmvixuly/thiet-ke-logic-so

•https://dl.dropbox.com/u/68634585/lecture/lecture4.1.pptx

•Đc thêm TL[7] tr 1-116ọ

•Cài đt ph n m m Xilinx ISE 12.4ặầề

•Chu n b bài th c hành s 1 trên FPGA t i ph l c 4 TL[1].ẩ ị ự ố ạ ụ ụ

•https://www.doc.ic.ac.uk/~wl/teachlocal/arch2/killasic.pdf

•http://www.deepchip.com/downloads/fpga-vs-asic.pdf

•http://www.xess.com/appnotes/fpga_tut.php

4/26

Ch ng IV: Thi t k m ch s trên FPGA ươ ế ế ạ ố quangkien82@gmail.com

Khái ni m FPGAệ

(Xilinx.com) Field-Programmable Gate Arrays (FPGAs) are semiconductor

devices that are based around a matrix of configurable logic blocks (CLBs)

connected via programmable interconnects. FPGAs can be reprogrammed to

desired application or functionality requirements after manufacturing.

5/26

Ch ng IV: Thi t k m ch s trên FPGA ươ ế ế ạ ố quangkien82@gmail.com

-công nghệ IC lập trình mới nhất và tiên

tiến nhất hiện nay.

- quá trình tái cấu trúc IC có thể được

thực hiện bởi người dùng cuối

-Công nghệ cho phép hiện thực hóa các

thiết kế số với chi phí và thời gian hợp lý

-Công nghệ đủ mạnh để đáp ứng đa số các

ứng dụng cơ bản, thay thế các chip ASIC

chuyên dụng

- Công nghệ cho phép mở ra các giải pháp

kỹ thuật mới cho các hệ xử lý truyền thống,

thay thế bằng các hệ có khả năng tái cấu

hình mềm dẻo.

![Bài giảng Nhập môn mạch số: Chương 3 (Phần 2) - TS. Trịnh Lê Huy [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/38491750824827.jpg)