BK

TP.HCM

2 0 0 8

dce

Tổng hợpluậnlývi mạch

2 0 1 0

dce Giớithiệu

•Mônhọc: Tổng hợpluậnlývi mạch

–Mãsố:

–Sốtín chỉ: 3

•Giảng viên:

– Dr. Tran Ngoc Thinh

• Email: tnthinh@cse.hcmut.edu.vn

• Phone: 8647256 (5843)

• Office: A3 building,

• Office hours: Tuesdays, 9:30-11:00

2

2 0 1 0

dce Giớithiệumônhọc

•Nội dung:

–Giớithiệuvềthiếtkếvi mạch

–Biếnđổitừcác đặctảngôn ngữHDL

–Nắm quy trình tổng hợp, kiểmtra, kiểmthửcác mạch 2

lớpvànhiềulớp

•Đốitượng:

– Sinh viên cao học

– Sinh viên đạihọcnăm3-4

•Đánh giá

–Tiểuluận: 30%

– Trình bày: 30%

–Kiểmtracuốikỳ: 40%

3

2 0 1 0

dce Nội dung môn học

•Tổng quan vềthiếtkếluậnlývi mạch

•Mạch tổhợp2 mức

•Tổng hợpmạch tổhợp2 mức

•Kiểmthửmạch tổhợp2 mức

•Mạch tổhợp nhiềumức

•Tổng hợpmạch tổhợp nhiềumức

•Kiểmthửmạch tổhợp nhiềumức

4

2 0 1 0

dce Tài liệu tham khảo

[1]. Logic Senthesis – Srinivas Devadas, Abhijit Ghosh, Kurt

Keutzer

[2]. Synthesis and Optimization of Digital Circuits –

Giovanni De Micheli

5

BK

TP.HCM

2 0 0 8

dce

Chương 1: Giớithiệutổng quan

¾Tổng quan

¾Mạch tổhợp2 mức

¾Mạch tổhợp nhiềumức

¾Kiểm tra (verification)

¾Kiểmthử(testing)

2 0 1 0

dce Tổng quan

•Mạch sốtích hợp

•Phương pháp thiếtkếIC

•Bốtrí mứctransistor

•Mứccổng

• Initial use of Logic Optimizaion

• Emergence of Synthesis-Base Design

• A Logic Synthesis Design Methodology

7

2 0 1 0

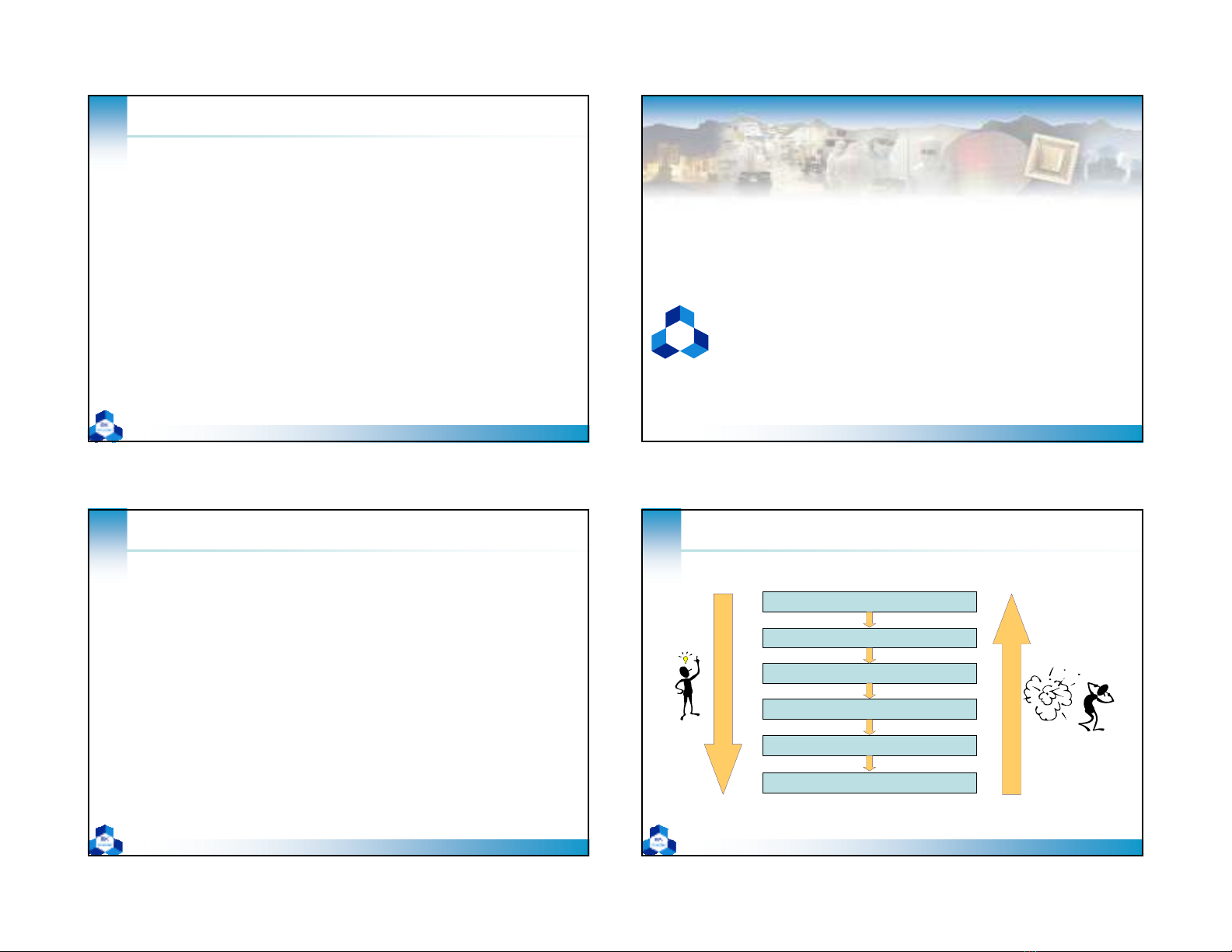

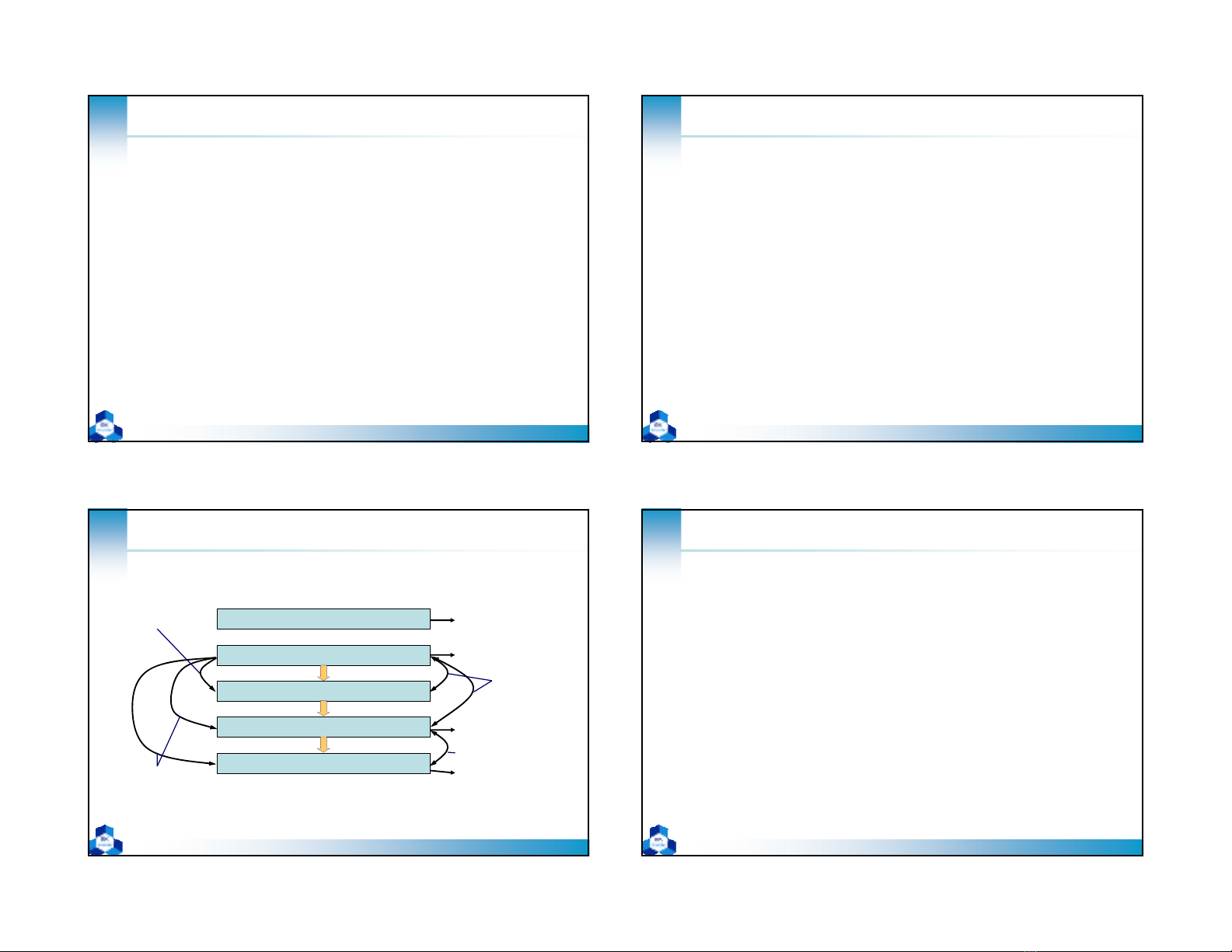

dce Design of Integrated Circuits

System Level

System Level

Register Transfer Level

Register Transfer Level

Gate Level

Gate Level

Transistor Level

Transistor Level

Layout Level

Layout Level

Mask Level

Mask Level

Design

Design

Verification

Verification

2 0 1 0

dce System Level

• Abstract algorithmic description of high-level behavior

– e.g. C-Programming language

– abstract bởi vì nó không chứabấtcứhiệnthực chi tiết nào cho thời

gian hoặcdata

–Hiệuquảđểđạtđượcmộtmôhìnhthựcthirútgọnởgiai đoạnđầu

tiên củathiếtkế

–Khókhănđể duy trì sựxuyên suốtdựán bởi vì không liên kếtđến

phầnhiệnthực

Port*

compute_optimal_route_for_packet(Packet_t *packet,

Channel_t *channel)

{

static Queue_t *packet_queue;

packet_queue = add_packet(packet_queue, packet);

...

}

2 0 1 0

dce RTL Level

module mark1;

reg [31:0] m[0:8192];

reg [12:0] pc;

reg [31:0] acc;

reg [15:0] ir;

always

begin

ir = m[pc];

if (ir[15:13] == 3b’000)

pc = m[ir[12:0]];

else if (ir[15:13]==3’b010)

acc = -m[ir[12:0]];

...

end

endmodule

module mark1;

reg [31:0] m[0:8192];

reg [12:0] pc;

reg [31:0] acc;

reg [15:0] ir;

always

begin

ir = m[pc];

if (ir[15:13] == 3b’000)

pc = m[ir[12:0]];

else if (ir[15:13]==3’b010)

acc = -m[ir[12:0]];

...

end

endmodule

• Cycle accurate model

“close” to the hardware

implementation

–Những kiểudữliệubit-

vector và cách hoạtđộng

đượctrừutượng hóa từ

hiệnthực bit-level

–Cấutrúctuầntự(e.g. if -

then - else, while loops) để

ủng hộmô hình dòng điều

khiểnphứctạp.

2 0 1 0

dce Gate Level

• Model on finite-state machine level

–Những mô hình chứcnăng trong luận lý Boolean

sửdụng registers và gates

– Các mô hình delay khác nhau cho gates và wires

1ns

1ns

4ns

4ns

3ns

3ns

5ns

5ns

2 0 1 0

dce Transistor Level

• Model on CMOS transistor level

–Được dùng trong kiểmtrasựtương đương chức

năng

–Hoặc phân tích chi tiếtvềtiming

2 0 1 0

dce Layout Level

• Transistors và wires đượcđặtnhưcác

polygons trong các lớp khác nhau như

diffusion, poly-silicon, metal, etc.

2 0 1 0

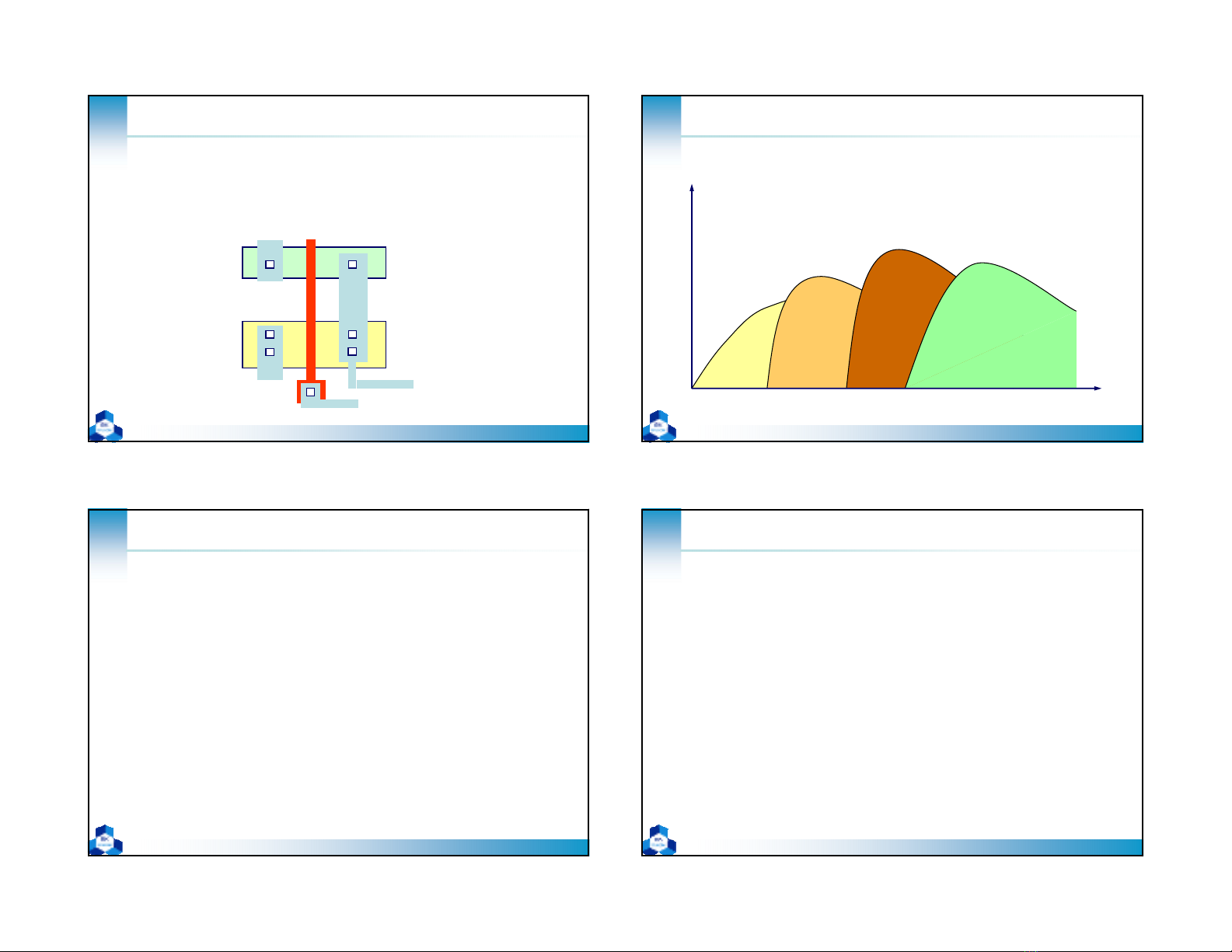

dce Design of Integrated Systems

Relative Effort

Relative Effort

Project Time

Project Time

System

System

RTL

RTL

Logic

Logic

-

-Design phases overlap to large degrees

Design phases overlap to large degrees

-

-Parallel changes on multiple levels, multiple teams

Parallel changes on multiple levels, multiple teams

-

-Tight scheduling constraints for product

Tight scheduling constraints for product

Transistor

Transistor

2 0 1 0

dce Design Challenges

• Systems đang trởnên lớnhơn, thờigianthiếtkếngày càng

phải rút ngắn

– > 100 Mio gates càng phổbiến cho ASICs

– > 0.4 Mio dòng của C-code để mô tảhành vi hệthống

– > 5 Mio dòng của RLT code

• Design teams rấtlớn cho những projects lớn

–Vàitrămngười

–Kỹnăng khác nhau

– Làm việcđồng thờiởnhiềumức khác nhau

–VIệcquảnlýđộ phứctạpvàliênlạcthiếtkếlà rấtkhókhăn

• Design tools đang ngày càng phúc tạphơnnhưng vẫnchưa

đáp ứng yêu cầu

– Thông thường ngườithiếtkếphảichạykhoảng 50 tools cho mỗi

component

– tools có nhiềulỗi, interfaces chưa thân thiệnetc.

2 0 1 0

dce Design Challenges

•Quyếtđịnh vềdesign point là rấtkhó

– performance / costs / time-to-market

–Quyếtđịnh phảiđượcthựchiện2-3 years trước khi hoàn

thành thiếtkếbefore design finished

–Cácthờiđiểmthiếtkếrấtkhóđoán trướcnếu không làm

thậtsự

–Xácđịnh vòng đờisảnphẩm

• Functional verification

–Môphỏng vẫnlàcôngcụchính cho kiểmtrachứcnăng

nhưng không đủ bởivìkíchthướccủa không gian thiếtkế

–Cáclỗi trong released hardware thì rấtđắtđể khắcphục

(khác với software)

2 0 1 0

dce Design Challenges

• Tradeoffs cơbảngiữacácmức mô hình hóa khác

nhau:

– modeling detail and team size to maintain model

• high-level models có thểđượckiểm soát bởi1 hoặc2 người

• detailed models cầnđược phân hoạch mà kếtquảlà sựkhó khăn

trong việc liên lạcgiữacáckhối

– modeling accuracy versus modeling compactness

• compact models bỏqua các chi tiếtvàđưarachỉnhững ước

lượng sơkhai cho hiệnthực

• detailed models thì kéo dài và khó khănđể thích nghi vớinhững

thay đổi trong thiếtkế

– simulation speed versus hardware performance

• high-level models có thểmô phỏng nhanh nhưng không thểhiện

thựchiệuquảvớinhững phương tiệntựđộng

• low-level models có thểhiệnthực nhanh chóng nhưng khó mô

phỏng

2 0 1 0

dce Full Custom Design Flow

• Application: những thiếtkếhiệusuấtcựccao

– general-purpose processors, DSPs, graphic chips, internet

routers, games processors etc.

• Target: thịtrường lớnvàlợi nhuậncao

– e.g. PC business

• Complexity: rấtcaovàđòi hỏilab hiệnđại

–Độingũlớn, đầutưcao và rủirocũng cao

• Vai trò Logic Synthesis:

–Hạnchếchỉcho components không chuẩn hóa vềhiệu

suấthoặccóthểthay đổisauđótrongchutrìnhthiếtkế

• non-critical data paths logic và control logic

–Mộtlượng lớn data-path components và fast control logic

đượcthiếtkếthủcông để tốiưuhiệusuất

2 0 1 0

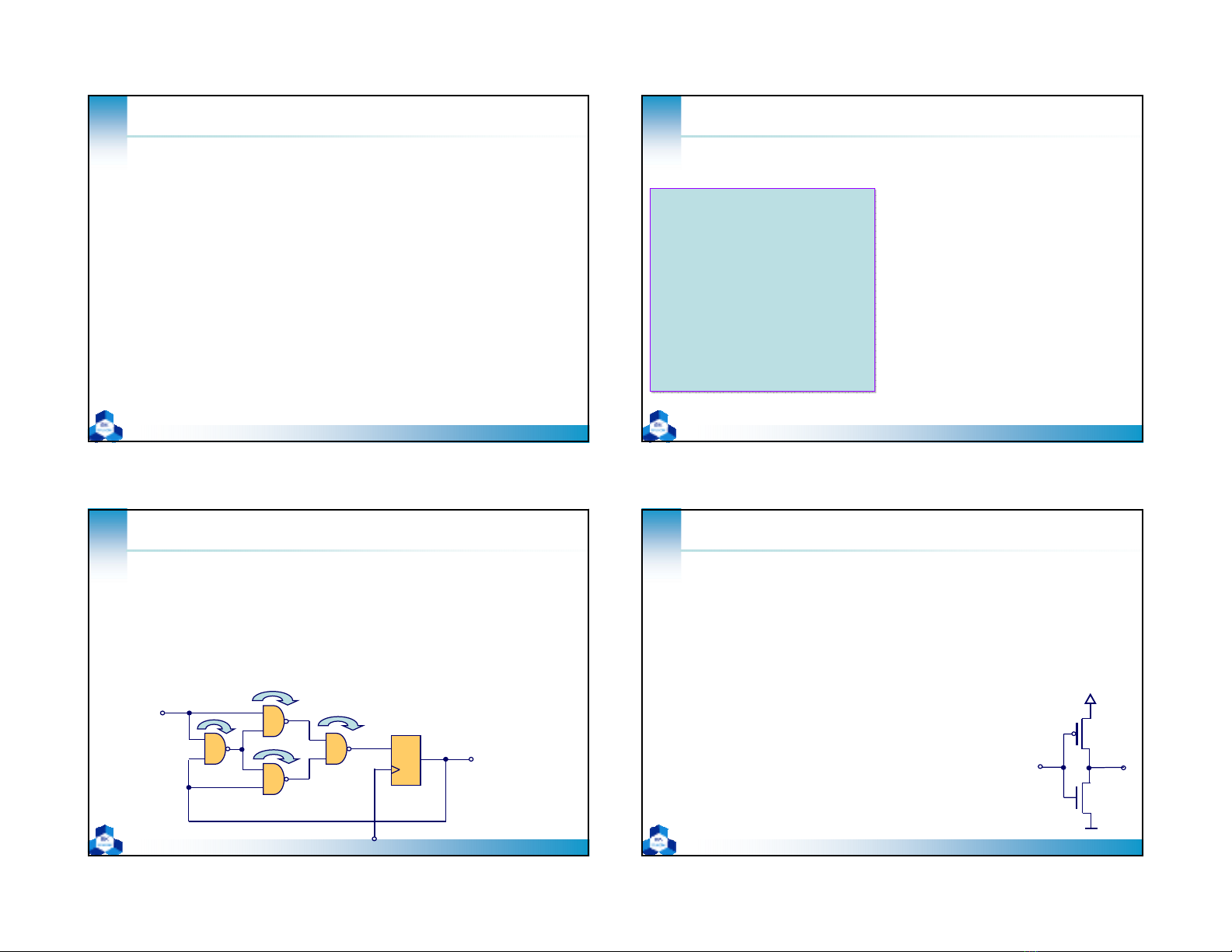

dce Full Custom Design Flow

ISA Specification

ISA Specification

RTL Spec

RTL Spec

Gate Level Netlist

Gate Level Netlist

Transistor Level Circuit

Transistor Level Circuit

Layout

Layout

Circuit Simulation

Circuit Simulation

Simulation

Simulation

Design Rule Checker

Design Rule Checker

Formal

Formal

Equivalence

Equivalence

Checking

Checking

Simulation

Simulation

Logic Synthesis

Logic Synthesis

Manual or

Manual or

semi

semi-

-automatic

automatic

Design

Design

Extract&Compare

Extract&Compare

2 0 1 0

dce ASIC Design Flow

• Application: thịtrường IC thông dụng

– peripheral chips in PCs, toys, handheld devices etc.

• Target: thịtrường trung bình và nhỏ, thờigianthiết

kếhạnchế

– e.g. consumer electronics

• Complexity of design: kiểuthiếtkếchuẩn, đoán

trướcđược

– standard flows, standard off-the-shelf tools

• Vai trò Logic Synthesis:

–Đượcsửdụng tỉlệcao trong thiếtkếngoạitrừnhững khối

đặcbiệtnhưRAM’s, ROM’s, analog components