2PáUO6PKPUO

Hardware Description Language

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

1

6èUOfU

1TkU

PVIUA

AYá•UO7>ACUP

2PáUO6PKPUO

1.1. 11h]1i=MC

oXWXh]1h_

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

2

oXXzb/Xh]1h_1bh

]imbharMCgVb/aX]1bh

11h]1i=MC

MC3pb/zbb/azhd]bXb/X]cXoXaX]

hvX]]dhXfhXVc3pah3c1b/zbb/azh

d]bXb/Xd]ohhf1bYb/X]cX]b/hfwb]

MAMZfm1/]dZZYAhZf/fVhZY1fXi1hXVW

eiXd]yb/D

K1uiX]ibAT

-

1987

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

3

K1uiX]ibAT

-

1987

KfX_]1MCfV1h]wrXx_]ob]1ib/zbb/

azhd]bXb/C

-B]zb/h]b/b]h

-DVb/XoXXhfb//b=1h]1hWXVb]pXib/

Xd

-K]iXg]iXVb]pXib/Xd

òTKIC73:

Kvb]Xzb/Xb/

-MC3pahh1uiX]ibXVA

-

B]zb/h]iXg]iXVWh_íXo

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

4

-

B]zb/h]iXg]iXVWh_íXo

b]qb]VmhX]Xbpc

-èX]hfXVb]1ib]pgblih

h]1hWXb/b]b]1ib]pXib/Xd

Xzb/Xh]1h_azd]b/]h]b/

òTKIC73:W

B]béb/]hfb]1iXzb/b/]=pd]b/

d]odh]1h_

-MCX]cd]sdh]1h_Wb/b]1id]b/

d]odb]h]1h_hhfublib/]VmhY1

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

5

d]odb]h]1h_hhfublib/]VmhY1

3ubYV=pch]=1bXxgb

-MChfb]1iXzb/b/]

-MCXx_]béb/d]X=hhb]1iaX

vX]h]1h__]oXb]Vid]W1b3ph]1h_

IC- b/Yb/Xh]3pAdd31XVh1cb

Specified).

òTKIC73:W

èX3dXzb/b/]

-cpbhcpbX3d=1Xzb/b/]X]hc

d]bXb/

B]béb/azhafb/

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

6

B]béb/azhafb/

-MCX]cd]sdazh]chb/XV

d]bXb/haX]h]b/g]dZb

X]cbXoXaXXb/

-Mxh]azd]b/ahWbh]1h_

WVc/aXXoX]XcbXazhX]1

h1h

òTKIC73:W

B]béb/hfVc1_hei

-MC3pahh1uiX]ibXX]db]bbubah

az]wb]MCXxh]X]mhfuba1Wazd]b/

odb/Xh1uiX]ibMC

B]béb/]hfh]1h_aX3b=p_]béb/

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

7

B]béb/]hfh]1h_aX3b=p_]béb/

gYb/31h]1h_

-Cpb/zbb/3dhfwb]WXXVcbubMCXxh]

gYb/h]1h_ah]h]b/3b=1g

h]Va/1VXVahb]xab]1ib/1

ubhfcb/MCXxb]1ihvb]béb/]=1Xeib

3h]b/]1a=pX]1Vgh]1h

MCXb/X]cd]sdYb/31XoXd]brXx

2PáUO6PKPUO

11h]1i=MC

1.2. oXWXh]1h_

oXXzb/Xh]1h_1bh

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

8

oXXzb/Xh]1h_1bh

]imbharMCgVb/aX]

1bh

oXWXh]1h_

hZdM1harMC

(Register Transfer Level)

hZdKb/]d

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

9

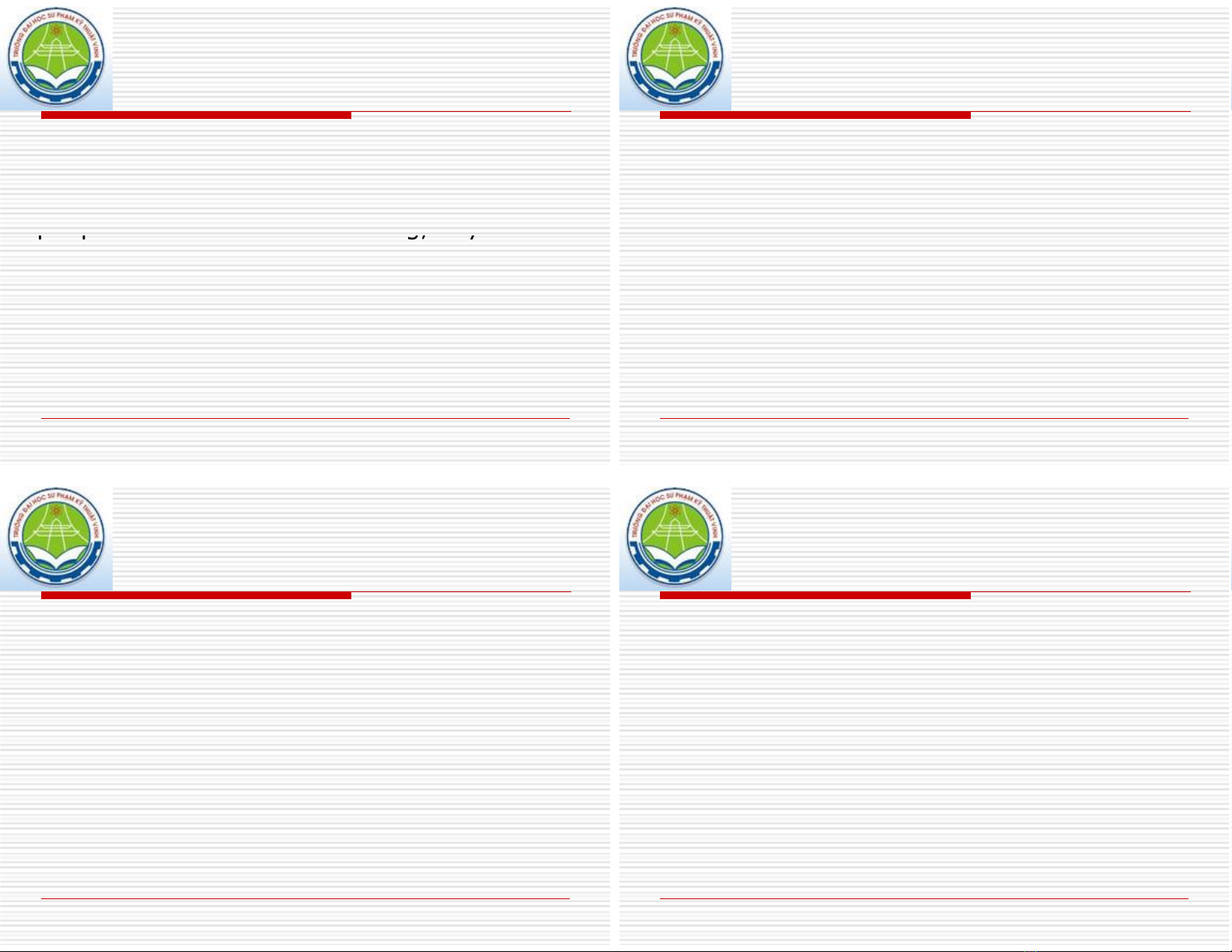

hZdKb/]d

-1ubYX]arMCh]pb]EZh31g

-K1iEZh31g=hXY1bhvX]

azd]b/h]1h_

hZdOdX]=pYqmb1Yb/d]b

aahcCVmcihX]c]1dGCG]cX

XoXahbX]cA

2PáUO6PKPUO

11h]1i=MC

oXWXh]1h_

oXXzb/Xh]1h_1bh

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

10

oXXzb/Xh]1h_1bh

]imbharMCgVb/aX]

1bh

oXXzb/Xh]1h_1bh

O131blgA

3hZfVgHiVfhigAA

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

11

http://www.xilinx.com/webpack/index.htm .

uáWPUTT

http://www.xilinx.com/support/download/index.htm

2PáUO6PKPUO

11h]1i=MC

oXWXh]1h_

oXXzb/Xh]1h_1bh

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

12

oXXzb/Xh]1h_1bh

]imbharMCgVb/aX]

1bh

]imbharMCgVb/

aX]1bh

MXb/

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

13

DX]1b

b/X]qb3

2PáUO2êYlKTcSUP

Hardware Description Language

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

14

6èUOfU

1TkU

PVIUA

AYá•UO7>ACUP

2PáUO2êYlKTcSUP

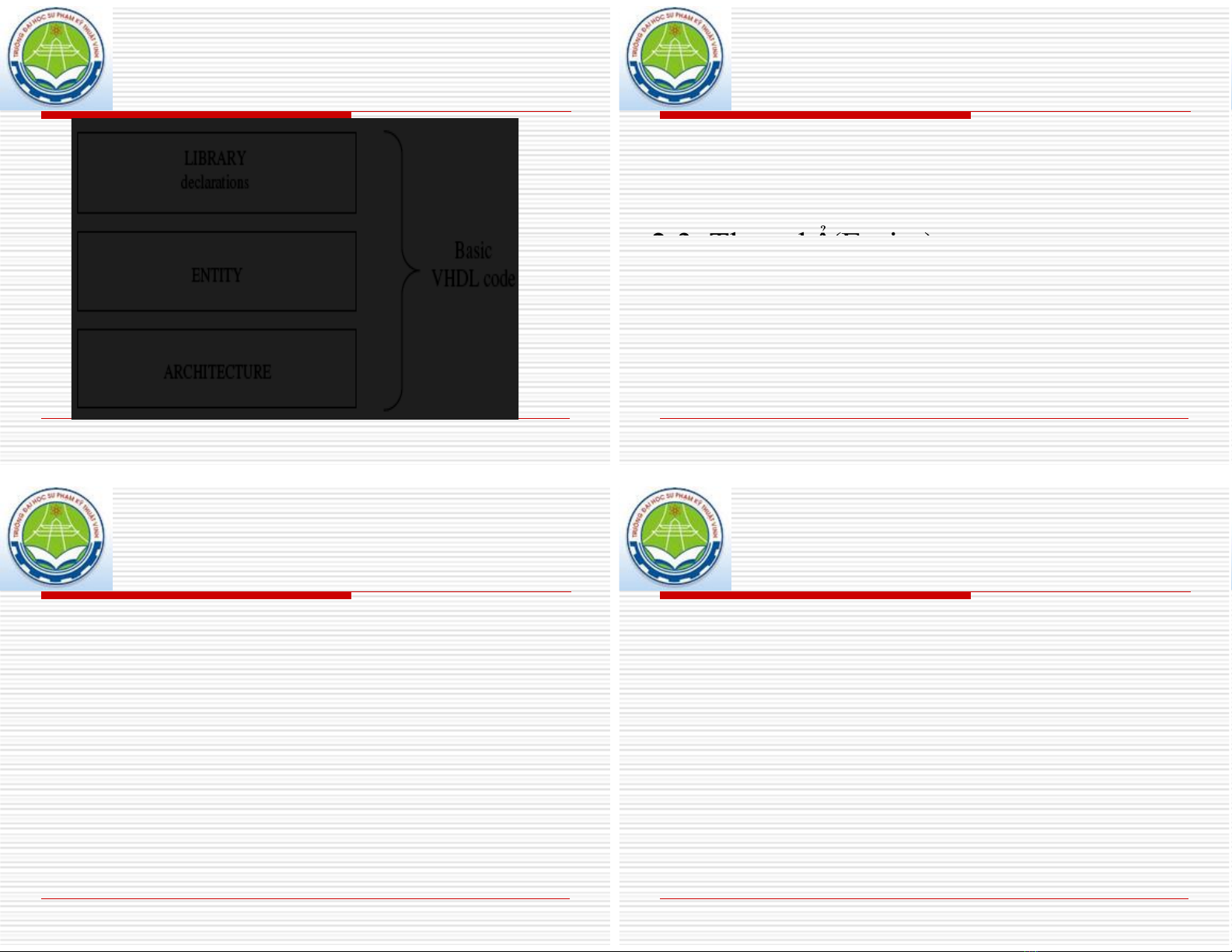

2KUúKèUKIC73:

PIVPáU:YIY_

APKPò4U_

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

15

APKPò4U_

UYlKYKPMKYM

2KgL

oXb=XWbXVMC

n ;cC73:OTIWPUKèUI

-PIV:1FPáU6TLIUPKPKKPáULUO

YVUOPRC3444A3D=p

-4<AAFPKPò;kèKKKUOaVYIKITéKPU;èTéKP

UUOX

-

27A42AB4RUYlK;kèKPfUYVUOKITéKPU

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

16

-

27A42AB4RUYlK;kèKPfUYVUOKITéKPU

nLIBRARY:

-AíWPWKKVéUSUPPá•UOLUO

-2PVWPdWLUOSéKKVéUTcSUPaKPIKKUOLUORPK

-;c:UPáKPRPMVRPkULéUOKI5B<2A=<>=24PI_

2=;>=<4<AaáKfUYVUOKI>264

oXb=XWbXV

MCh1d

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

17

2PáUO2êYlKTcSUP

2KUúKèUKIC73:

PIVPáU:YIY_

APKPò4U_

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

18

APKPò4U_

UYlKYKPMKYM

2KgL

B]V1Woch]=1bC1WfVfm

LIBRARY library_name;

USE library_name.package_name.package_parts;

d]od

K]b/gYb/XoXh]=1bgVi

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

19

LIBRARY ieee;

USE ieee.std_logic_1164.all

LIBRARY std;

USE std.standard.all;

LIBRARY work;

USE work.all;

-oX h] =1b std =p work h]b/ 3p aX b] =w h] _]zb/ Xb khai Woc

X]b/ X] Xx h] =1b ieee 3p Xb d]1 X =1h f ra.

B]V1Woch]=1bK1d

- Yb/ h] =1b IEEE khi Yb/ XoX _1i Y 31i STD_LOGIC,

STD_ULOGIC.

CPxàUNNNLPUPOiUPx

1/9/2012 8:05:21 PM Very High Speed Intergated Circuit

Hardware Description Language

20

std_logic_1164b]fKTCFAVaX

std_logic_arithb]fXoX_1iY31iAE=pLEAEXoX/11

h]ih31ubeiVb=pgcgob]hcobhExXb/X]Vb]1i]paX]imb1Y

31iapX]cd]sdah_1iXX]imb1h]pb]XoX_1iY31i_]oX

-std_logic_signedX]VXoX]paX]cd]sd3pa=1X=1Y31i

KTCFATMKFIXh]X]1bX]_]1Y31i3p_1iAE

- std_logic_unsignedX]VXoX]paX]cd]sd3pa=1X=1Y31i

KTCFATMKFIXh]X]1bX]_]1Y31i3p_1iLEAE