1

Trường Đại Học Bách Khoa Hà Nội

Khoa Điện Tử Viễn Thông

====o0o====

TRUNG TÂM THỰC HÀNH ĐIỆN TỬ

BÁO CÁO THỰC TẬP

MẠCH ĐỒNG HỒ SỐ

Giáo viên hướng dẫn :

Sinh viên thực hiện : Nguyễn Anh Tuấn 20073168 DT9

Tạ Anh Tú 20073385 DT9

Trần Văn Tiến 20072899 DT9

HÀ NỘI – 9/2010

2

Mục Lục

Chương I: CƠ SỞ LÝ THUYẾT LIÊN QUAN................................................................3

I. Flip Flop: .....................................................................................................................3

1.1 Khái niệm:.................................................................................................................3

1.2 Hoạt động của FF: .....................................................................................................3

1.3 Phân loại FF: .............................................................................................................3

II. Hệ chuyển mã:............................................................................................................4

2.1 Số BCD: ( Binary Code Decimal)..............................................................................4

2.2 Hệ chuyển từ mã nhị phân sang mã BCD:..................................................................4

III. Hệ mã hoá và giải mã: ...............................................................................................5

3.1 Hệ mã hoá: ................................................................................................................5

3.2. Hệ giải mã:...............................................................................................................6

IV. Hệ tuần tự: ( hệ đếm).................................................................................................8

4.1 Khái niệm:.................................................................................................................8

4.2 Hệ đếm bất kỳ: ..........................................................................................................8

4.3 Ghép các hệ đếm: ......................................................................................................9

Chương II: THIẾT KẾ SƠ ĐỒ MẠCH..........................................................................10

I. Sơ đồ khối:.................................................................................................................10

II. khối tạo xung-IC 7400 (NAND)................................................................................11

III. Khối đếm:................................................................................................................11

IV. Khối giải mã:...........................................................................................................14

V. Khối hiển thị:............................................................................................................17

VI. Mạch đồng hồ số:....................................................................................................18

6.1 Sơ đồ nguyên lý:......................................................................................................18

6.2 Nguyên lý hoạt động: ..............................................................................................19

3

Chương I: CƠ SỞ LÝ THUYẾT LIÊN QUAN

I. Flip Flop:

1.1 Khái niệm:

Flip Flop được cấu tạo từ các cổng logic, có thể nói FF là tổ hợp các

cổng logic hoạt động theo một quy luật định trước.

FF bao gồm:

- Chân nhận xung đồng hồ, xung nhịp, xung clock (Ck).

- Hai ngõ ra dữ liệu (data) là Q và

Q

.

- Có 1 hoặc 2 ngõ chức năng quy định hoạt động của FF: S, R, D, J, K.

- Ngoài ra FF còn có hai chân: Clr ( clear) và chân Pre ( Preset). Khi tác

động vào chân Clr sẽ xoá FF làm Q = 0,

Q

= 1. Khi tác động vào chân

Pre sẽ đặt FF làm Q = 1,

Q

= 0.

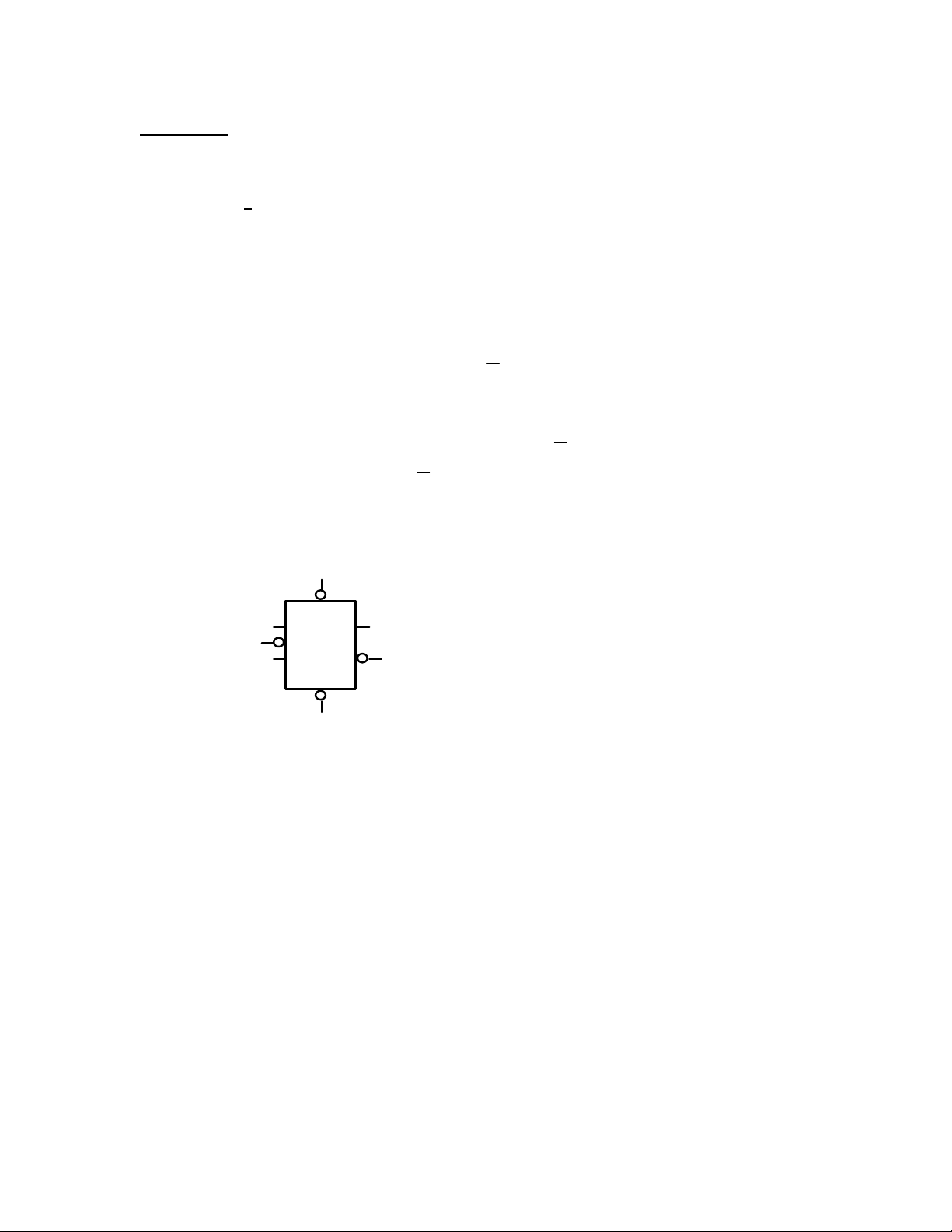

1.2 Hoạt động của FF:

S

J

CP

K

R

Q

_

Q

JK- FF

Khi nhận một xong clock tại chân Ck, FF sẽ thay đổi trạng thái một

lần. Trạng thái mới sẽ tuỳ thuộc vào mức logiccủa các chân chức năng, và

tuỳ thuộc theo bảng sự thật của mỗi loại FF.

1.3 Phân loại FF:

Theo chức năng: có 4 loại: SK- FF, D- FF, T- FF, JK- FF.

Theo trạng thái tác động của xung clock: có 5 loại:

- FF tác đọng mức 0.

- FF tác động mức 1.

- FF tác động cạnh lên.

- FF tác động cạnh xuống.

- FF tác động chủ - tớ.

4

II. Hệ chuyển mã:

2.1 Số BCD: ( Binary Code Decimal).

Được tạo nên khi ta mã hoá mỗi đecac của một số thập phân dưới

dạng một số nhị phân 4 bit.

18 BCD

0001 1000

* Lưu ý: các phép cộng và trừ số BCD được thực hiện giống như số nhị

phân. Tuy nhiên nếu phép tính có nhớ thì sau khi được kết quả ta phải hiệu

đính bằng cách trừ cho 10(D) hay cộng 6(D).

Thông thừờng sau mỗi lệnh cộng hoặc trừ số BCD ta kèm theo lệnh

hiệu đính.

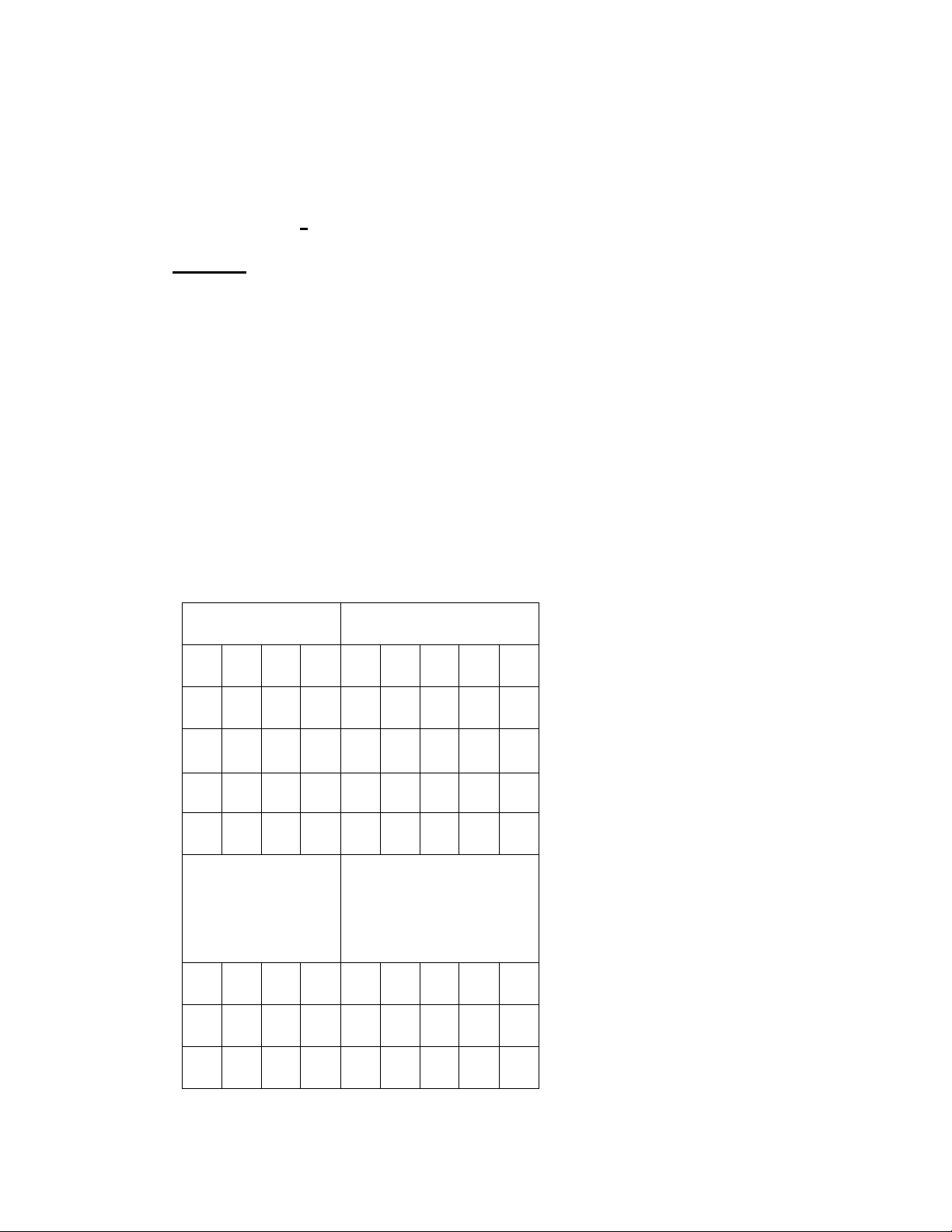

2.2 Hệ chuyển từ mã nhị phân sang mã BCD:

* Bảng sự thật:

Nhị phân BCD

X4

X3

X2

X1

Y5

Y4

Y3

Y2

Y1

0 0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 0 1

0 0 1 0 0 0 0 1 0

0 0 1 1 0 0 0 1 1

.

.

.

.

.

.

.

.

.

1 0 0 1 0 1 0 0 1

1 0 1 0 1 0 0 0 0

1 0 1 1 1 0 0 0 1

5

1 1 0 0 1 0 0 1 0

1 1 0 1 1 0 0 1 1

1 1 1 0 1 0 1 0 0

1 1 1 1 1 0 1 0 1

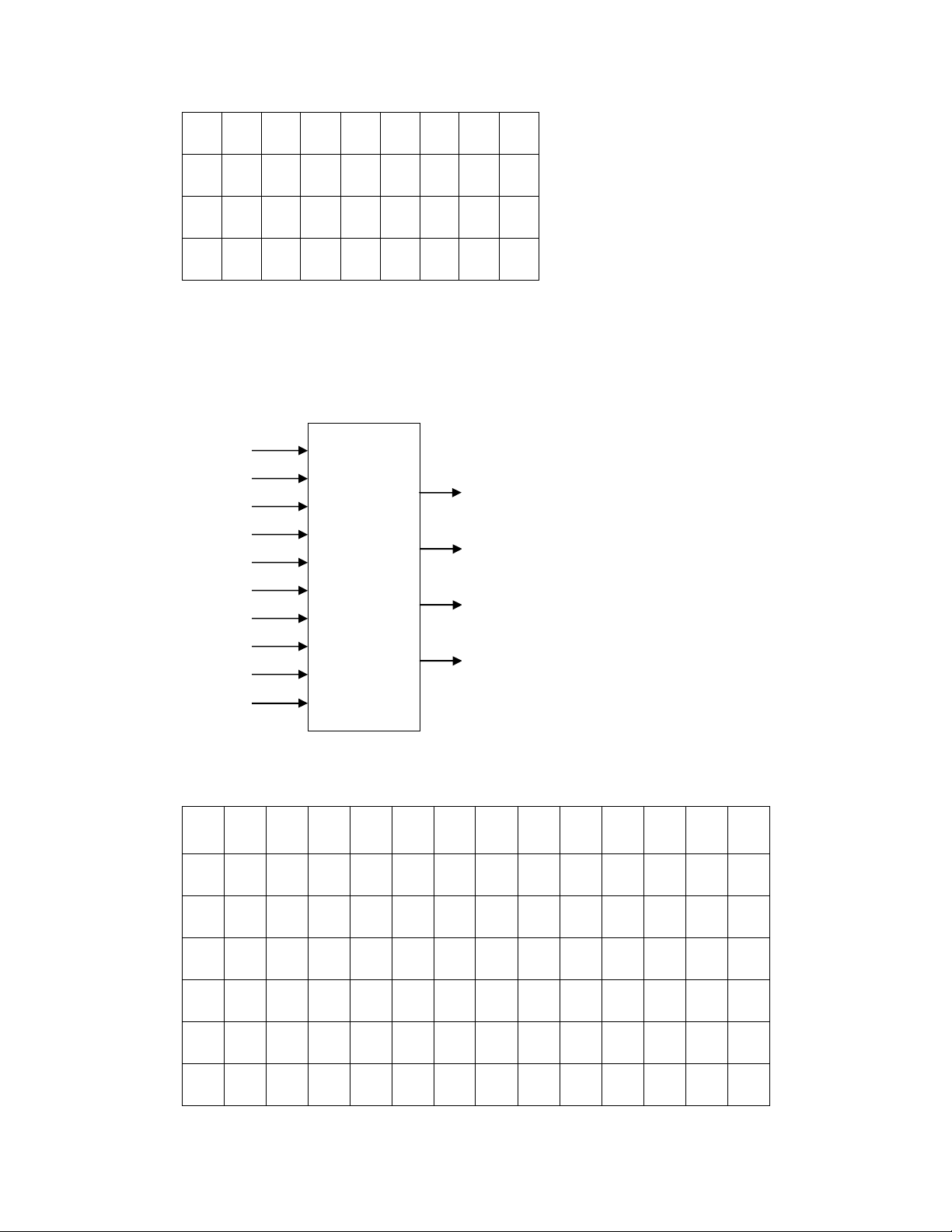

III. Hệ mã hoá và giải mã:

3.1 Hệ mã hoá:

Mã hoá thập phân thành nhị phân:

* Bảng sự thật:

0 1 2 3 4 5 6 7 8 9 D C B A

1 0 0 0 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 0 0 0 0 1 0 1

1

2

3

4

5

0

6

7

8

9

A

B

C

D

( LSB)

( MSB)

![Báo cáo thực tập tốt nghiệp Công ty TNHH Cơ điện Samwa Tek: [Mô tả chi tiết hơn về nội dung báo cáo nếu có thể]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250917/trantiendat_ct2/135x160/96461758161119.jpg)

![Báo cáo thực tập tại Garage Car Plus [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250810/nguyenanhquoc2809@gmail.com/135x160/25661754896300.jpg)

![Đồ án tốt nghiệp: Tính toán, kiểm tra hệ thống điều hòa không khí cho tòa nhà Depot Tham Lương [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250717/vijiraiya/135x160/40421752722146.jpg)