ChươngChương

22

::

CôngCông

nghệnghệ

CMOSCMOS

ChươngChương

22

::

CôngCông

nghệnghệ

CMOSCMOS

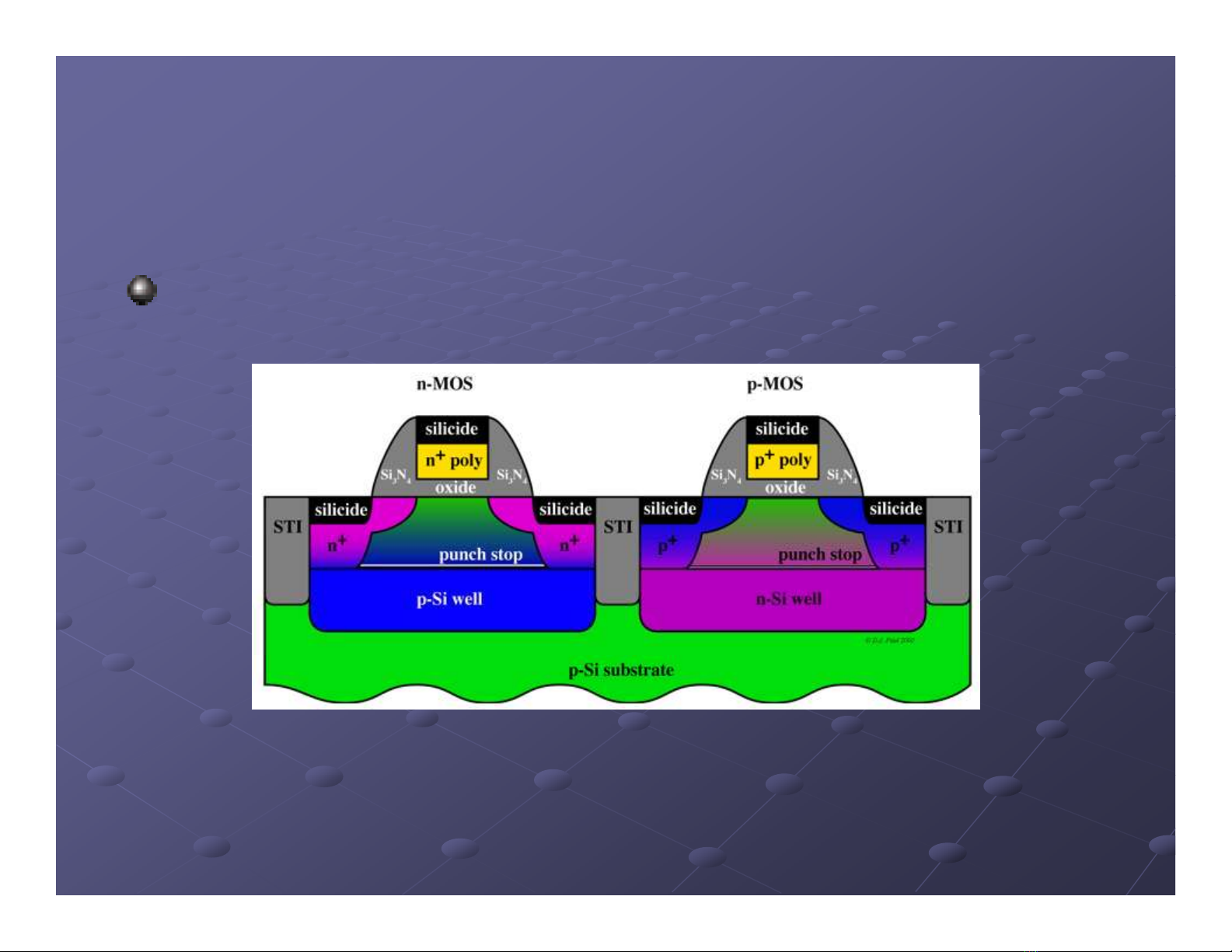

CấuCấu

trúctrúc

củacủa

pp

--

mosmos

vàvà

nn

--

mosmos

CấuCấu

trúctrúc

củacủa

pp

mosmos

vàvà

nn

mosmos

Thái nguyên 08/2008 Slide Slide 3131

Thiết kế vi mạch VLSI Thiết kế vi mạch VLSI -- ASIC ASIC --FPGAFPGA

22

11

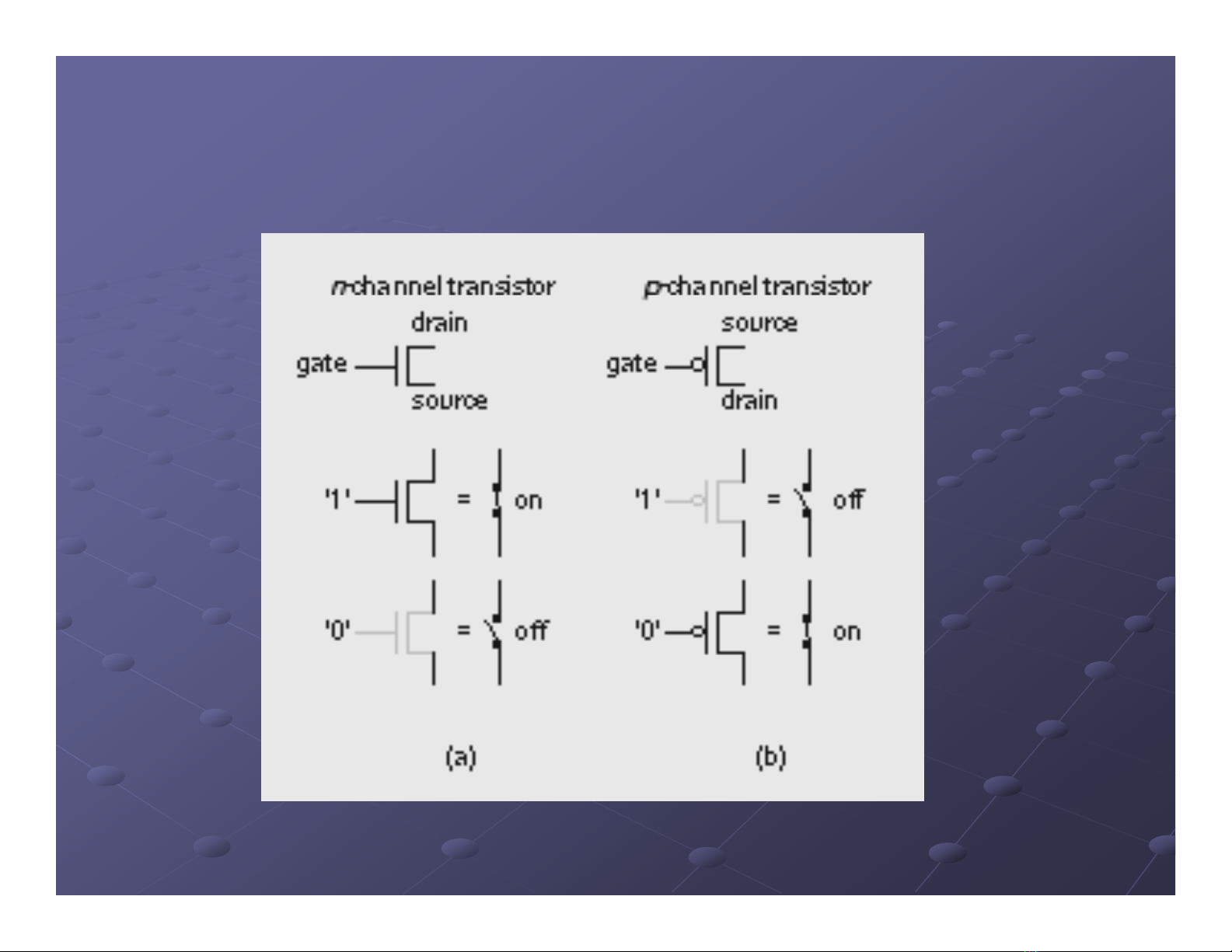

ChuểnChuển

mạchmạch

TransistorTransistor

MOSMOS

22

..

11

..

ChuểnChuển

mạchmạch

TransistorTransistor

MOSMOS

Thái nguyên 08/2008 Slide Slide 3232

Thiết kế vi mạch VLSI Thiết kế vi mạch VLSI -- ASIC ASIC --FPGAFPGA

22

22

LogicLogic

CMOSCMOS

22

..

22

..

LogicLogic

CMOSCMOS

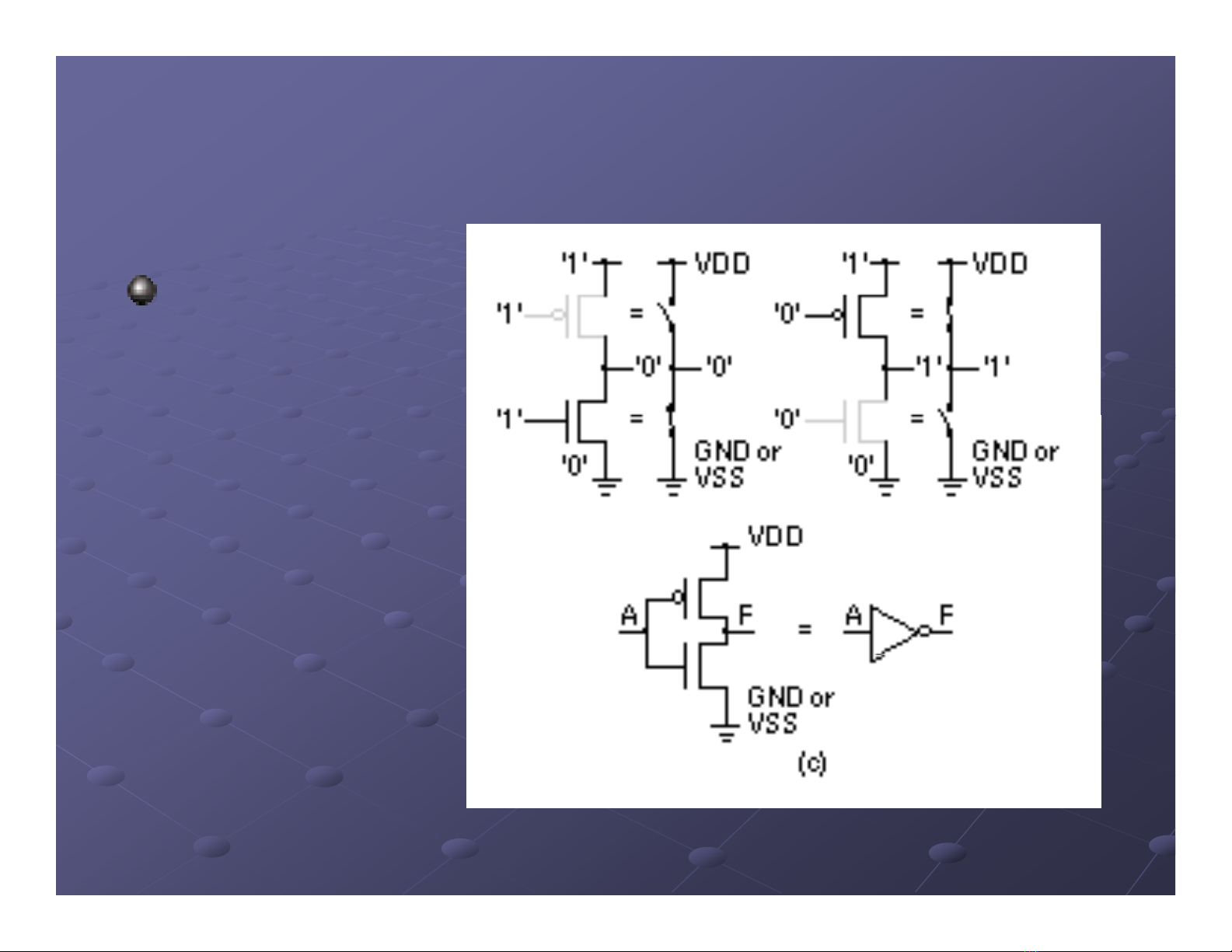

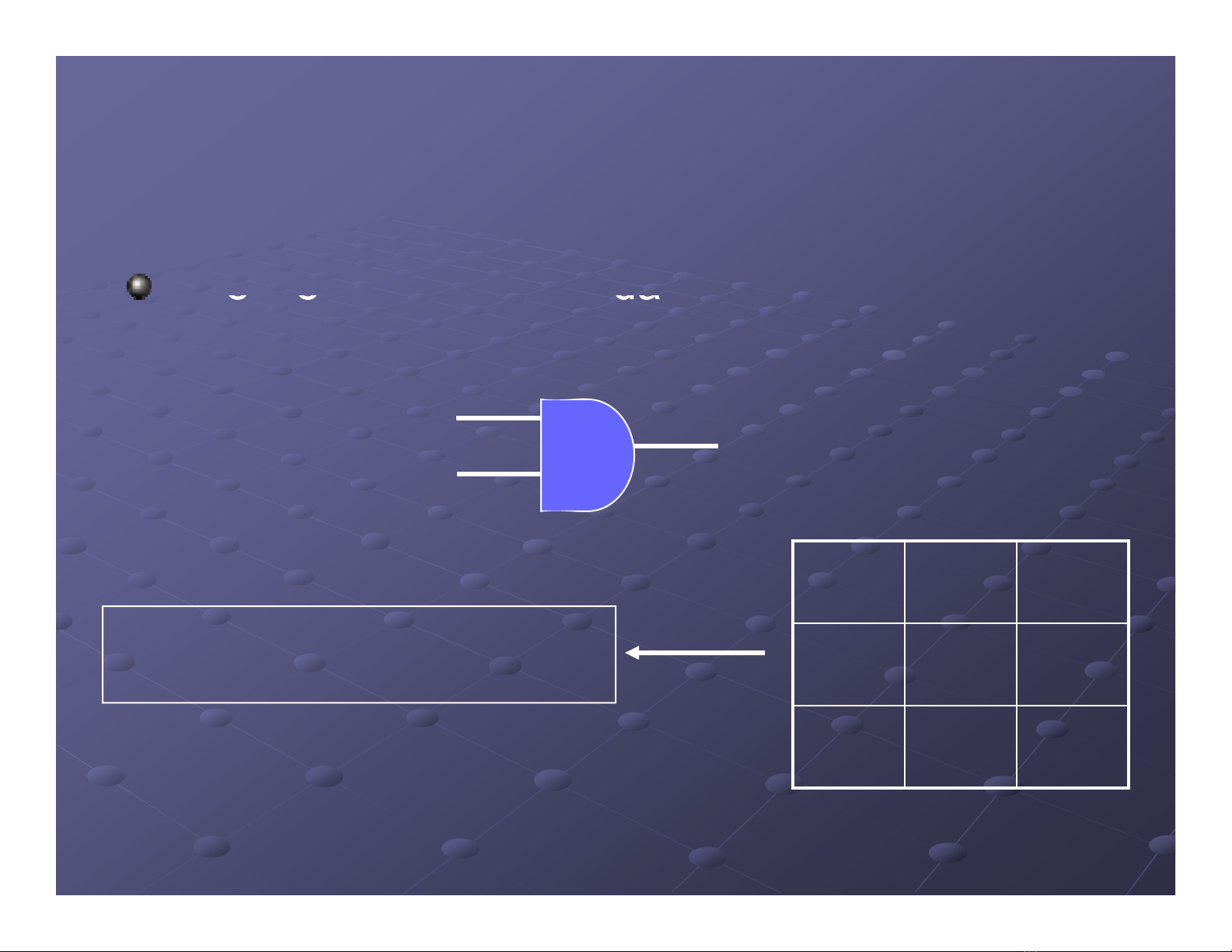

CổngCổng

đảođảo

::

CổngCổng

đảođảo

::

Thái nguyên 08/2008 Slide Slide 3333

Thiết kế vi mạch VLSI Thiết kế vi mạch VLSI -- ASIC ASIC --FPGAFPGA

22

22

LogicLogic

CMOSCMOS

22

..

22

..

LogicLogic

CMOSCMOS

NguyênNguyên

tắctắc

ghepghep

cổngcổng

CMOSCMOS

NguyênNguyên

tắctắc

ghepghep

cổngcổng

CMOSCMOS

NguyênNguyên tắctắcmắcmắc songsong songsong chocho logiclogic OROR

NguyênNguyên

tắctắc

mắcmắc

nốinối

tiếptiếp

chocho

logiclogic

ANDAND

NguyênNguyên

tắctắc

mắcmắc

nốinối

tiếptiếp

chocho

logiclogic

ANDAND

NguyênNguyên tắctắcthiếtthiếtkếkếmạchmạch CMOSCMOS

ếế

((

ầầ

Vi

ế

tVi

ế

t hàmhàm chocho FF

((

dùngdùng bìabìa cacnocacno nhómnhóm ph

ầ

nph

ầ

n

tửtử11))

ViếtViết

hàhà

hh

F’F’

((

dùdù

bìbì

hóhó

hầhầ

ViếtViết

hà

m

hà

mc

h

oc

h

o

F’F’

((

dù

ng

dù

ng

bì

a

bì

acacnocacno n

hó

mn

hó

mp

hầ

np

hầ

n

tửtử00,,hoặchoặclấylấyđảođảocủacủaF)F)

Thái nguyên 08/2008 Slide Slide 3434

Thiết kế vi mạch VLSI Thiết kế vi mạch VLSI -- ASIC ASIC --FPGAFPGA

22

22

LogicLogic

CMOSCMOS

22

..

22

..

LogicLogic

CMOSCMOS

ThiếtThiết

kếkế

côngcông

ANDAND

haihai

đầuđầu

vàovào

ThiếtThiết

kếkế

côngcông

ANDAND

haihai

đầuđầu

vàovào

a

a

b

F = a.b

ff0011

00

00

00

F = a.b {dùng mạch nối tiếp}

00

00

00

110011

F’ = a’ + b’ {dùng mạch song song}

Thái nguyên 08/2008 Slide Slide 3535

Thiết kế vi mạch VLSI Thiết kế vi mạch VLSI -- ASIC ASIC --FPGAFPGA

![Giáo trình Vi mạch tương tự (Phần 2): CĐ Giao thông Vận tải [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210708/bautroimaudo/135x160/1952838099.jpg)

![Giáo trình Vi mạch số: Phần 2 - CĐ Giao thông Vận tải [Tài liệu đầy đủ]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210708/bautroimaudo/135x160/1078090755.jpg)

![Giáo trình Vi mạch số lập trình (Điện tử công nghiệp) - CĐ Công nghiệp và Thương mại [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210601/ermintrudetran/135x160/9681622516104.jpg)

![Bài giảng Tổ chức - Cấu trúc Máy tính II Đại học Công nghệ Thông tin (2022) [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/8531747304537.jpg)