Chương 6:

PHÂN CỰC CHO TRASISTOR

HIỆU ỨNG TRƯỜNG (FET)

BỘ GIÁO DỤC VÀO ĐÀO TẠO

ĐH Sư Phạm Kỹ Thuật TP.HCM

KHOA ĐIỆN – ĐIỆN TỬ

Bộ Môn Cơ Sở Kỹ Thuật Điện tử

NỘI DUNG CHÍNH

6.1 Mạch phân cực cho JFET

Mạch phân cực cố định

Mạch phân cực cầu phân áp

Mạch phân cực hồi tiếp áp

6.2 Mạch phân cực cho D-MOSFET

6.3 Mạch phân cực cho E-MOSFET

Mạch phân cực hồi tiếp

Mạch phân cực cầu phân áp

3

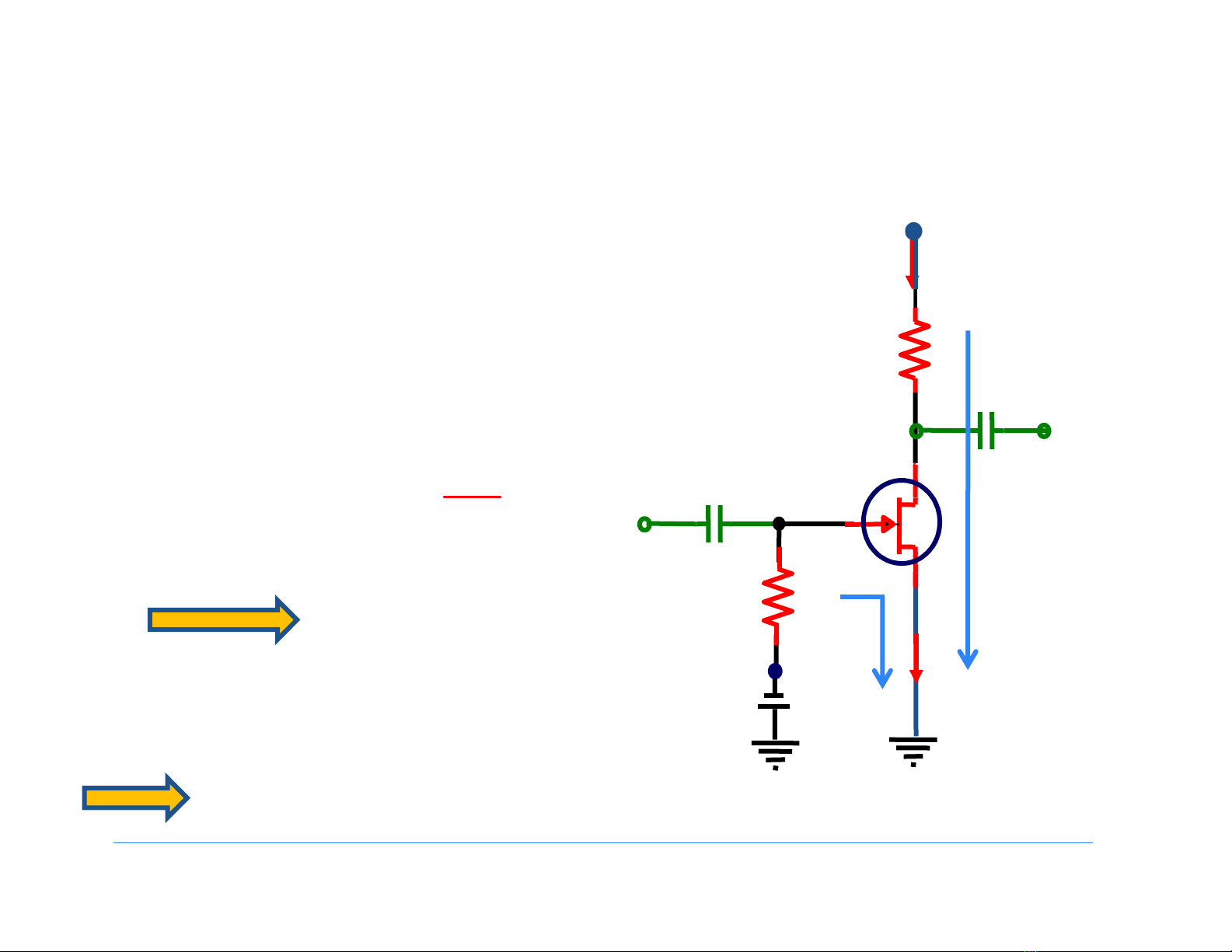

6.1. Các dạng mạch phân cực cho JFET

6.1.1. Mạch phân cực cố định:

RD

C1

Vi

VGG

RG

1M

VO

C2

NJFET

G

D

S

IS

ID

VDD

IG= 0, ID= IS

VDS = VDD – ID.RD

2

1GS

D DSS

P

V

I I

V

GS GG

V V

* Mạch vòng GS:

Thế (1) vào phương trình Shockley:

* Mạch vòng DS:

(1)

ID1, ID2

Điểm làm việc tĩnh Q(ICQ, VCEQ)

4

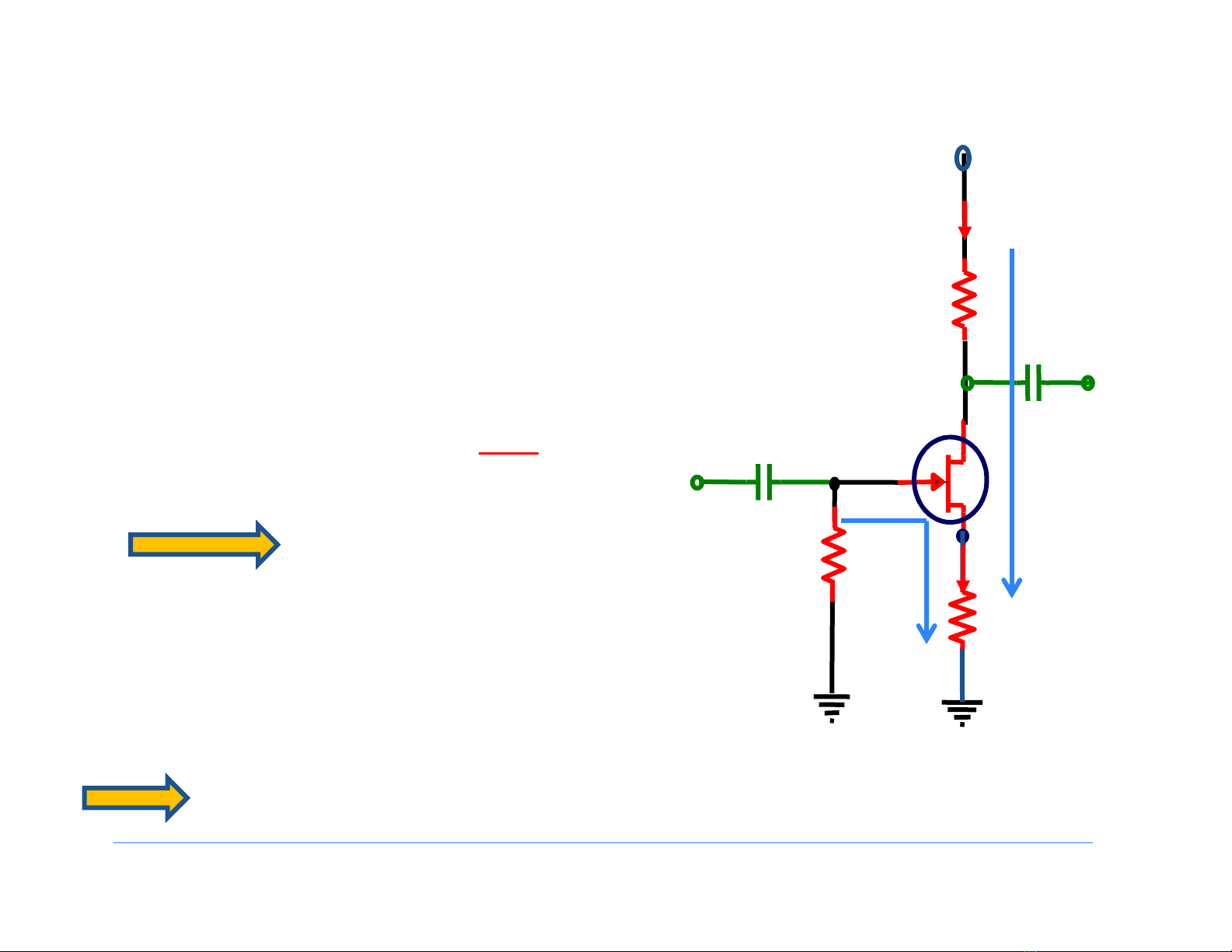

RD

C1

ViRG

1M

VO

C2

NJFET

G

D

S

ID

RS

IS

VDD

VDS = VDD – ID.(RD+RS)

.

GS D S

V I R

IG= 0, ID= IS

* Mạch vòng GS:

2

1GS

D DSS

P

V

I I

V

Thế VGS vào phương trình Shockley:

* Mạch vòng DS:

Chọn nghiệm thoả điều kiện: 0 IDIDSS

VPVGS 0

ID1, ID2

6.1. Các dạng mạch phân cực cho JFET

6.1.2. Mạch tự phân cực:

Điểm làm việc tĩnh Q(IDQ, VDSQ)

5

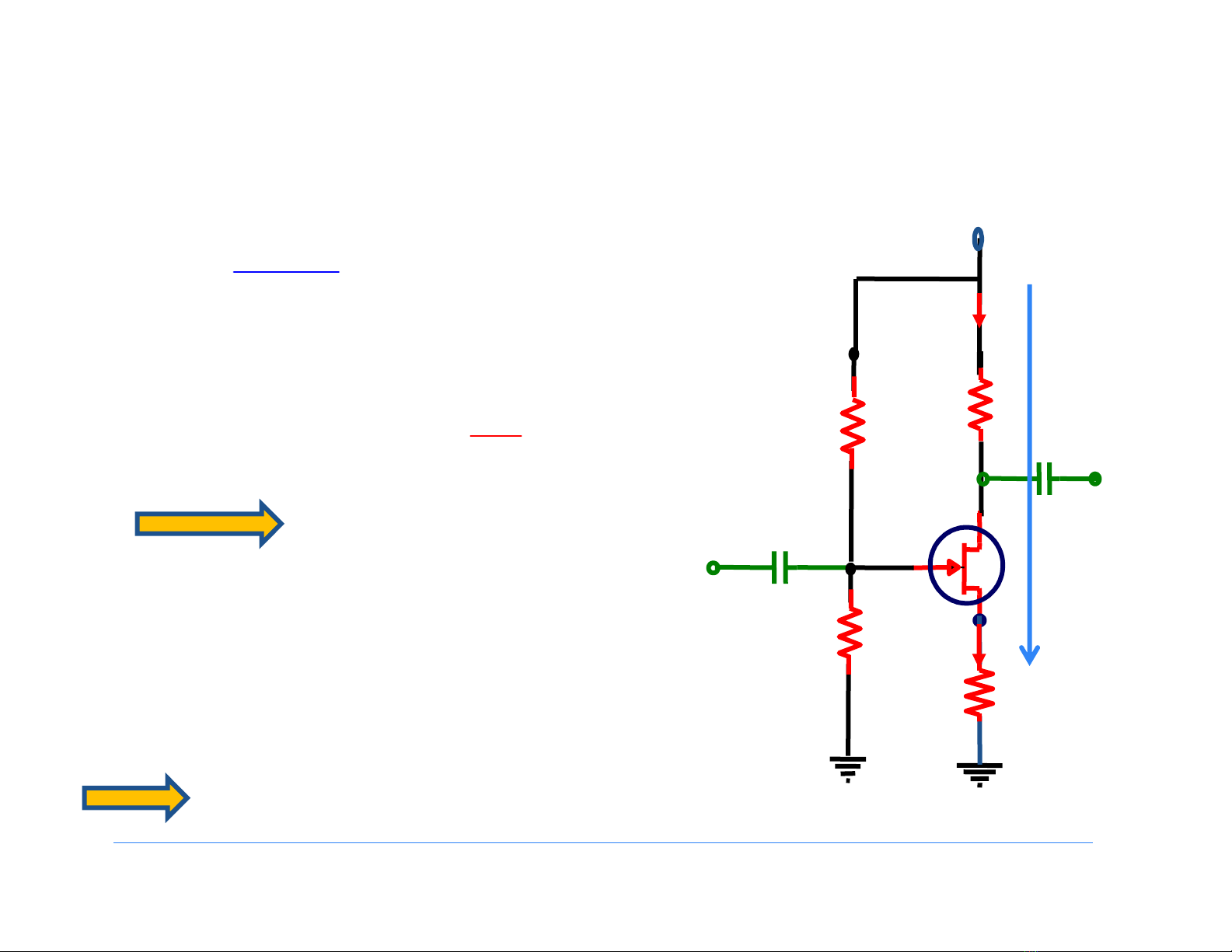

RD

C1

Vi

R2

VO

C2

NJFET

G

D

S

ID

RS

IS

R1

VDD

VDS = VDD – ID.(RD+RS)

2

1GS

D DSS

P

V

I I

V

2

1 2

G DD

R

V V

R R

.

GS D S G

V I R V

IG= 0, ID= IS

Thế VGS vào phương trình Shockley:

* Mạch vòng DS:

Chọn nghiệm thoả: 0 IDIDSS

VPVGS 0

ID1, ID2

6.1. Các dạng mạch phân cực cho JFET

6.1.3. Mạch phân cực cầu phân áp:

Điểm làm việc tĩnh Q(IDQ, VDSQ)

![Đề thi học kì 2 môn Vật lí 1 năm 2023-2024 có đáp án [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260507/hoahongxanh0906/135x160/64291778553454.jpg)

![Đề thi học kì 2 Vật lí 1 năm 2023-2024 có đáp án [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260507/hoahongxanh0906/135x160/1381778553461.jpg)

![Đề thi học kì 2 Vật lí 1 năm 2022-2023 có đáp án [kèm PDF]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260507/hoahongxanh0906/135x160/21778553462.jpg)