CHỨC NĂNG VÀ THÔNG SỐ CỦA BUS

Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

•Bus là đường truyền tín hiệu có chức năng lưu thông, vận chuyển tín hiệu,dữ liệu

giữa các khối chức năng trong hệ thống máy tính.

•Bus thường có 50 đến 100 dây dẫn được gắn trên mainboard.

•Với các đường dây dẫn, Bus truyền tín hiệu giữa bộ vi xử lý và các bộ phận khác,

hoặc thiết bị này với các thiết bị khác trong hệ thống máy tính.

CHỨC NĂNG VÀ THÔNG SỐ CỦA BUS

Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

•Độ rộng bus (bus width, đơn vị bit):là số bit dữ liệu tối đa có thể truyền trong 1

chu kỳ dữ liệu của bus (số bit dữ liệu tối đa trong 1 lần truyền).

•Tốc độ bus (bus speed, đơn vị MHz): tốc độ truyền tối đa của bus.

•Chu kỳ dữ liệu xung nhịp (clock data cycle): số chu kỳ xung nhịp cần thiết để

truyền 1 chu kỳ dữ liệu.

•Băng thông (Bandwidth, đơn vị MBps): Số bit dữ liệu tối đa truyền trên một đơn vị

thời gian (giây).

Băng thông [MB/s] = 𝑇ố𝑐 độ 𝐵𝑈𝑆 𝑀𝐻𝑧 ∗𝑆ố 𝑏𝑦𝑡𝑒 𝑡𝑟𝑜𝑛𝑔 1 𝑙ầ𝑛 𝑡𝑟𝑢𝑦ề𝑛 𝑡ả𝑖

𝐶ℎ𝑢 𝑘ỳ 𝑑ữ 𝑙𝑖ệ𝑢 𝑡ℎ𝑒𝑜 𝑥𝑢𝑛𝑔 𝑛ℎị𝑝

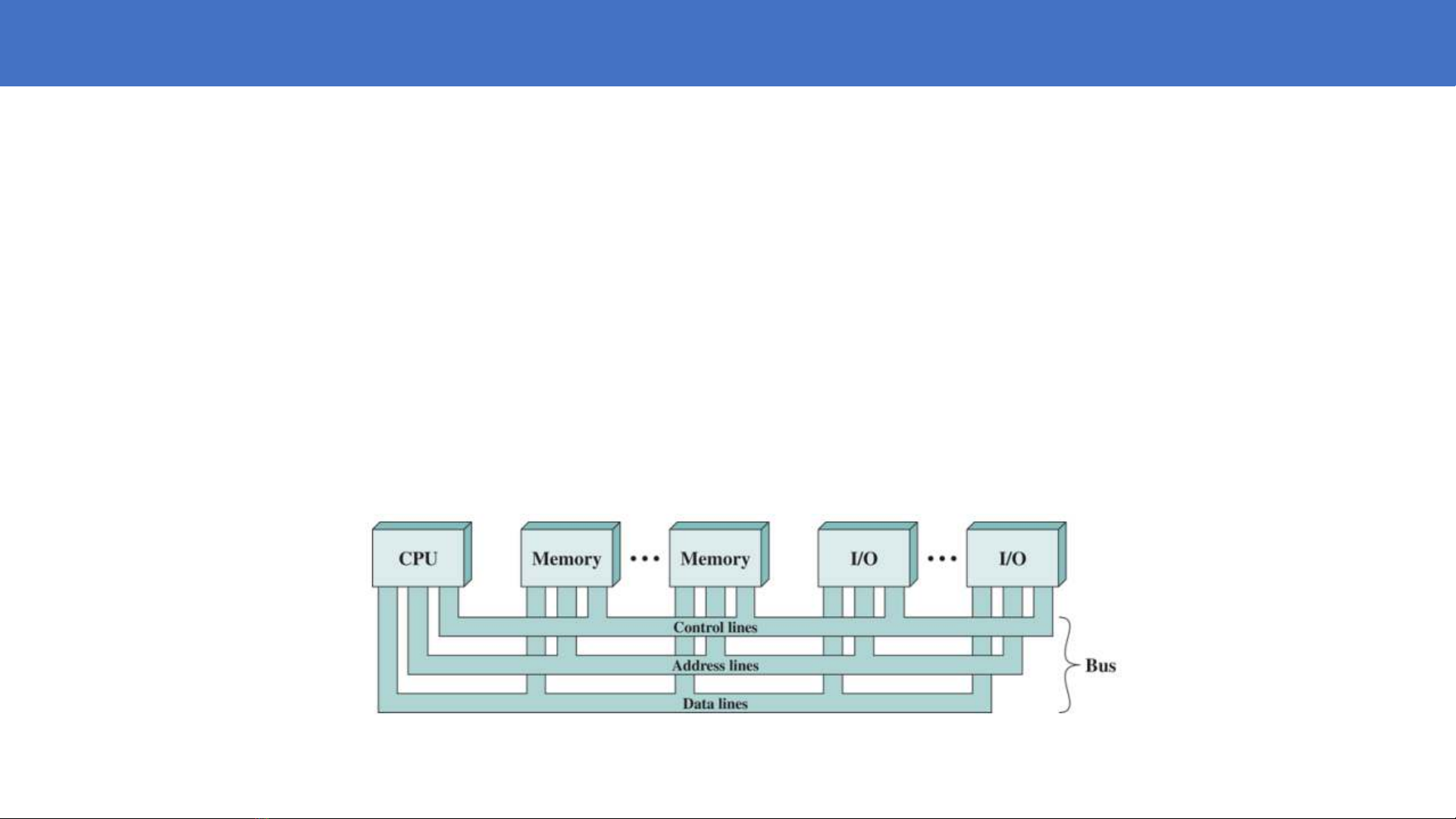

HỆ THỐNG ĐƠN BUS

•Có nhiều thành phần nối vào bus chung, một số thiết bị tích tực (active) có thể đòi hỏi truyền thông

trên bus, một số các thiết bị thụ động chờ yêu cầu từ các thiết bị khác ➔Các thiết bị tích cực được

gọi là chủ (master) còn thiết bị thụ động là tớ (slave).

•Phân loại các dây dẫn:

oDây dẫn dữ liệu: Data line.

oDây dẫn địa chỉ: Address line.

oDây dẫn điều khiển: Control line.

Sơ đồ kết nối Bus

HỆ THỐNG ĐƠN BUS

Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

•Tại một thời điểm chỉ phục vụ được một yêu cầu trao đổi dữ liệu.

•Các thành phần nối vào Bus có thể có tốc độ khác nhau.

•Các Module nhớ và Module IO phụ thuộc vào cấu trúc của CPU.

•Khắc phục:

oXây dựng cấu trúc đa Bus bao gồm các hệ thống Bus khác nhau về tốc độ.

oTrong hầu hết các máy PC bus được phân thành 3 cấp và các bus nối với nhau

thông qua cầu nối Bus.