Thi t k logic s ế ế ố

(VLSI design)

B môn KT Xung, s , VXLộ ố

quangkien82@gmail.com

https://sites.google.com/site/bmvixuly/thiet-ke-

logic-so

08/2012

•N i dungộ: Ki n trúc ki u c u trúc, Mô ế ể ấ

ph ng trên ModelSim, Đ i t ng d li u, ỏ ố ượ ữ ệ

ki u d li uể ữ ệ

•Th i l ngờ ượ : 3 ti t bài gi ngế ả

2/15

Ch ng II: Ngôn ng VHDL ươ ữ quangkien82@gmail.com

M c đích, n i dungụ ộ

3/15

Ch ng II: Ngôn ng VHDL ươ ữ quangkien82@gmail.com

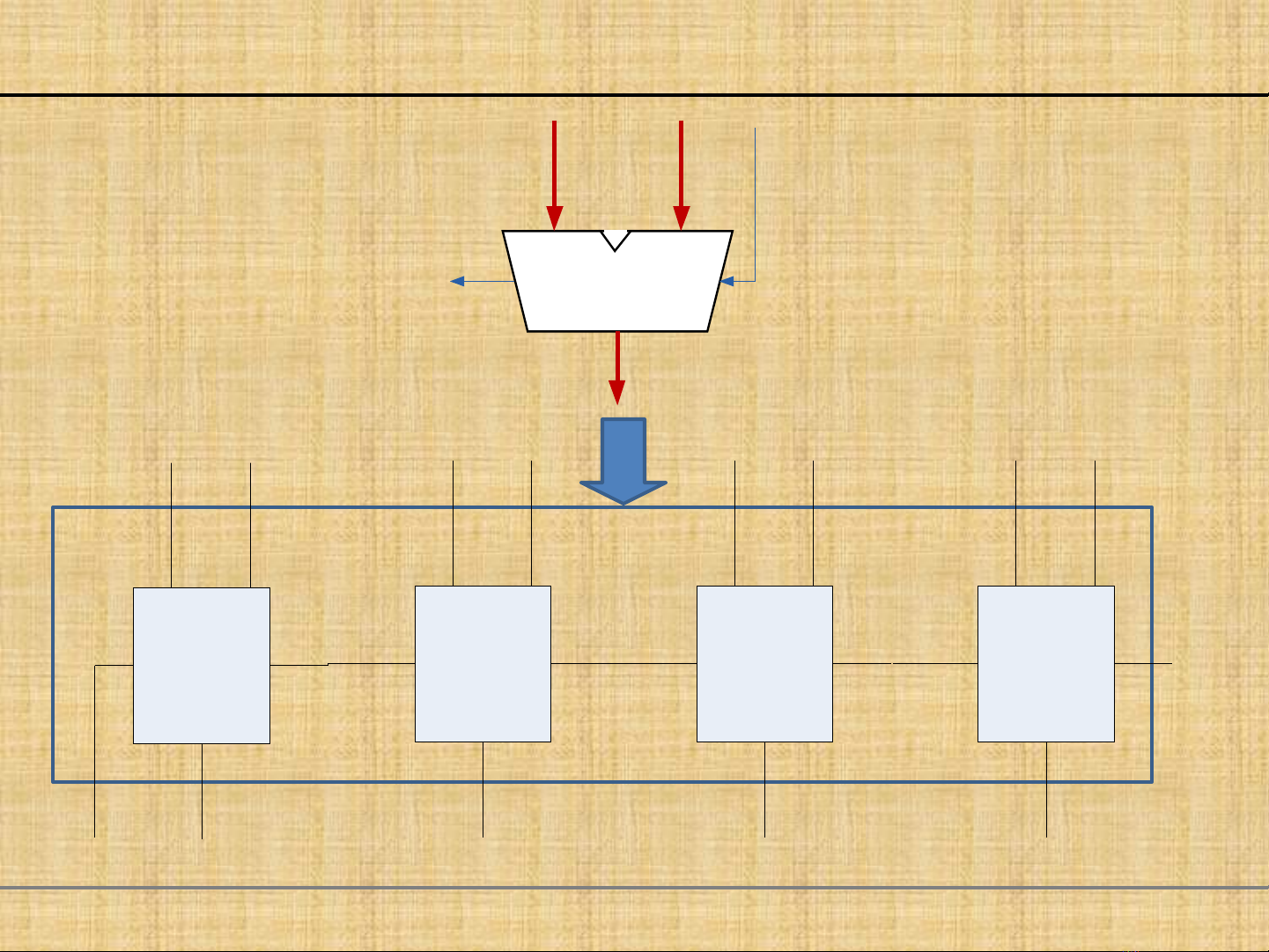

Adder 4 bit

Σ

ABCin

Cout

Sum

4 4

4

FULL_ADDER

b0 a0

CI

S0

FULL_ADDER

b3 a3

C(2)

S3

FULL_ADDER

b2 a2

C(1)

S2

FULL_ADDER

b1 a1

C(0)

S1

CO

M t th c th có bao nhiêu ki n trúc ?ộ ự ể ế

Ki n trúc nào đ c biên d ch vào th vi n Work?ế ượ ị ư ệ

Ki n trúc nào s đ c mô ph ng b ng l nh Vsim?ế ẽ ượ ỏ ằ ệ

4/15

Ch ng II: Ngôn ng VHDL ươ ữ quangkien82@gmail.com

Configuration

ADDER4 = 4 Full_adder

Behavioral

Dataflow

configuration behav of adder4 is

for structure -- one of architecture

for all: full_adder

use entity work.full_adder(behavioral);

end for;

end for;

end configuration;

-- select architecture

for u0: full_adder use entity work.full_adder(behavioral);

for u1: full_adder use entity work.full_adder(behavioral);

for u2: full_adder use entity work.full_adder(dataflow);

for u3: full_adder use entity work.full_adder(dataflow);

?

5/15

Ch ng II: Ngôn ng VHDL ươ ữ quangkien82@gmail.com

Configuration

![Bài giảng Nhập môn mạch số: Chương 3 (Phần 2) - TS. Trịnh Lê Huy [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/38491750824827.jpg)

![Giáo trình Trang bị điện nước (TC) - Trường Cao đẳng Công nghiệp Thanh Hóa [Ngành Điện nước]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260511/hoatrami2026/135x160/14221778681890.jpg)