Kỹ

Kỹ thuật

thuậtVi

Vi xử lý

xử lý

Điện tử

Điện tử-

-Viễn thông

Viễn thông

Đại học Bách khoa Đà Nẵng

Đại học Bách khoa Đà Nẵng

Chương

Chương 4

4

4.1

4.1 Phân loại bộ nhớ bán dẫn

Phân loại bộ nhớ bán dẫn

4.2

4.2 Hoạt động của các

Hoạt động của các chip EPROM

chip EPROM

4.3

4.3 Hoạt động của các

Hoạt động của các chip SRAM

chip SRAM

4.4 Bus

4.4 Bus hệ thống của hệ

hệ thống của hệvi

vi xử lý

xử lý 8088

8088

4.5

4.5 Bài toán thiết kế bộ nhớ

Bài toán thiết kế bộ nhớ

M

Mục tiêu và biện pháp thiết kế

ục tiêu và biện pháp thiết kế

Ghép nối các

Ghép nối các chip

chip nhớ

nhớEPROM

EPROM và

và SRAM

SRAM

với

vớiBus

Bus hệ thống sao cho không xảy ra

hệ thống sao cho không xảy ra

xung đột

xung đột:

:

Các

Các chip

chip nhớ bị cấm khi

nhớ bị cấm khi vi

vi xử lý truy cập

xử lý truy cập

các cổng

các cổng I/O

I/O

Chỉ có một

Chỉ có mộtchip

chip nhớ hoạt động khi

nhớ hoạt động khi vi

vi xử lý

xử lý

truy cập bộ nhớ

truy cập bộ nhớ

Thực hiện một mạch giải mã địa chỉ bộ

Thực hiện một mạch giải mã địa chỉ bộ

nhớ dùng các

nhớ dùng các chip

chip giải mã hoặc các cổng

giải mã hoặc các cổng

logic

logic hoặc kết hợp cả hai

hoặc kết hợp cả hai

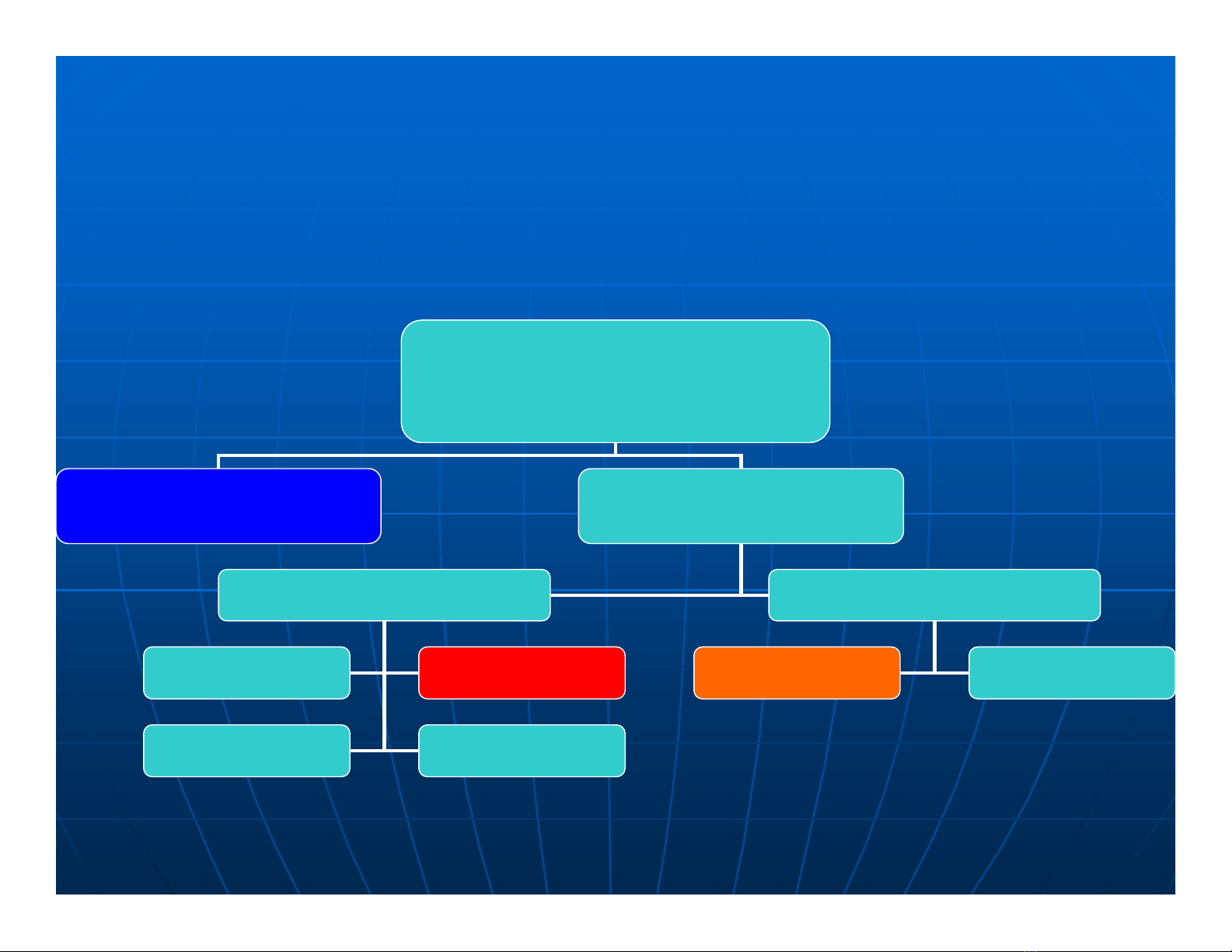

4.1

4.1 Phân loại bộ nhớ bán dẫn

Phân loại bộ nhớ bán dẫn

Bộnhớ bán dẫn

(Semiconductor memory)

SAM

(Sequential Access Memory)

RAM

(Random Access Memory)

ROM (Read Only Memory)RWM (Read Write memory)

PROM EPROM

EEPROM Flash ROM

SRAM DRAM

4.2

4.2 Các

Các chip EPROM

chip EPROM

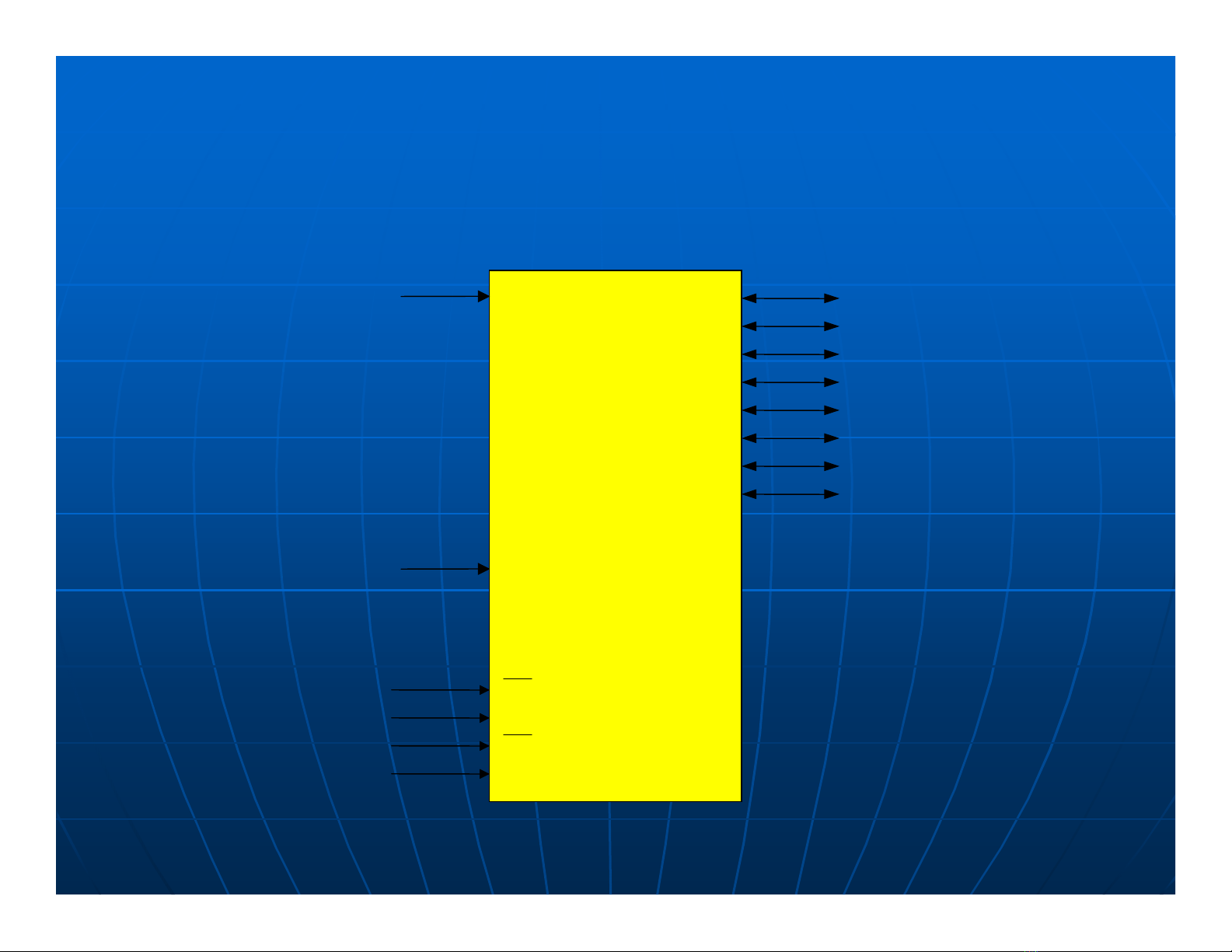

EPROM

A0

A1

A2

A3

A4

A5

A6

A7

A8

Ap-1

Vpp

D0

D1

D2

D3

D4

D5

D6

D

m-1

CE

OE

PGM

pchân địa chỉ

Các chân điều khiển

m chân dữ liệu

Điều khiển đọc

Chọnchip

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)