PH N M Đ UẦ Ở Ầ

1. LÝ DO CH N Đ TÀIỌ Ề

Ngày nay, khoa h c k thu t phát tri n hi n đ i. H th ng thi t b đi n t ,ọ ỹ ậ ể ệ ạ ệ ố ế ị ệ ử

m ch đi n t , k thu t đi n t -s ra đ i đã làm thay đ i sâu s c toàn b ho t đ ngạ ệ ử ỹ ậ ệ ử ố ờ ổ ắ ộ ạ ộ

s n xu t c a con ng i. K thu t đi n t -s đã và đang đ c thay th d n k thu tả ấ ủ ườ ỹ ậ ệ ử ố ượ ế ầ ỹ ậ

t ng t , và nó đóng m t vai trò then ch t trong cu c cách m ng khoa h c k thu tươ ự ộ ố ộ ạ ọ ỹ ậ

và công ngh . Song song v i s phát tri n th n kì cu c cách m ng khoa h c-côngệ ớ ự ể ầ ộ ạ ọ

ngh , k thu t s đã d n d n có m t h u h t t t c các thi t b t thi t b dânệ ỹ ậ ố ầ ầ ặ ở ầ ế ấ ả ế ị ừ ế ị

d ng đ n thi t b công nghi p, đ c bi t là trong lĩnh v c thông tin liên l c, phát thanhụ ế ế ị ệ ặ ệ ự ạ

truy n hình, t đ ng đi u khi n… Nó gi i quy t đ c kh i l ng công vi c l n,ề ự ộ ề ể ả ế ượ ố ượ ệ ớ

gi m kích th c c a các m ch đi n t đ ng th i chúng có ả ướ ủ ạ ệ ử ồ ờ nhi u tính năng h n và đề ơ ộ

chính xác cao h n nhi uơ ề . Có th nói r ng k thu t s ra đ i là cu c cách m ng trongể ằ ỹ ậ ố ờ ộ ạ

ngành k thu t đi n t . ỹ ậ ệ ử

Th k 21 ch ng hi n s phát tri n v i t c đ chóng m t c a khoa h c-côngế ỷ ứ ế ự ể ớ ố ộ ặ ủ ọ

ngh , nó đóng vai trò then ch t trên t t c các lĩnh v c c a cu c s ng vì v y m iệ ố ấ ả ự ủ ộ ố ậ ỗ

m t chúng ta, đ c bi t là th h tr , sinh viên ngành k thu t khi s ng trong th kộ ặ ệ ế ệ ẻ ỹ ậ ố ế ỷ

m i này, c n ph i hi u rõ và có ki n th c v k thu t s . Do đó tôi ch n đ tài “Tìmớ ầ ả ể ế ứ ề ỹ ậ ố ọ ề

hi u v b ghi d ch và IC có ch c năng liên quan” làm đ tài bài t p l n.ể ề ộ ị ứ ề ậ ớ

2. M C TIÊU Đ TÀIỤ Ề

- Sinh viên b c đ u tìm hi u v nghiên c u khoa h c.ướ ầ ể ề ứ ọ

- Hi u đ c m ch logic t h p.ể ượ ạ ổ ợ

- N m v ng ki n th c v b ghi d ch.ắ ữ ế ứ ề ộ ị

- Phân tích đ c IC có ch c năng t ng t .ượ ứ ươ ự

3. NHI M V Đ TÀIỆ Ụ Ề

- Trình bày v flipflop.ề

- Tìm hi u v b ghi d ch.ể ề ộ ị

- Nghiên c u v IC có ch c năng liên quan.ứ ề ứ

1

4. PH NG PHÁP NGHIÊN C UƯƠ Ứ

- Ph ng pháp lý thuy t : ươ ế

+ S u t m tài li u, sách tham kh o, internet... ư ầ ệ ả

+ Tìm ki m các IC có ch c năng nh m ch đ c giao.ế ứ ư ạ ượ

5 GI I H N Đ TÀIỚ Ạ Ề

- Nghiên c u v n đ trên c s lý thuy t.ứ ấ ề ơ ở ế

- Flip flop và b ghi d ch.ộ ị

- IC 74HC595A

6. B C C BÀI T P L NỐ Ụ Ậ Ớ

- Ch ng 1: Tìm hi u v Flip Flopươ ể ề

- Ch ng 2: Gi i thi u v b ghi d chươ ớ ệ ề ộ ị

- Ch ng 3: Tìm hi u v IC có ch c năng liên quan “IC 74HC595A”.ươ ể ề ứ

2

PH N N I DUNGẦ Ộ

CH NG 1ƯƠ

TÌM HI U V FLIP FLOPỂ Ề

1.1 Đ NH NGHĨAỊ

Trig trong ti ng anh g i là Flip-Flop vi t t t là FF. Nó là m t ph n t nh có 2ơ ế ọ ế ắ ộ ầ ử ớ

tr ng thái cân b ng n đ nh t ng ng v i 2 m c logic 0 và 1. D i tác d ng c a cácạ ằ ổ ị ươ ứ ớ ứ ướ ụ ủ

tín hi u đi u khi n l i vào, trig có th chuy n v m t trong hai tr ng thái cânệ ề ể ở ố ơ ể ể ề ộ ạ

b ng, và gi nguyên tr ng thái đó ch ng nào ch a có tín hi u đi u khi n làm thayằ ữ ạ ừ ư ệ ề ể

đ i tr ng thái c a nóổ ạ ủ .

1.2 PHÂN LO I Ạ

- Theo ch c năngứ+ RS-FF

+ D-FF

+ T-FF

- Theo cách làm vi cệ+ Không đ ng bồ ộ

+ Đ ng bồ ộ • Bình th ngườ

• Ch -tủ ớ

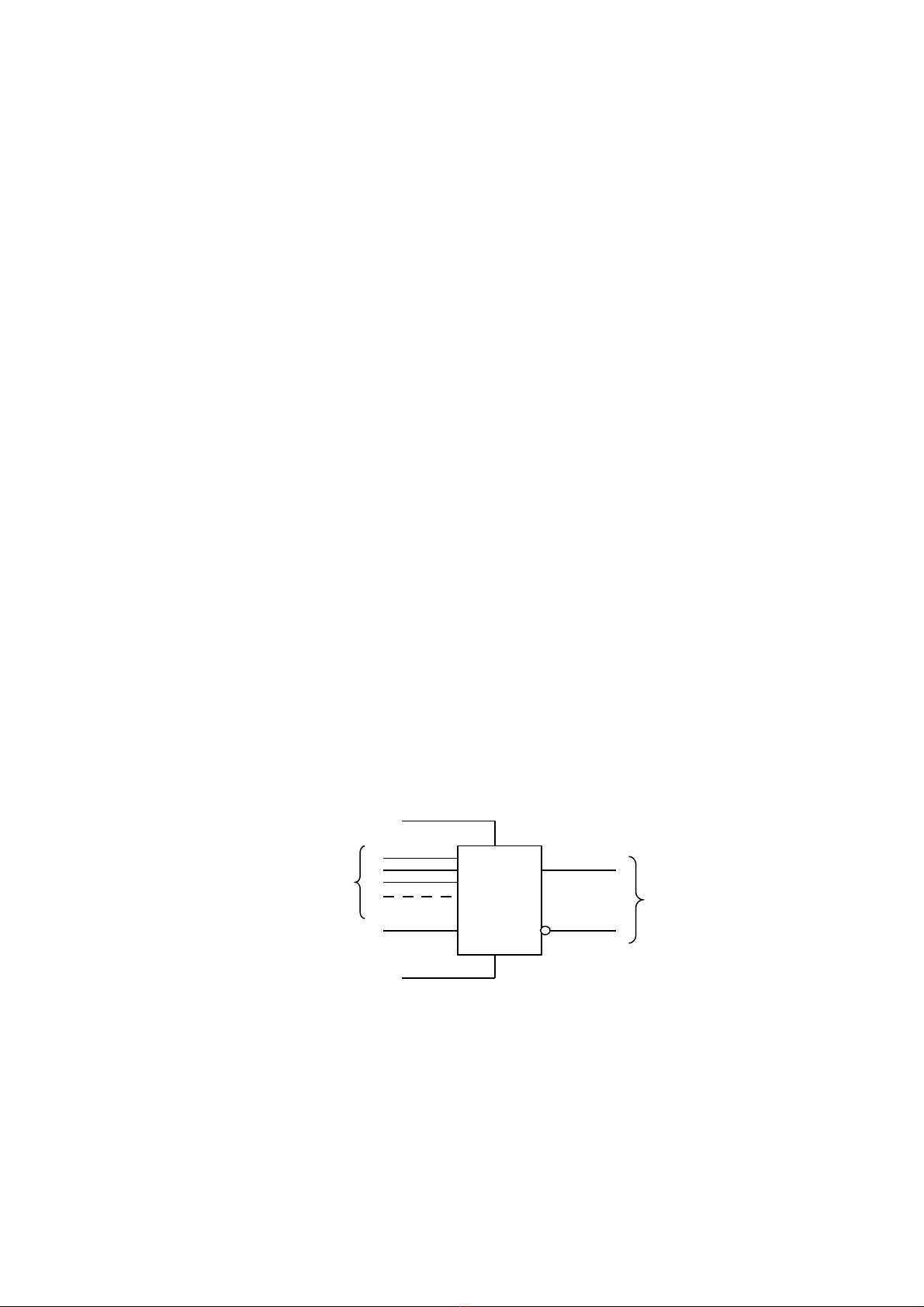

1.3 KÝ HI UỆ

Hình 1.1: Ký hi u c a flip flopệ ủ

- Vi m ch có th có 1, 2 ho c nhi u l i vào đi u khi nạ ể ặ ề ố ề ể

- Chân CLK có th có ho c khôngể ặ

- Pr (preset) có th có ho c khôngể ặ

3

Q

Flip

Fop

CLR

CLK

Đ uầ vào

Pr

Đ uầ ra

-Q và

Q

có 2 l i ra và luôn luôn có giá tr ng c nhauố ị ượ

- Tùy t ng lo i FF do ch t o có th còn có đ u vào xóa (thi t l p 0), đ u vàoừ ạ ế ạ ể ầ ế ậ ầ

thi t l p (thi t l p 1), đ u vào đ ng b (CLK).ế ậ ế ậ ầ ồ ộ

1.4 CH C NĂNGỨ

Flip-flop và ch t đ c s d ng nh các y u t l u tr d li uố ượ ử ụ ư ế ố ư ữ ữ ệ

- Có th l u tr 2 tr ng thái 0 ho c 1 (nh ).ể ư ữ ạ ặ ớ

- Có kh năng ti p nh n (ghi vào), l u tr trong m t th i gian tùy theo yêu c uả ế ậ ư ữ ộ ờ ầ

và xu t ra (đ c ra) m t tr ng thái (1 bit) nh phân đang đ c l u tr trong FF.ấ ọ ộ ạ ị ượ ư ữ

- Vi c m r ng các ch c năng c a FF s đ c th c hi n nh có các đ u vàoệ ở ộ ứ ủ ẽ ượ ự ệ ờ ầ

đi u khi n hành vi c a FF ngoài các đ u vào tín hi u đã nói t i (xóa tín hi u đangề ể ủ ầ ệ ớ ệ

l u, cho phép ghi hay đ c ...).ư ọ

1.5. CÁC LO I FLIP FLOPẠ

1.5.1. Flip Flop RS

1.5.1.1 S đ kh iơ ồ ố

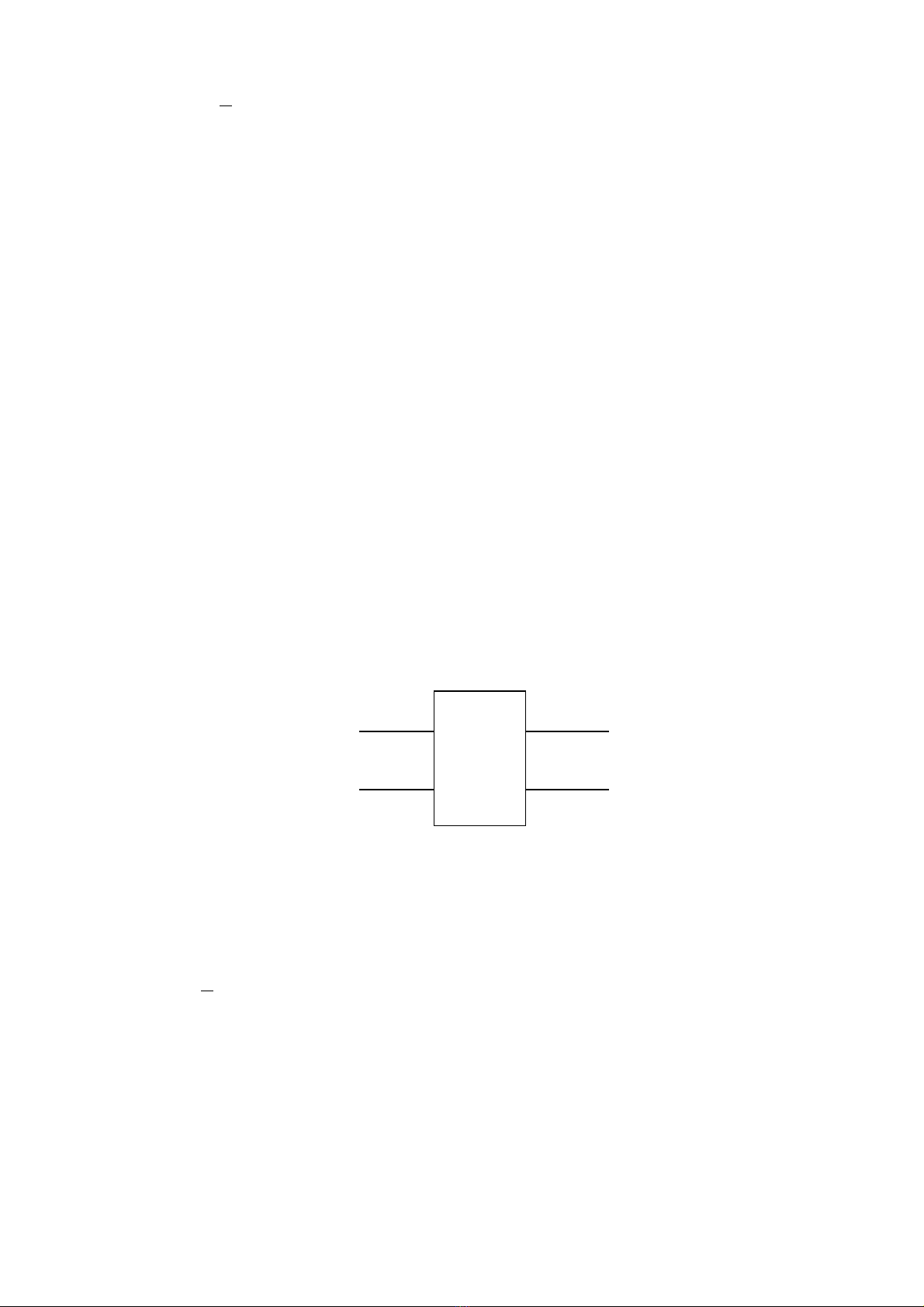

Hình 1.2: Ký hi u RS-FFệ

Flip Flop RS (RS-FF) là m t ph n t nh c b n có 2 tr ng thái cân b ng b nộ ầ ử ớ ơ ả ạ ằ ề

v ng, nó có 2 l i vào R, S và 2 l i ra Q và .Q và luôn ng c nhauữ ố ố ượ

Q,

Q

là 2 l i ra c a FF.ố ủ

1.5.1.2 . B ng s th tả ự ậ

4

RS-FF

Q

S

R

SnRnQn+1 M t ho t đ ngố ạ ộ

0 0 QnNhớ

1 0 1 Xác l pậ

0 1 0 Xóa

1 1 Không cho phép C m dùngấ

B ng 1.1ả: B ng s th t c a RS-FFả ự ậ ủ

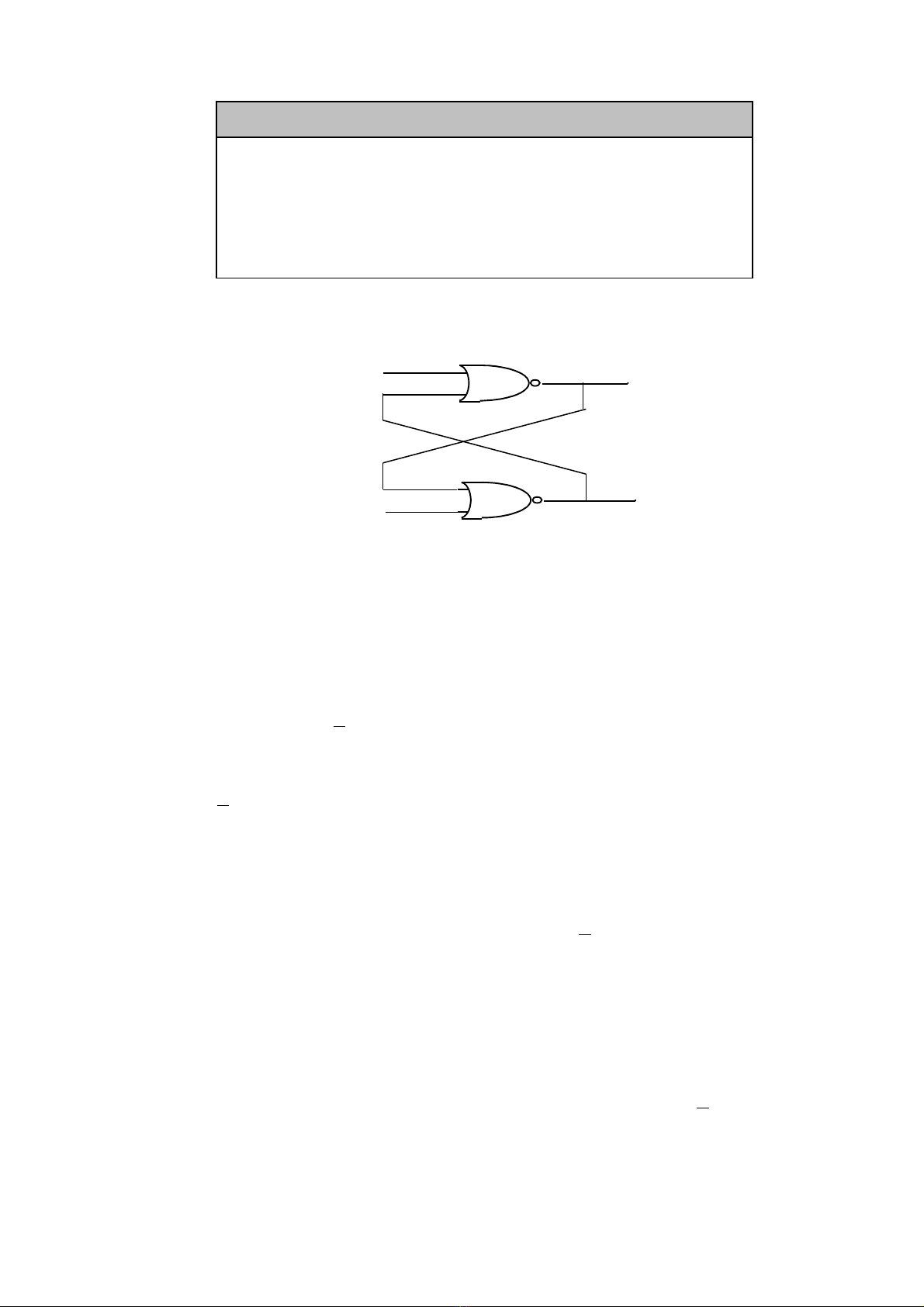

1.5.1.3 S đ logicơ ồ

Hình 1.3: S đ logic c a RS-FFơ ồ ủ

1.5.1.4 Nguyên t c ho t đ ng ắ ạ ộ

- Khi S = 0, R = 0: L i ra v n gi tr ng thái cũ Qố ẫ ữ ạ n : Tr ng thái nh .ạ ớ

N u tr ng thái ban đ u Qế ạ ầ n = 0, c 2 l i vào c a c a logic NOR I đ u b ngả ố ủ ử ề ằ

0 nên l i ra c a nó là ố ủ

Q

= 1 và l i ra c a NOR II là Q = 0 trùng v i tr ng tháiố ủ ớ ạ

ban đ u tr c đó. T c là đã nh tr ng thái Q = 0. N u tr ng thái ban đ u Qầ ướ ứ ớ ạ ế ạ ầ n = 1

thì l i ra ố

Q

= 0 và l i ra c a NOR II là Q = 1 trùng v i tr ng thái ban đ u tr cố ủ ớ ạ ầ ướ

đó. T c Q = 1.ứ

- Khi S = 0, R = 0: L i ra Qn = 1: Tr ng thái xác l p.ố ạ ậ

N u lúc kh i đ u Sn = 1, Rn = 0 l i ra NOR I là ế ở ầ ố

Q

= 0, c 2 l i vào c a NOR IIả ố ủ

đ u b ng 0 nên l i ra Q c a nó tr ng thái k t thúc Qn+1 = 1: Tr ng thái xác l p.ề ằ ố ủ ở ạ ế ạ ậ

- Khi S = 0, R = 1: L i ra Qn+1 = 0: Tr ng thái xóa.ố ạ

N u lúc kh i đ u Sn = 0, Rn = 1, m ch logic NOR II có m t l i vào Rn = 1 nênế ở ầ ạ ộ ố

l i ra c a nó Q = 0, c hai l i vào c a NOR I đ u b ng 0 nên l i ra ố ủ ả ố ủ ề ằ ố

Q

= 1, v y tr ngậ ạ

thái k t thúc c a FF Qn+1 = 0 ng v i tr ng thái xóa c a FF.ế ủ ứ ớ ạ ủ

5

Q

R

S I

II

![Báo cáo thực tập tốt nghiệp Công ty TNHH Cơ điện Samwa Tek: [Mô tả chi tiết hơn về nội dung báo cáo nếu có thể]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250917/trantiendat_ct2/135x160/96461758161119.jpg)

![Báo cáo thực tập tại Garage Car Plus [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250810/nguyenanhquoc2809@gmail.com/135x160/25661754896300.jpg)

![Đồ án tốt nghiệp: Tính toán, kiểm tra hệ thống điều hòa không khí cho tòa nhà Depot Tham Lương [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250717/vijiraiya/135x160/40421752722146.jpg)

![Hệ thống điều khiển nhà thông minh: Luận văn tốt nghiệp [Chuẩn SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260423/hoacattuong2026/135x160/35121777429487.jpg)