Điện tử cơ bảnĐiện tử cơ bản

Ch 6.Transistor trường ứng( FETCh 6.Transistor trường ứng( FET))

I. Đại cương và phân loạiI. Đại cương và phân loại

• FET ( Field Effect Transistor)-Transistor

hiệu ứng trường –Transistor trường.

•Có 2 loại:

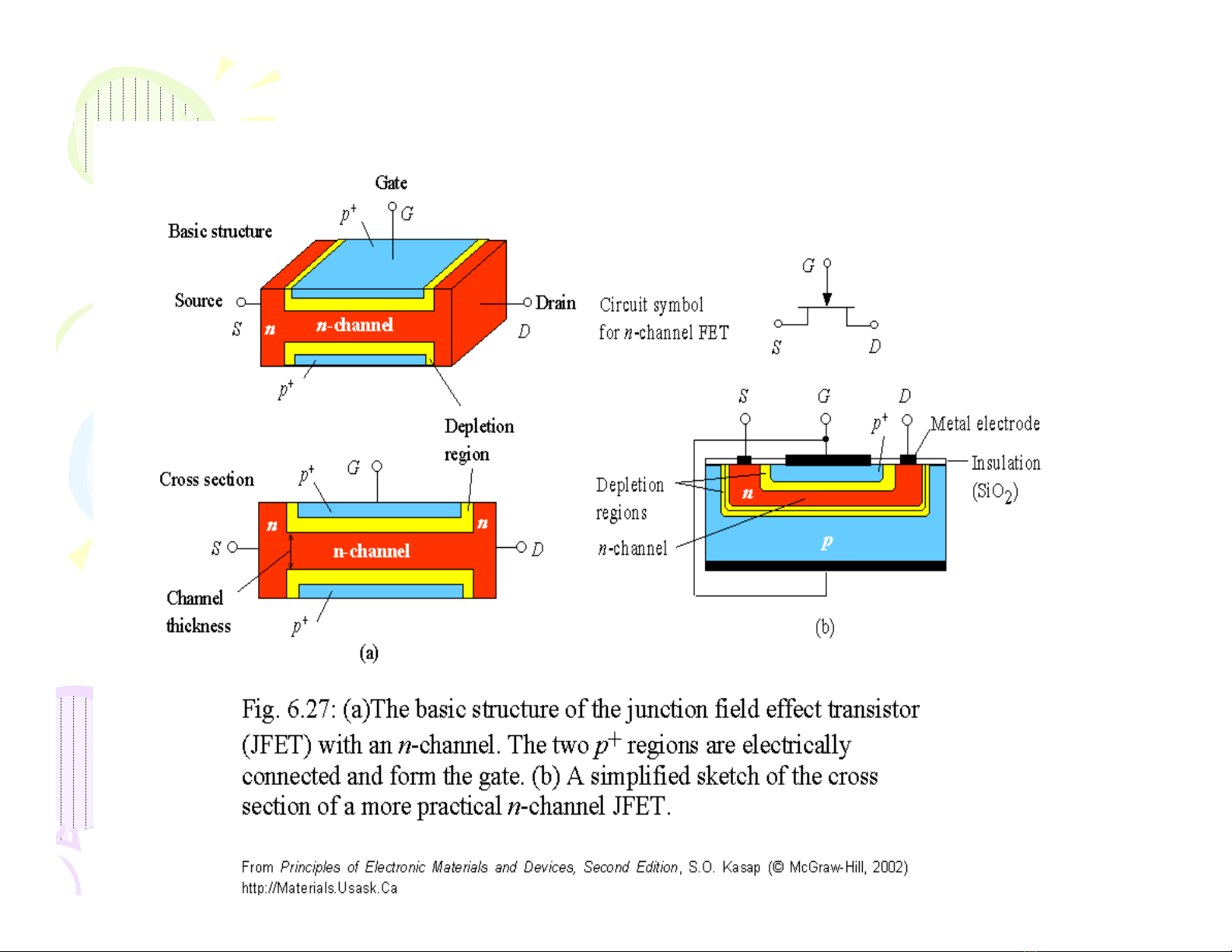

-Transistor trường nối (JFET-Junction

FET.

-Transistor có cổng cách điện ( IGFET-

Insulated Gate FET hay MOSFET – Metal

Oxide Semiconductor : Kim loại- oxid-

bán

dẫn)

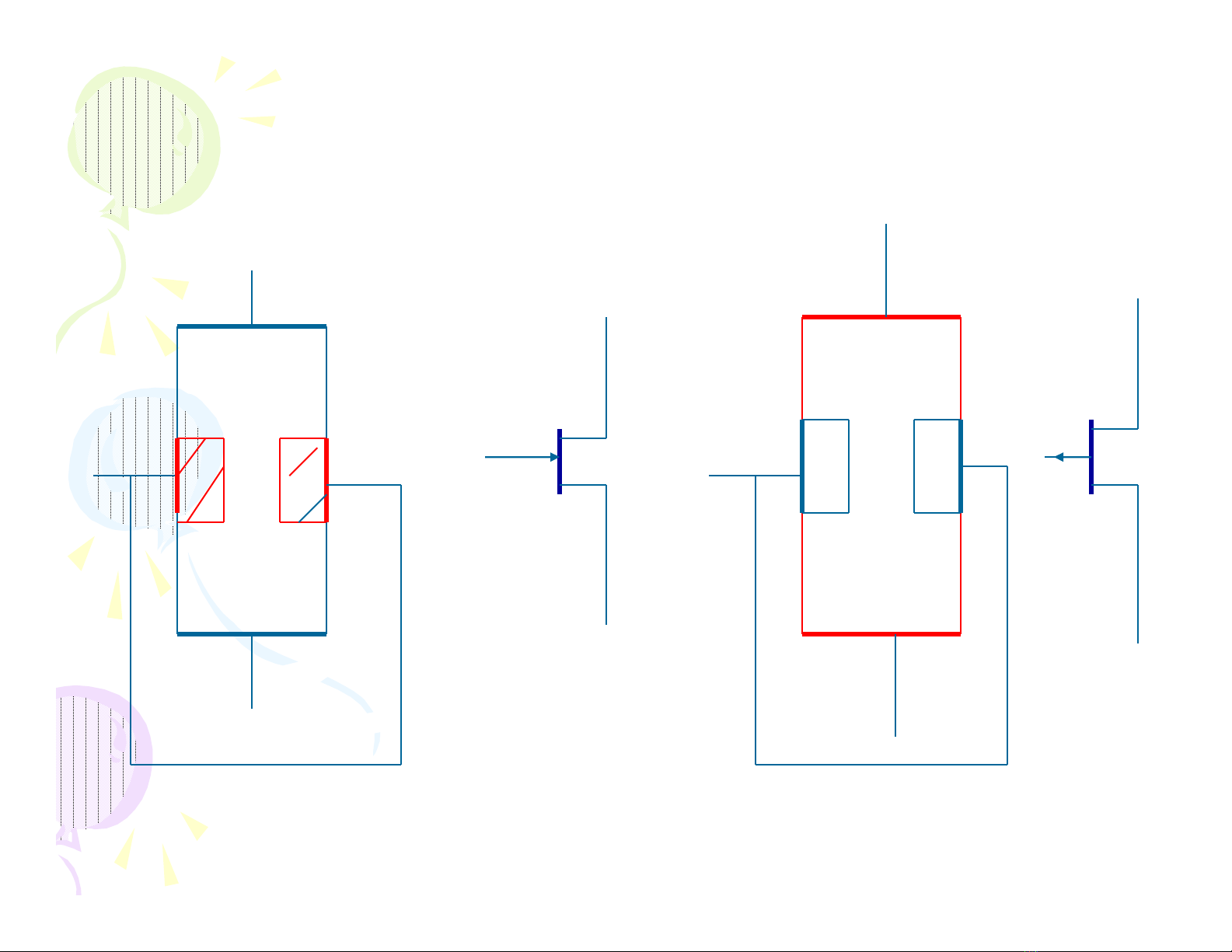

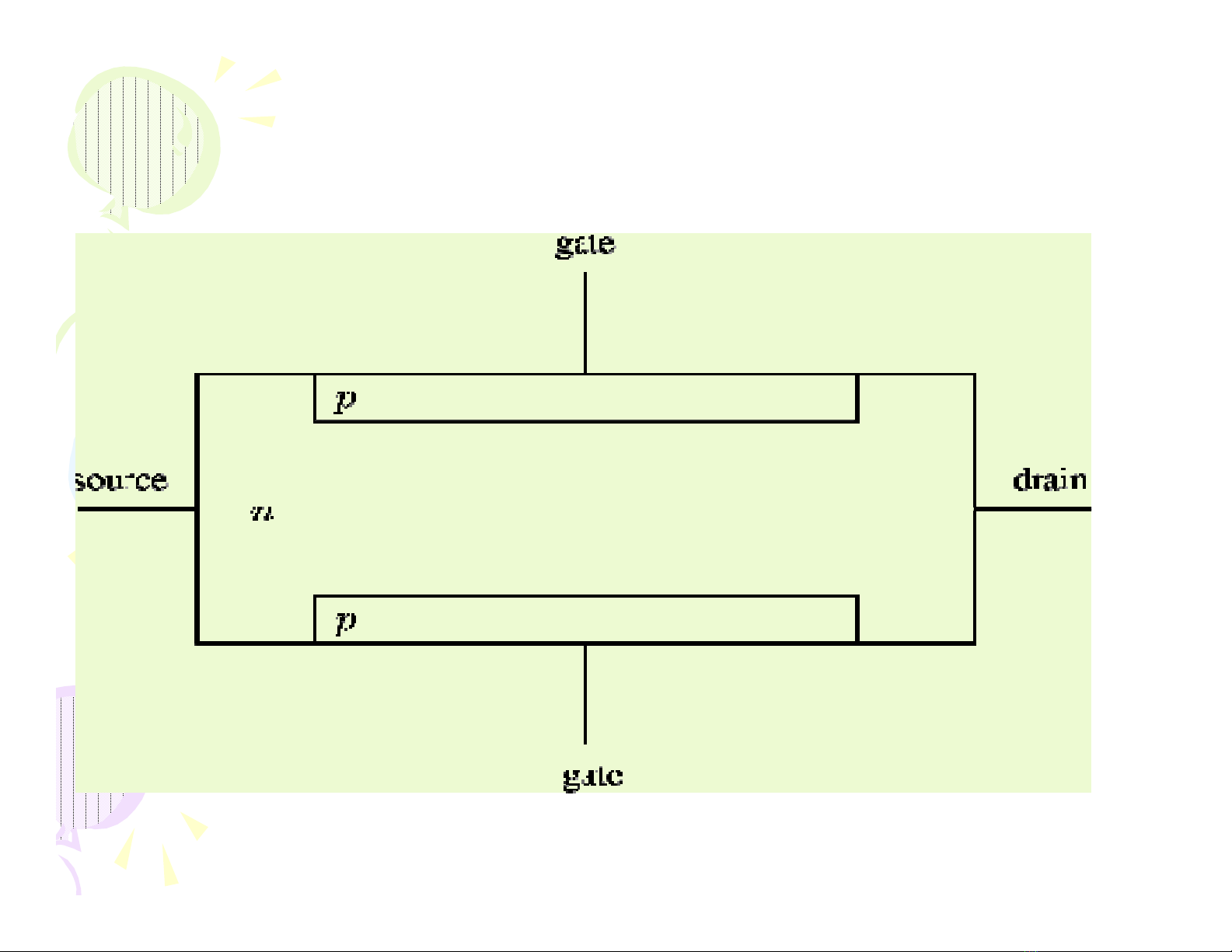

I. JFETI. JFET

1.Cấu tạo

D D

D D

G G G G

p p n n

n p

S S

S S

kênh n kênh p

• JFET

• JFET kênh n

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)