Tài liu môn hc: Ghép ni và ñiu khin thit b ngoi vi

Ging viên: Nguyn Văn Minh Trí 59

CHƯƠNG 5: GHÉP NI VÀO RA ðIU KHIN BNG DMA

5.1 Khái nim DMA cơ b$n

5.1.1 Khái nim DMA

Phương pháp trao ñ%i d liu theo chương trình s, chm do:

- VXL phi gii mã và thc hin lnh

- Trao ñ%i d liu t(ng byte thông qua thanh cha AX c"a VXL.

K$ thut vào ra DMA (direct memory access) là phương pháp truy cp trc tip t!i b

nh! hoc I/O mà không có s tham gia c"a CPU. Phương pháp này trao ñ%i d liu gia

b nh! và thit b ngoi vi v!i tc ñ cao và ch& b hn ch bi tc ñ c"a b nh! hoc

c"a b ñiu khin DMA. Tc ñ truyn DMA có th ñt t!i 10 ÷ 12 Kbyte/s v!i các b

nh! RAM có tc ñ cao. DMA ñưc ng dng trong nhiu mc ñích nhưng thông thưng

nó ñưc dùng trong quá trình "refresh" DRAM, xut màn hình, ñc ghi ñĩa, truyn d

liu gia các vùng nh! v!i tc ñ cao .

5.1.2 Hot ñng DMAC (DMA Controller) cơ bn

Hai tín hiu ñ yêu cu và xác nhn trong h thng VXL là HOLD ñưc s dng ñ yêu

cu DMA và HLDA là ñu ra xác nhn DMA. Khi tín hiu HOLD hot ñng (HOLD =

1), DMA ñưc yêu cu. B VXL tr li b#ng cách kích hot tín hiu HLDA, xác nhn

yêu cu, ñ'ng thi th n%i các công vic hin thi cùng các bus d liu và ña ch&, ñiu

khin ñưc ñt trng thái tr kháng cao. Trng thái này cho phép các thit b I/O bên

ngoài hoc các b VXL khác nm quyn ñiu khin bus h thng ñ truy cp trc tip b

nh! . Tín hiu HOLD có mc ưu tiên cao hơn INTR hoc ñu vào NMI (ngt không che

ñưc) và ch& sau RESET. Tín hiu HOLD luôn có hiu lc ti bt kỳ thi ñim nào trong

sut quá trình thc hin các lnh khác c"a VXL. Chú ý r#ng t( lúc tín hiu HOLD thay

ñ%i cho ñn khi tín hiu HLDA thay ñ%i ñã tri qua mt s chu kỳ clock .

DMA thưng ñưc thc hin gia thit b I/O và b nh!. Quá trình ñc DMA là quá trình

ñưa d liu t( b nh! ra thit b I/O, và ngưc li quá trình ghi DMA là quá trình ñưa d

liu t( I/O t!i b nh!. Trong c hai chu trình này thit b I/O và b nh! ñưc ñiu khin

ñ'ng thi d4n ñn cn có các tín hiu ñiu khin khác nhau. Ð ñiu khin quá trình ñc

DMA ta cn hai tín hiu hot ñng MEMR (ñc b nh! ) và IOW (ghi I/O). Ð ñiu

khin quá trình ghi ta có hai tín hiu MEMW (ghi b b nh!) và IOR (ñc I/O). B ñiu

khin DMA cung cp ña ch& b nh! và tín hiu chn thit b I/O cho 8088 trong sut quá

trình DMA. Do tc ñ truyn DMA ph thuc vào tc ñ c"a b nh! và tc ñ c"a b

ñiu khin DMA nên trong trưng hp tc ñ c"a b ñiu khin DMA nh- hơn so v!i b

nh! thì b ñiu khin DMA s, làm gim tc ñ chung c"a h thng .

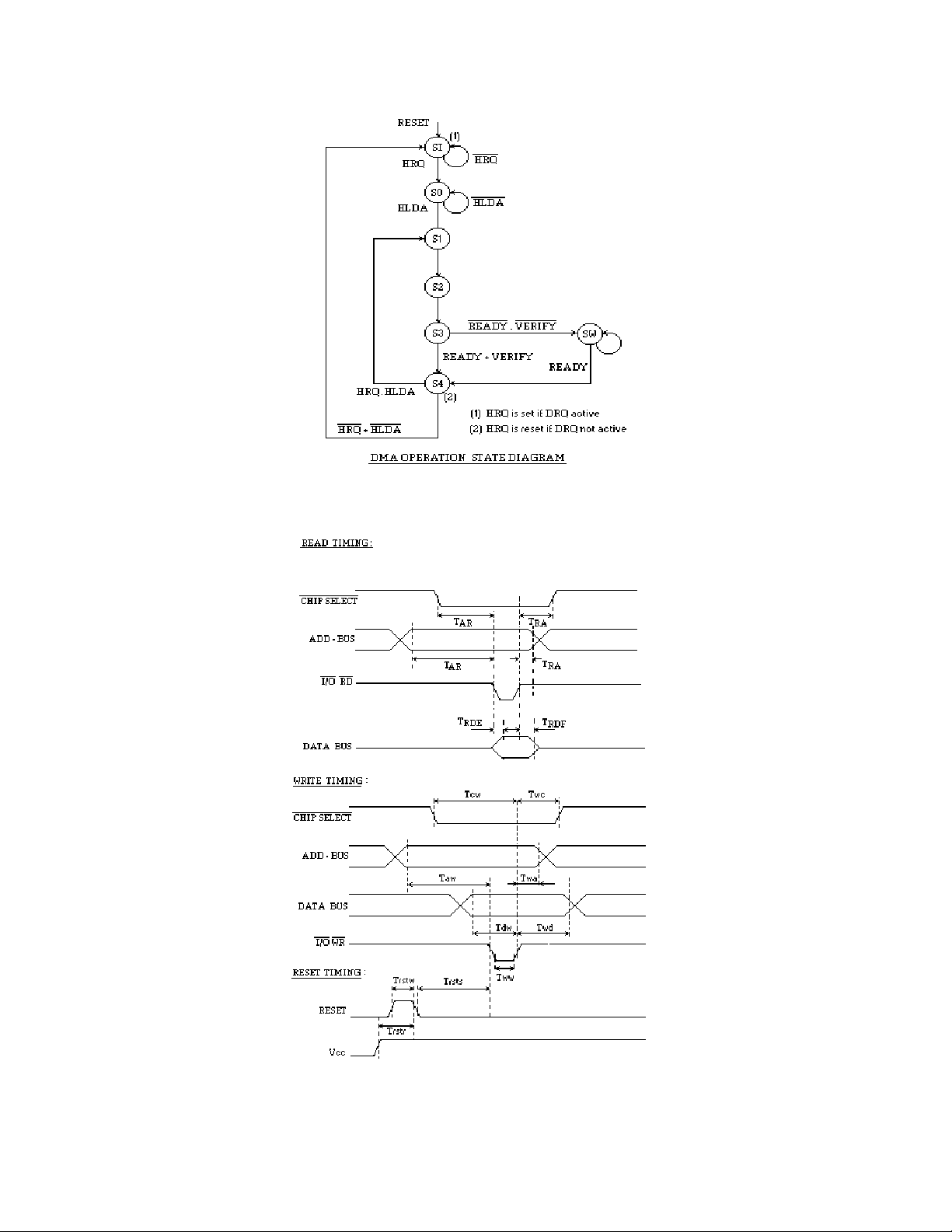

Hình v, sau minh ho quá trình hot ñng DMA cơ bn cùng ñ' th thi gian ñc / ghi

DMA :

Tài liu môn hc: Ghép ni và ñiu khin thit b ngoi vi

Ging viên: Nguyn Văn Minh Trí 60

Ð' th thi gian ñc / ghi DMA .

Tài liu môn hc: Ghép ni và ñiu khin thit b ngoi vi

Ging viên: Nguyn Văn Minh Trí 61

5.1.3. Các ch ñ trao ñi d liu DMA

+ Trao ñ%i d liu theo khi: trao ñ%i nhiu li d liu, ñm t( giá tr n ñn 0.

+ Trao ñ%i ly lén chu kỳ t(ng phn: DMA phát hin data bus r2i, r'i thc hin trao

ñ%i d liu DMA.

DMAC phi có:

- Thit b phát hin ñưng dây r2i

- Thit b bo ñm VXL b treo cho t!i khi DMAC không s dng ñưng dây,

khin VXL ch mt thi gian Tw

t!i khi DMAC thc hin trao ñ%i xong trong

mt phn c"a trao ñ%i d liu và tip tc nt phn ly lén chu kỳ sau cho t!i

khi kt thúc trao ñ%i c t( d liu DMA.

+ Trao ñ%i ly lén chu kỳ trong sut: ging ch ñ trên, nhưng DMA bt VXL ch t!i

khi trao ñ%i xong mt t( d liu trn v5n.

Tài liu môn hc: Ghép ni và ñiu khin thit b ngoi vi

Ging viên: Nguyn Văn Minh Trí 62

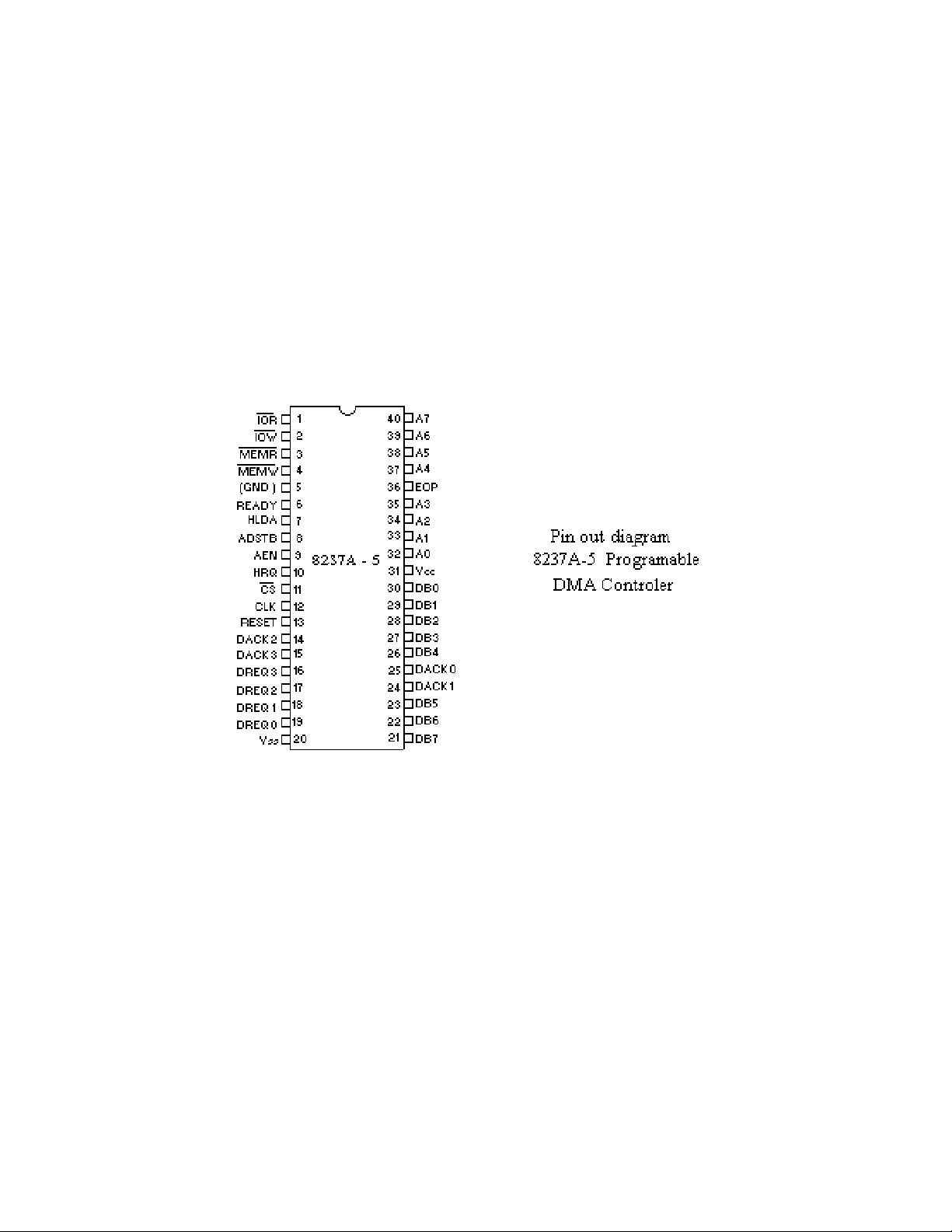

5.2 B! ñi-u khi.n DMA – 8237A

Vi mch 8237A là mt b ñiu khin DMA cung cp ña ch& b nh! và tín hiu ñiu

khin trong sut quá trình DMA và truyn s liu v!i tc ñ cao gia b nh! và thit b

vào ra. 8237 là vi mch có 4 kênh tương thích v!i b VXL 8088, các kênh này có th m

rng thêm nhiu kênh khác mc dù ñi v!i h thng nh- thì 4 kênh này là qúa ñ". 8237

có kh năng thc hin truyn DMA lên t!i 1.6Mbyte/s .M2i kênh có kh năng ñánh ña

ch& t!i 64 Kbyte b nh! và có th truyn 64 Kbyte theo chương trình.

5.2.1 Sơ ñ khi và chc năng các khi ca vi mch 8237A

1. Sơ ñ khi

Hình 5.1: Vi m#ch 8237A -5

Tài liu môn hc: Ghép ni và ñiu khin thit b ngoi vi

Ging viên: Nguyn Văn Minh Trí 63

Hình 5.2: Sơ ñ* kh"i chi ti1t c'a 8237

- CLK : Ðưc ni v!i tín hiu ñ'ng h' h thng .

- CS :Tín hiu chn mch, thông thưng ni v!i ñu ra c"a mt b gii mã ña ch&.

- RESET : Xoá các thanh ghi tm, thanh ghi trng thái , thanh ghi lnh,thanh ghi yêu cu.

- READY : to trng thái ch cho 8237A-5 ñi v!i b nh! hoc I/O có tc ñ thp.

- HLDA (hold Acknowledge): tín hiu thông báo CPU ñã th n%i bus ña ch&, d liu,

ñiu khin c"a nó.

- DREQ

0

- DREQ

3

(DMA request) : Ðu vào yêu cu truyn DMA cho m2i kênh c"a

8237A-5, cc tính c"a các tín hiu vào này là có th lp trình ñưc .

- DB

0

- DB

7

(data bus ): Chân ni v!i bus d liu c"a b VXL 8088 ñưc s dng trong

quá trình trao ñ%i d liu

- IOR và IOW : ñiu khin ñc và ghi I/O .

- EOP (end of process ) : tín hiu hai chiu báo kt thúc DMA ti cui chu kỳ DMA .

- A

0

- A

3

: Chn thanh ghi ni cn lp trình và mt phn ña ch& truyn DMA trong quá

trình DMA .

- A

7

- A

4

: Cung cp 1 phn ña ch& còn li c"a DMA .

![Bài giảng Tổ chức - Cấu trúc Máy tính II Đại học Công nghệ Thông tin (2022) [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/8531747304537.jpg)