= 1 byte vöøa truyeàn ñi hoaëc nhaän ñöôïc laø döõ lieäu.

= 0 byte vöøa truyeàn ñi hoaëc nhaän ñöôïc laø ñòa chæ.

Bit 4 P Stop bit

P = 1 vöøa nhaän ñöôïc bit Stop.

P = 0 chöa nhaän ñöôïc bit Stop.

Bit 3 S Start bit

S = 1 vöøa nhaän ñöôïc bit Start.

S = 0 chöa nhaän ñöôïc bit Start.

Bit 2 bit information

I2C Slave mode:

= 1 ñoïc döõ lieäu.

= 0 ghi döõ lieäu.

I2C Master mode:

= 1 ñang truyeàn döõ lieäu.

= 0 khoâng truyeàn döõ lieäu.

Bit 1 UA Update Address

Bit naøy chæ coù taùc duïng ñoái vôùi cheá ñoä I2C Slave mode10 bit ñòa chæ.

UA = 1 vi ñieàu khieån caàn caäp nhaät theâm ñòa chæ töø thanh ghi SSPADD.

UA = 0 khoâng caàn caäp nhaät theâm ñòa chæ.

Bit 0 BF Buffer Full Status bit

BF = 1 Thanh ghi SSPBUF ñang chöùa döõ lieäu truyeàn ñi hoaëc nhaän ñöôïc.

BF = 0 thanh ghi SSPBUF khoâng coù döõ lieäu.

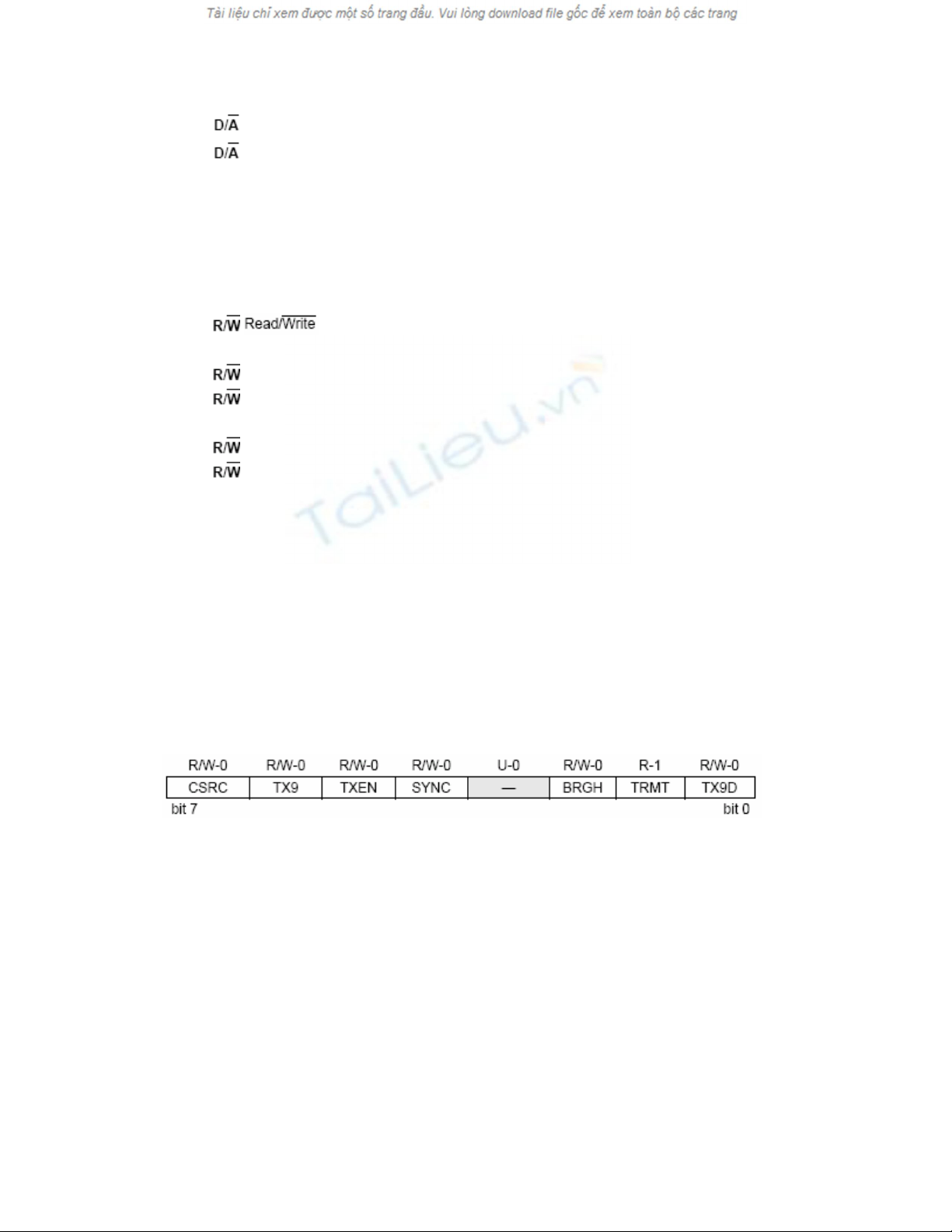

P2.44 Thanh ghi TXSTA: ñòa chæ 98h

Thanh ghi chöùa caùc bit traïng thaùi vaø ñieàu khieån vieäc truyeàn döõ lieäu thoâng qua chuaån

giao tieáp USART.

Bit 7 CSRC Clock Source Select bit

ÔÛ cheá ñoä baát ñoàng boä: khoâng caàn quan taâm.

ÔÛ cheá ñoä ñoàng boä:

CSRC = 1 Master mode (xung clock ñöôïc laáy töø boä taïo xung BRG).

CSRC = 0 Slave mode (xung clock ñöôïc nhaän töø beân ngoaøi).

Bit 6 TX-9 9-bit Transmit Enable bit

TX-9 = 1 truyeàn döõ lieäu 9 bit.

TX-9 = 0 truyeàn döõ lieäu 8 bit.

Bit 5 TXEN Transmit Enable bit

TXEN = 1 cho pheùp truyeàn.

TXEN = 0 khoâng cho pheùp truyeàn.

Bit 4 SYNC USART Mode Select bit

SYNC = 1 daïng ñoàng boä

SYNC = 0 daïng baát ñoàng boä.

Bit 3 Khoâng caàn quan taâm vaø maëc ñònh mang giaù trò 0.

Bit 2 BRGH High Baud Rate Select bit

Bit naøy chæ coù taùc duïng ôû cheá ñoä baát ñoàng boä.

BRGH = 1 toác ñoä cao.

BRGL = 0 toác ñoä thaáp.

Bit 1 TRMT Transmit Shift Register Status bit

TRMT = 1 thanh ghi TSR khoâng coù döõ lieäu.

TRMT = 0 thanh ghi TSR coù chöùa döõ lieäu.

Bit 0 TX9D

Bit naøy chöùa bit döõ lieäu thöù 9 khi döõ lieäu truyeàn nhaän laø 9 bit.

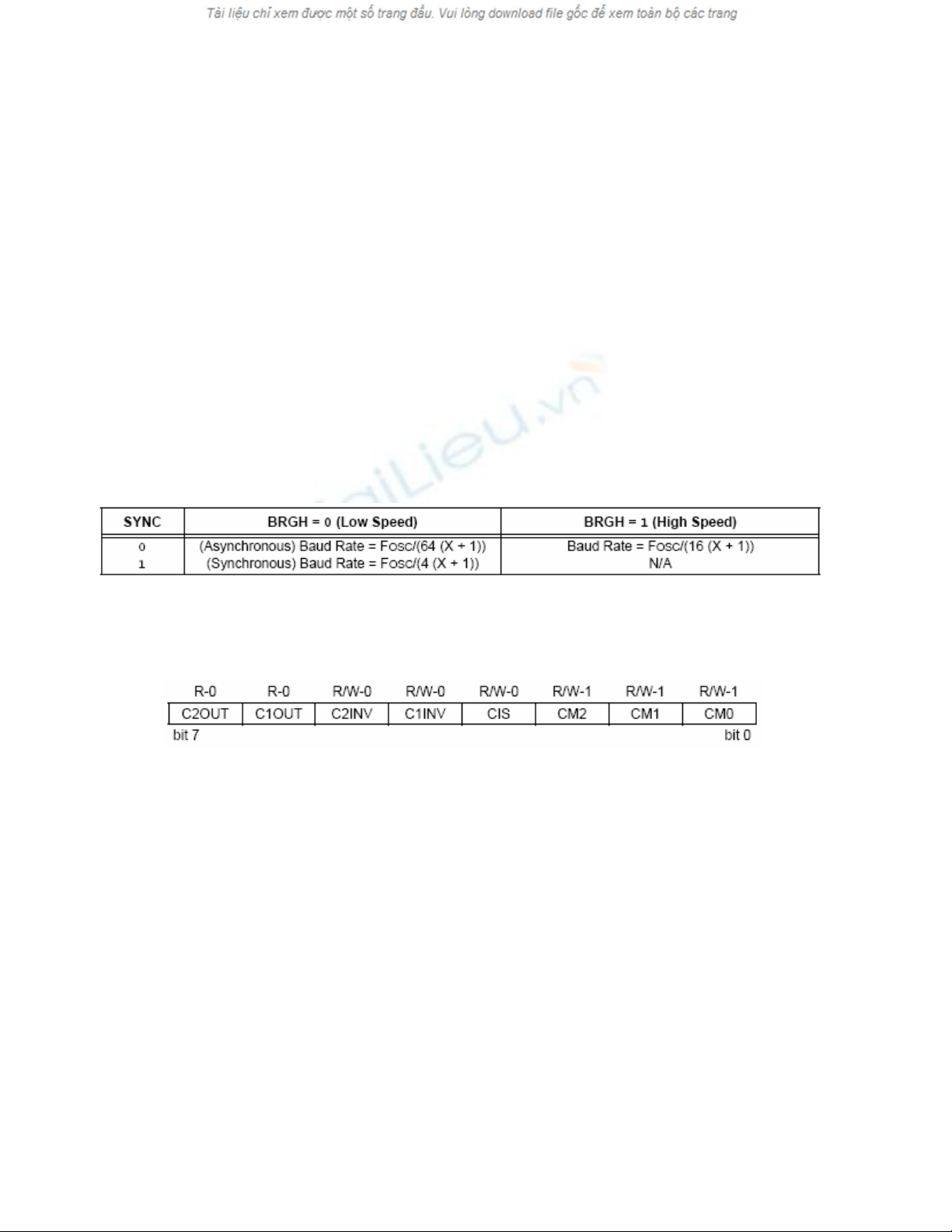

P2.45 Thanh ghi SPBRG: ñòa chæ 99h

Thanh ghi chöùa giaù trò taïo xung clock cho boä taïo xung BRG (Baud Rate Generator).

Taàn soá xung clock do BRG taïo ra ñöôïc tính theo caùc coâng thöùc trong baûng sau:

Trong ñoù X laø giaù trò chöùa trong thanh ghi SRBRG.

Thanh ghi CMCON: ñòa chæ 9Ch

Thanh ghi ñieàu khieån vaø chæ thò caùc traïng thaùi cuõng nhö keát quaû cuûa boä so saùnh.

Bit 7 C2OUT Comparator 2 (C2) Output bit

Khi C2INV = 0

C2OUT = 1 khi (pin VIN+ cuûa C2)> (pin VIN- cuûa C2).

C2OUT = 0 khi (pin VIN+ cuûa C2) < (pin VIN- cuûa C2).

Khi C2INV = 1

C2OUT = 1 khi (pin VIN+ cuûa C2)< (pin VIN- cuûa C2).

C2OUT = 0 khi (pin VIN+ cuûa C2) > (pin VIN- cuûa C2).

Bit 6 C1OUT Comparator 1 (C1) Output bit

Khi C1INV = 0

C1OUT = 1 khi (pin VIN+ cuûa C1)> (pin VIN- cuûa C1).

C1OUT = 0 khi (pin VIN+ cuûa C1) < (pin VIN- cuûa C1).

Khi C1INV = 1

C1OUT = 1 khi (pin VIN+ cuûa C1)< (pin VIN- cuûa C1).

C1OUT = 0 khi (pin VIN+ cuûa C1) > (pin VIN- cuûa C1).

Bit 5 C2INV Comparator 2 Output Conversion bit

C2INV = 1 ngoõ ra C2 ñöôïc ñaûo traïng thaùi.

C2INV = 0 ngoõ ra C2 khoâng ñaûo traïng thaùi.

Bit 4 C1INV Comparator 1 Output Conversion bit

C1INV = 1 ngoõ ra C1 ñöôïc ñaûo traïng thaùi.

C1INV = 0 ngoõ ra C1 khoâng ñaûo traïng thaùi.

Bit 3 CIS Comparator Input Switch bit

Bit naøy chæ coù taùc duïng khi CM2:CM0 = 110

CIS = 1 khi pin VIN- cuûa C1 noái vôùi RA3/AN3 vaø

pin VIN- cuûa C2 noái vôùi RA2/AN2

CIS = 0 khi pin VIN- cuûa C1 noái vôùi RA0/AN0 vaø

pin VIN- cuûa C2 noái vôùi RA1/AN1

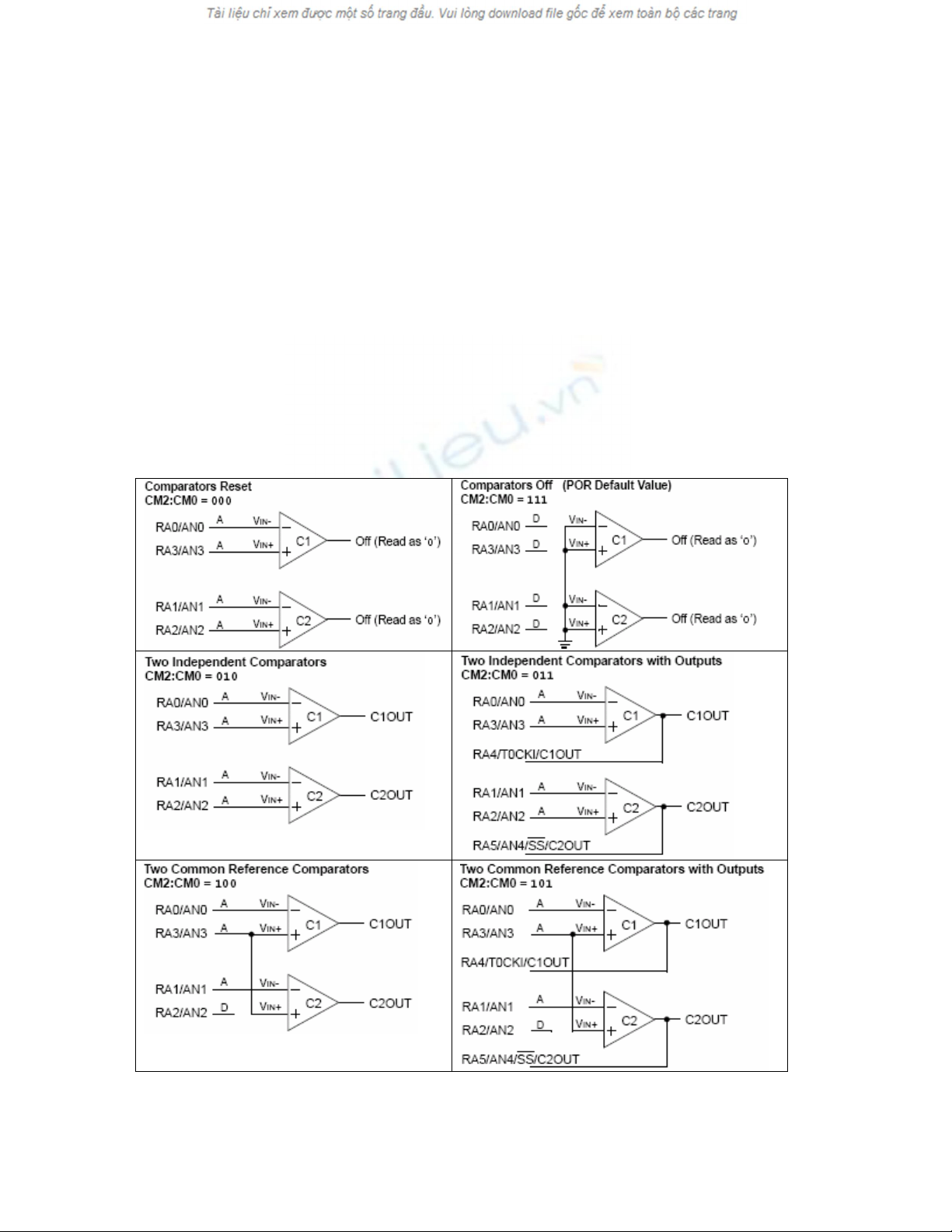

Bit 2-0 CM2:CM0 Comparator Mode bit

Caùc bit naøy ñoùng vai troø trong vieäc thieát laäp caùc caáu hình hoaït ñoäng cuûa boä

Comparator. Caùc daïng caáu hình cuûa boä Comparator ñöïôc trình baøy trong baûng sau:

Trong ñoù: A laø ngoõ vaøo Analog, khi ñoù giaù trò cuûa caùc pin naøy ñoïc töø caùc PORT luoân baèng 0.

B laø ngoõ vaøo Digital.

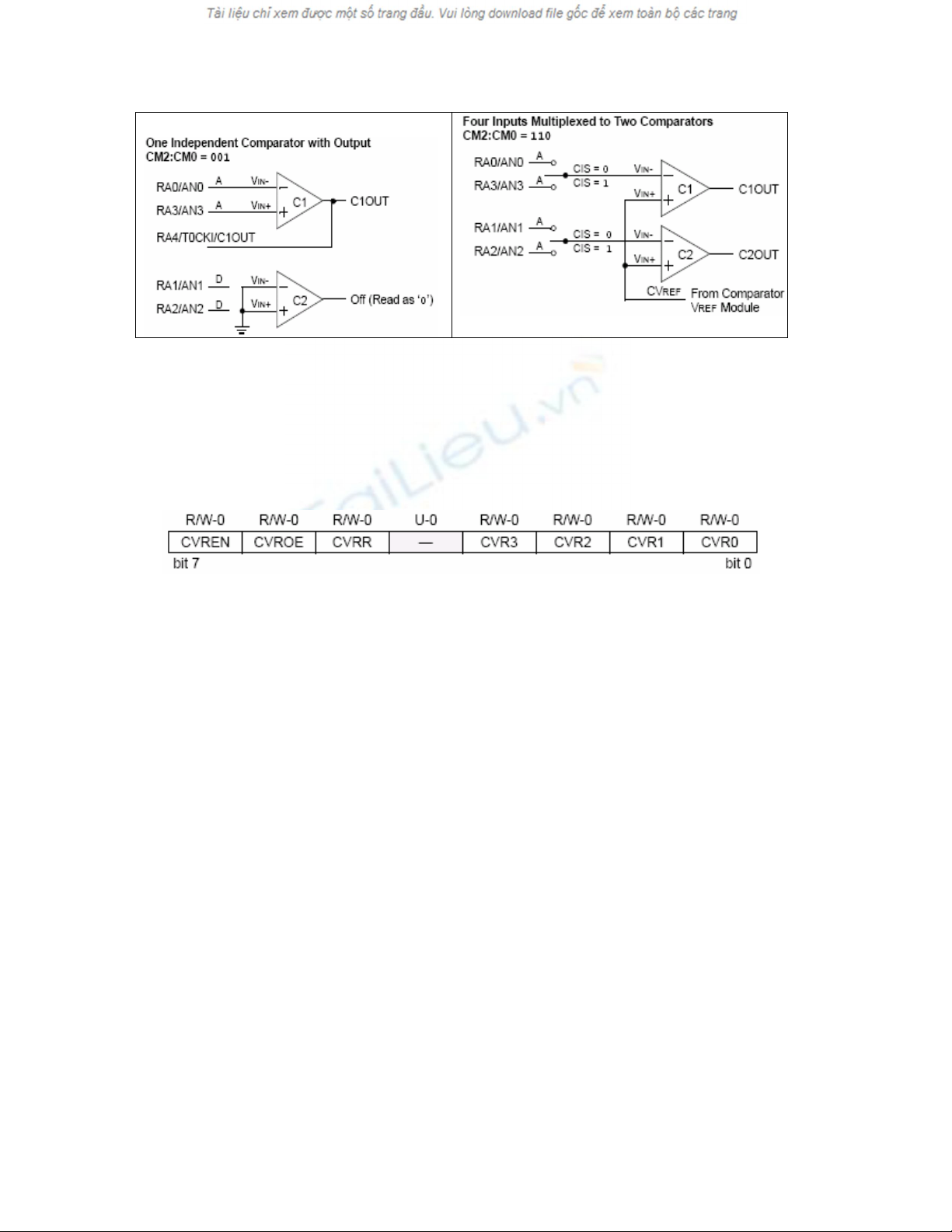

P2.46 Thanh ghi CVRCON: ñòa chæ 9Dh

Thanh ghi ñieàu khieån boä taïo ñieän aùp so saùnh khi boä Comparator hoaït ñoäng vôùi caáu

hình ‘110’.

Bit 7 CVREN Comparator Voltage Reference Enable bit.

CVREN = 1 boä taïo ñieän aùp so saùnh ñöôïc caáp ñieän aùp hoaït ñoäng.

CVREN = 0 boä taïo ñieän aùp so saùnh khoâng ñöôïc caáp ñieän aùp hoaït ñoäng.

Bit 6 CVROE Comparator VREF Output Enable bit

CVROE = 1 ñieän aùp do boä taïo ñieän aùp so saùnh taïo ra ñöôïc ñöa ra pin RA2.

CVROA = 0 ñieän aùp do boä taïo ñieän aùp so saùnh taïo ra khoâng ñöôïc ñöa ra ngoaøi.

Bit 5 CVRR Comparator VREF Range Selection bit

CVRR = 1 moät möùc ñieän aùp coù giaù trò VDD/24 (ñieän aùp do boä taïo ñieän aùp so

saùnh taïo ra coù giaù trò töø 0 ñeán 0.75VDD).

CVRR = 0 moät möùc ñieän aùp coù giaù trò VDD/32 (ñieän aùp do boä taïo ñieän aùp so

saùnh taïo ra coù giaù trò töø 0.25 ñeán 0.75VDD).

Bit 4 Khoâng caàn quan taâm vaø maëc ñònh mang giaù trò 0.

Bit 3-0 CVR3:CVR0 Caùc bit choïn ñieän aùp ngoõ ra cuûa boä taïo ñieän aùp so saùnh.

Khi CVRR = 1:

Ñieän aùp taïi pin RA2 coù giaù trò CVREF = (CVR<3:0>/24)*VDD.

Khi CVRR = 0

Ñieän aùp taïi pin RA2 coù giaù trò CVREF = (CVR<3:0>/32)*VDD + ¼VDD.

P2.47 Thanh ghi ADRESL: ñòa chæ 9Eh

Thanh ghi chöùa caùc bit thaáp cuûa keát quaû boä chuyeån ñoåi A/D (8 bit cao chöùa trong

thanh ghi ADRESH ñòa chæ 1Eh).

P2.48 Thanh ghi ADCON1: ñòa chæ 9Fh

Thanh ghi chöùa caùc bit ñieàu khieån boä chuyeån ñoåi ADC (ADC coù hai thanh ghi ñieàu

khieån laø ADCON1 vaø ADCON0).

Bit 7 ADFM A/D Result Format Select bit

ADFM = 1 Keát quaû ñöôïc löu veà phía beân phaûi 2 thanh ghi ADRESH:ADRESL

(6 bit cao mang giaù trò 0).

ADFM = 0 Keát quaû ñöôïc löu veà phía beân traùi 2 thanh ghi ADRESH:ADRESL

(6 bit thaáp mang giaù trò 0).

Bit 6 ADCS2 A/D Conversion Clock Select bit

ADCS2 keát hôïp vôùi 2 bit ADCS1:ADCS0 trong thanh ghi ADCON0 ñeå ñieàu

khieån vieäc choïn xung clock cho khoái chuyeån ñoåi ADC.

Bit 5,4 Khoâng caàn quan taâm vaø maëc ñònh mang giaù trò 0.

Bit 3-0 PCFG3:PCFG0 A/D Port Configuration Control bit

Caùc bit naøy ñieàu khieån vieäc choïn caáu hình hoaït ñoäng caùc coång cuûa boä chuyeån

ñoåi ADC.

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)