BÀI TẬP Ch12. Năng lượng và Công suất

12. 1 Mạch Inverter được thiết kế bằng transistor NMOS và tải RL thúc tụ CL.

Điện thế cấp điện Vs và MOSFET có điện trở RON, điện thế thềm VTH. GIả sử

logic 0 = 0V và logic 1 = Vs volt.

1. Xác định công suất trạng thái tĩnh tiêu thụ bởi inveter khi cho 0 tác động

vào ngõ vào của nó.

2. Xác định công suất trạng thái tĩnh tiêu thụ bởi inveter khi cho 1 tác động

vào ngõ vào của nó.

3. Xác định công suất tĩnh và công suất động tiêu thụ bởi Inveter khi cho liên

tiếp chuổi xung 01010101….tác động vào ngõ vào. Giả sử sự chuyển tiếp tín

hiệu ( 0 1, hoặc 1 0) xãy ra vài T giây, và hơn nữa T rất lớn hơn thời

hằng của mạch.

4. Giả sử ngõ vào như ở câu 3, cho biết thừa số nào làm cho công suất động bị

giảm nếu:

a. T tăng theo thừa số 2,

b. Vs giảm theo thừa số 2.

c. CL tăng theo thừa số 2 ?

5. Giả sử mạch Inverter thoả qui luật tĩnh với điện thế ngưỡng cao và thấp

tương ứng VIH = VH , VOL = VL. Cho biết MOSFET có RON và VTH. Giả sử

VL < VTH < VH < VS, chọn trị số RL trong số hạng của các thông số khác của

mạch sao cho công suất tiêu thụ của mạch Inverter là tối thiểu.

Đáp số:

1. Pstatic = 0

2.

2

S

static

ON L

V

PR R

=+

3.

( )

2

2

S

static

ON L

V

PR R

=+

,

( )

2 2

2

S L L

dynamic

ON L

V R C

P

R R T

=

+

4. a. phân nữa, b. phần tư, c. phân nữa,

5. Làm cực đại RL.

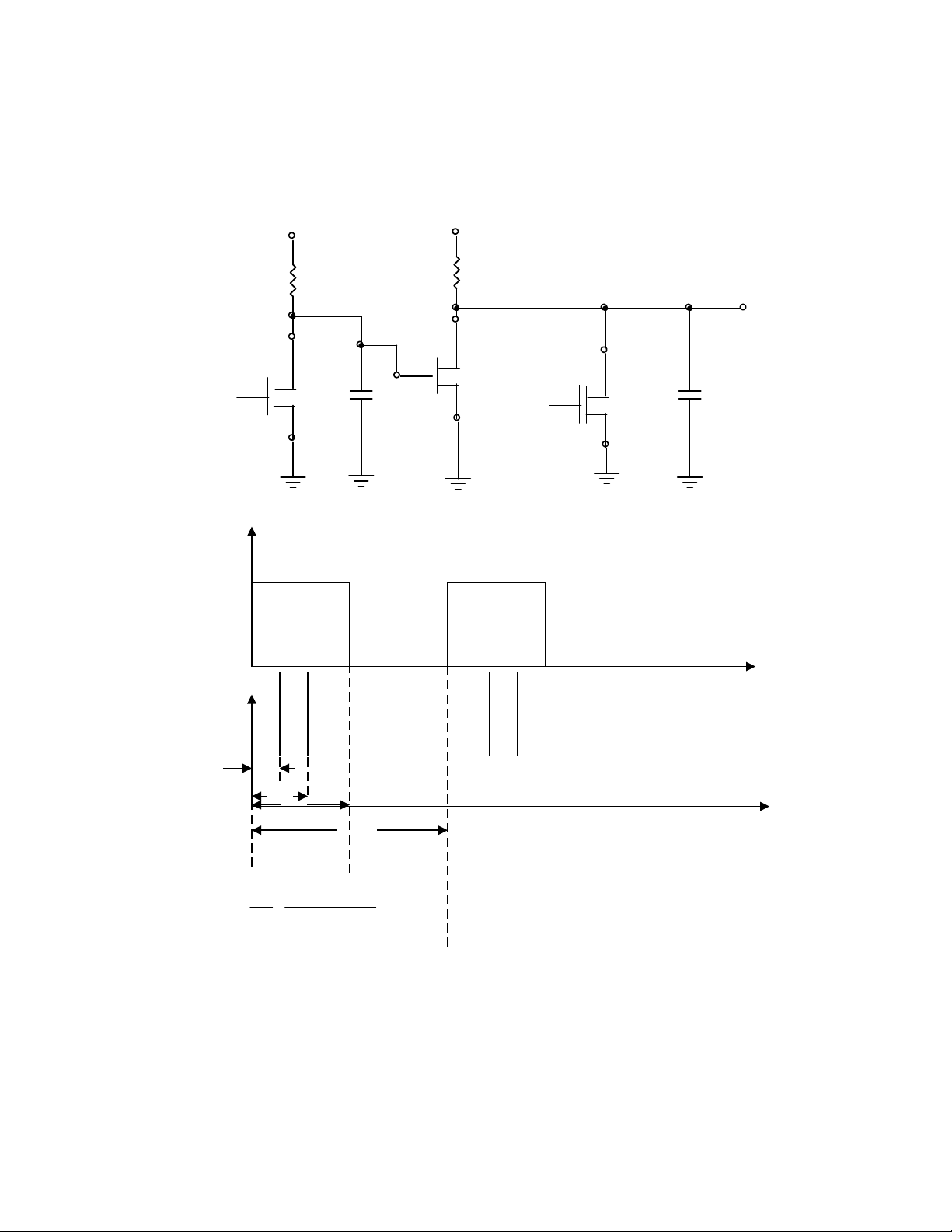

12.2 Bài tập này nhằm khảo sát công suất tiêu tán bởi mạch logic nhỏ. Mạch gồm

có mạch Inveter ghép nối tiếp và cổng NAND ở H. 12.2 . Mạch có hai ngõ

vào A và B, và moat ngõ ra Z. Tín hiệu vào là tuần hoàn với chu kỳ T4. Giả

sử RON của mỗi MOSFET là zero ( không).

1. Vẽ dạng sóng ngõ ra Z với

4

0t T� �

. Giả sử CG và CL đều bằng zero.

2. Suy ra công suất tĩnh thời gian trung bình tiêu thụ bởi mạch theo Vs, RL, T1,

T2, T3, và T4. Công suất tĩnh thời gian trung bình được định nghĩa là năng

lượng tổng cộng tiêu thụ bởi cổng trong suốt chu kỳ

4

0t T� �

chia cho T4

3. Giờ giả sử CG và CL khác không. Suy ra công suất động thời gian trung bình

tiêu thụ bởi mạch theo Vs, RL, T1, T2, T3, và T4. Đồng thời giả sử thời hằng

của mạch nhỏ hơn T1, T2-T1, T3-T2, và T4-T3.

4. Tính trị công suất tĩng và động thời gian trung bình với VS = 5V, RL = 10 k

Ω

,

CG = 100 fF, CL = 1 pF, T1 = 100 ns, T2 = 200 ns, T3 = 300 ns, và T4 = 600 ns.

1

5. Cho biết lượng năng lượng tiêu thụ bởi mạch trong một phút với các thông

số cho ở câu 4 ?

6. Cho biết phần trăm công suất tiêu thụ tổng cộng thời gian trung bình giảm

nếu điện thế cấp điện Vs giảm đi 30% ?

H.12.2

5V

A

. . . . .

0

t

5V

B

. . . . .

0

T1 t

T2

T3

T4

Đáp số

2.

2

1 2 4

4

S

L

V T T T

R T

� �

− + +

� �

� �

3.

( )

2

4

2

S

G L

VC C

T+

4. Pstatic = 2,9 mW, Pdynamic = 87,5

W

µ

5. 0,18 j

6. 51%

12.3 Một mạch gồm N Inverter, với N>>1. Mỗi Inverter được thiết kế bằng

transistor NMOS và điện trở RL. Điện thế cấp điện Vs và điện trở khi MOSFET

2

Z

Vs

Vs

A

RL RL

CG

CL

B

dẫn là RON. Điện thế thềm của NMOS là VTH. Cho biết các inverter ghép nối tiếp

thành chuổi. Tính công suất tĩnh tiêu thụ của mạch.

Đáp số:

2

2

S

static

L ON

VN

PR R

� �

=� �

+

� �

3

![Tài liệu tham khảo Tiếng Anh lớp 8 [mới nhất/hay nhất/chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250806/anhvan.knndl.htc@gmail.com/135x160/54311754535084.jpg)

![Phiếu bài tập cuối tuần Tiếng Việt 1 tuần 2 đề 2: [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250728/thanhha01/135x160/42951755577464.jpg)