Slide 1

4.396 Điện tử tương tự 1

Bài giảng: Transistor trường

Slide 2

Nội dung

•5.1 Cấu trúc và hoạt động của transistor trường

–5.1.1 Phân loại transistor trường

–5.1.2 Transistor trường có cực cửa tiếp giáp (JFET)

–5.1.3 Transistor trường có cực cửa cách ly (MOSFET)

•5.2 Các dạng mắc mạch

–5.2.1 Mạch nguồn chung

–5.2.2 Mạch máng chung

–5.2.3 Mạch cửa chung

•5.3 Các phương pháp phân cực cho trasistor trường

–5.3.1 PP phân cực cố định

–5.3.2 PP tự phân cực

–5.3.3 PP phân cực bằng mạch phân áp

–5.3.4 PP phân cực kiểu hồi tiếp

•5.4 Các tham số kỹ thuật quan trọng của FET

Slide 3

5.1 Cấu trúc và hoạt động của FET

•5.1.1 Phân loại transistor trường

•5.1.2 Tran Transistor trường có cực cửa

tiếp giáp (JFET)

•5.1.3 Transistor trường có cực cửa cách ly

(MOSFET)

Slide 4

5.1.1 Phân loại FET

•Transistor trường có cực cửa tiếp giáp

JFET (Junction Field-Effect Transistor)

–Kênh n

–Kênh p

•Transistor trường có cực cửa cách ly

MOSTFET (Metal-Oxide-Semiconductor

Field-Effect Transistor)

–Kiểu Depletion: kênh n, kênh p

–Kiểu Enhancement: kênh n, kênh p

Slide 5

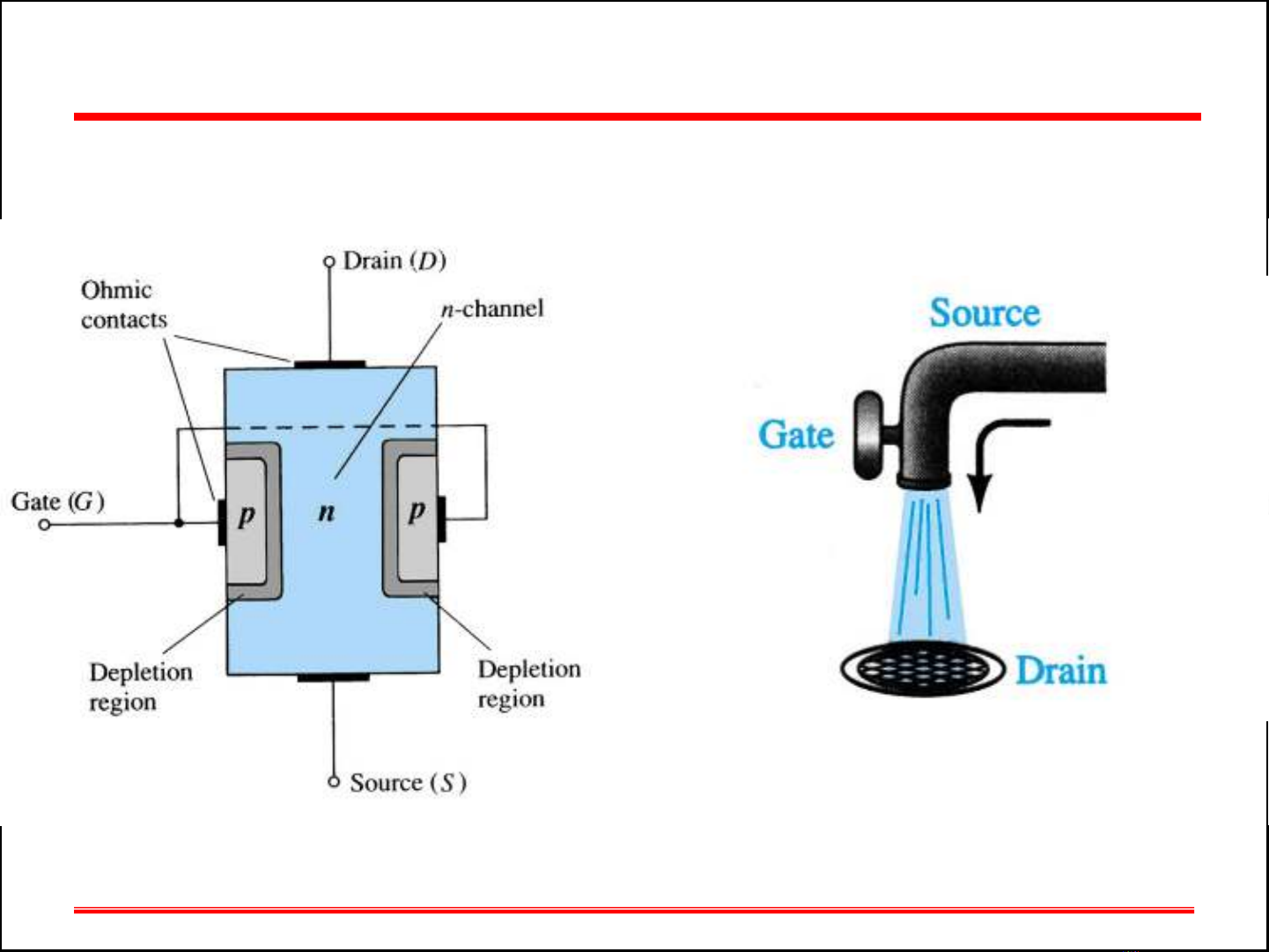

5.1.2 JFET

• Cấu trúc

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Vô tuyến điện viên hàng hải GMDSS hạng tổng quát: Phần 1 [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/45101777969769.jpg)

![Giáo trình Thực tập điện tử cơ bản: Phần 1 [Full]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260504/vispacex_27/135x160/66001778032993.jpg)