Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

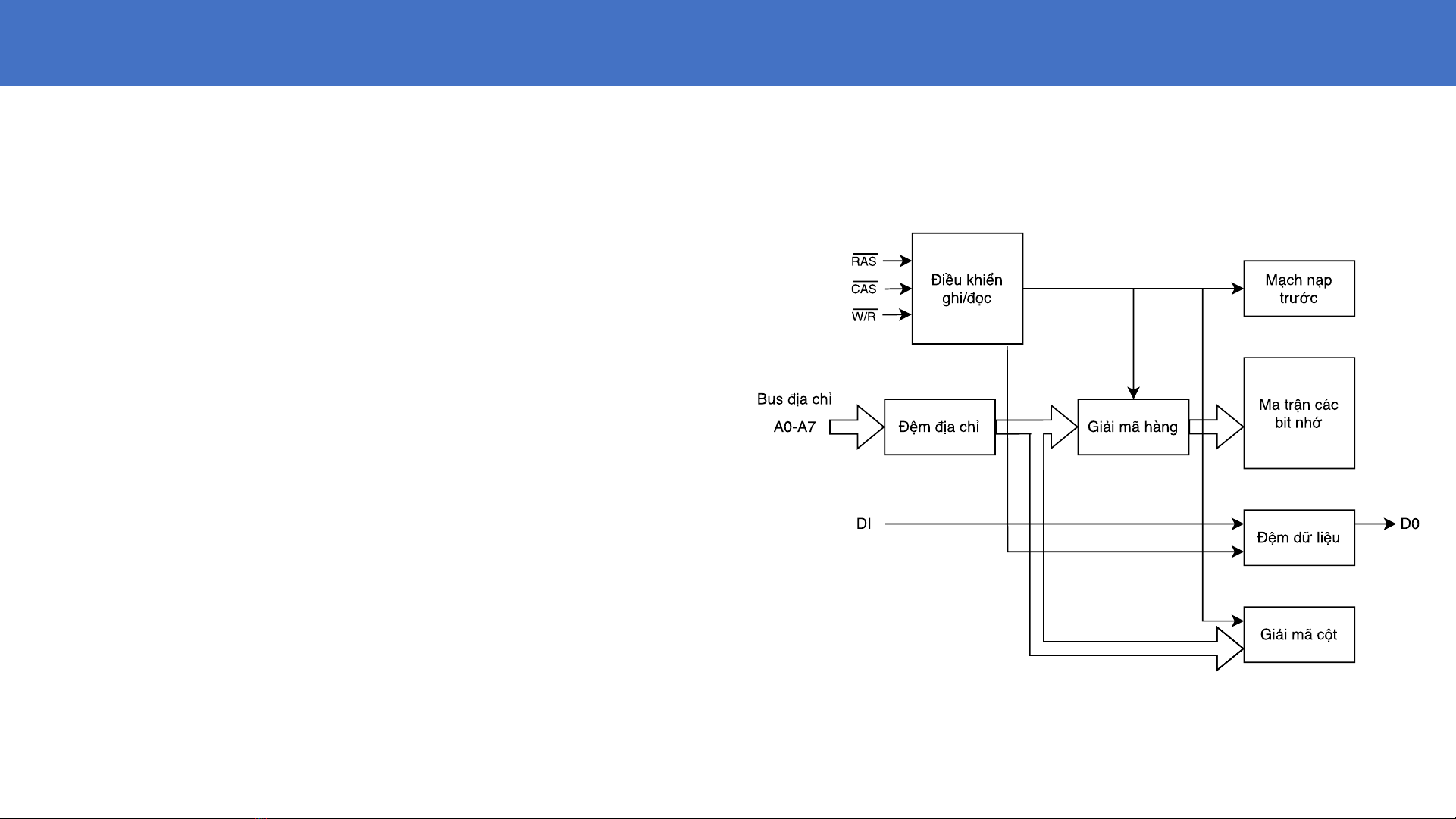

BỘ NHỚ BÁN DẪN – DYNAMIC RANDOM ACCESS MEMORY

DRAM dùng n địa chỉ dồn kênh để nạp lần

lượt (2 lần) địa chỉ hàng và địa chỉ cột vào

đệm địa chỉ/

Dung lượng của chip DRAM 22n ×m bit

Các chân tín hiệu điều khiển

•RAS (Row Access Strobe): điều khiển việc nạp địa

chỉ hàng

•CAS (Column Access Strobe): điều khiển việc nạp

địa chỉ cột

•W/R = 0 điều khiển ghi chip, W/R = 1 điều khiển

đọc chip

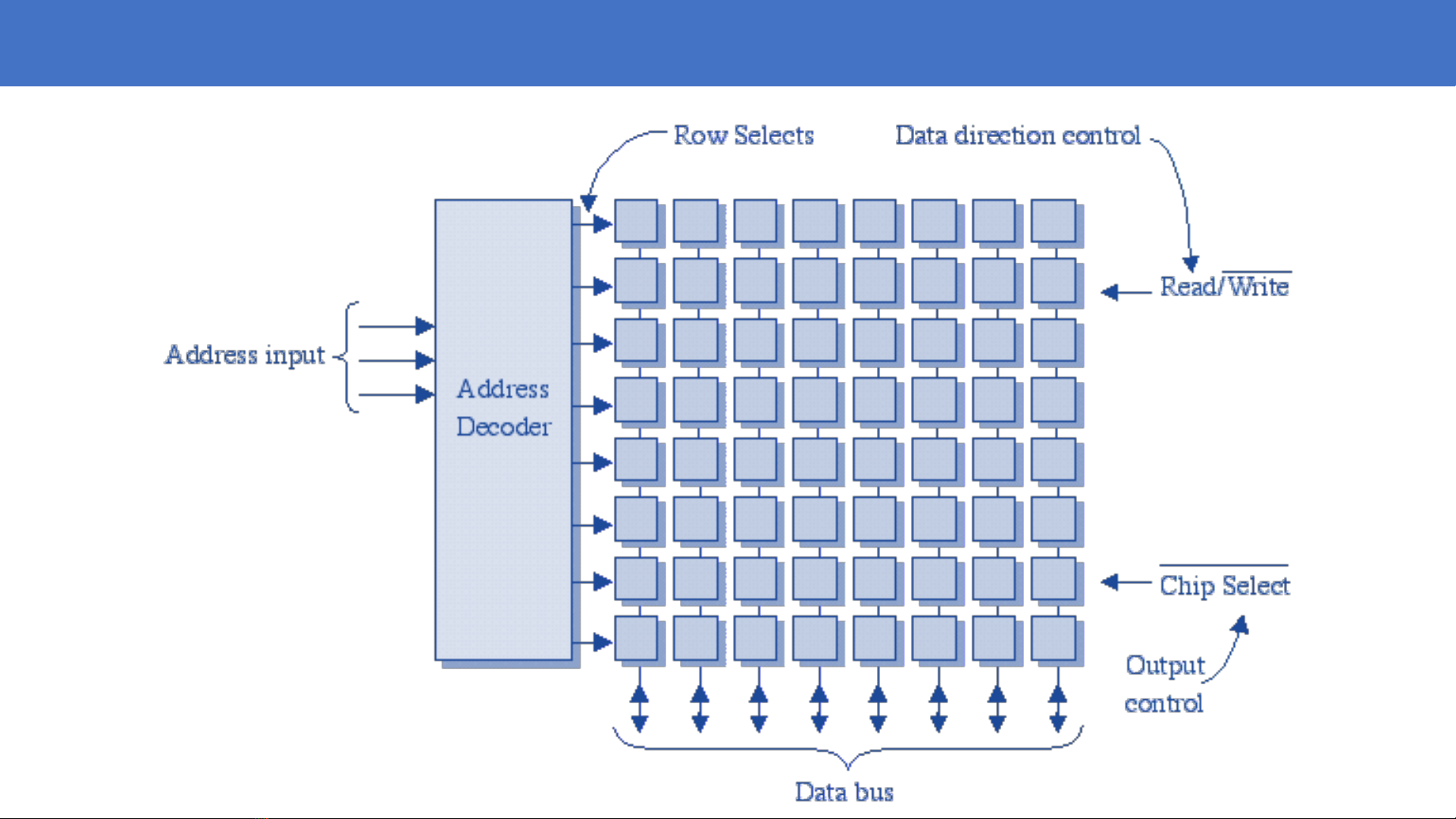

TỔ CHỨC CHIP NHỚ

Cơ chế refresh của DRAM

Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

• Điện tích trên một tụ điện trong một ônhớ của DRAM sẽ bị phóng điện Số

liệu bị thay đổi.

•Khi đọc/ghi bộ nhớ thì DRAM được làm tươi tự động.

•Có 03 kỹ thuật làm tươi (refresh phổ biến)

+Chỉ kích hoạt RAS (RAS –Only –Refresh)

+ Kích hoạt CAS trước RAS (CAS - Before - RAS - Refresh)

+Làm tươi ẩn (Hiden –Refresh)

Cơ chế refresh của DRAM

Khoa Công Nghệ Thông Tin – Đại học Sài Gòn Kiến Trúc Máy Tính

❑Chỉ kích hoạt RAS (RAS –Only –Refresh)

•Sử dụng các chu trình đọc giả để làm tươi DRAM.

•Tín hiệu 𝑅𝐴𝑆 được đặt ở mức tích cực để chọn hàng.

•Các tín hiệu 𝐶𝐴𝑆 bị cấm.

•DRAM được đọc bên trong một hàng vào các cặp dây bit và khuếch đại số

liệu đọc, tuy nhiên không truyền được chúng ra các cặp dây I/O →Số

liệu không truyền ra đệm lối ra.

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)