1

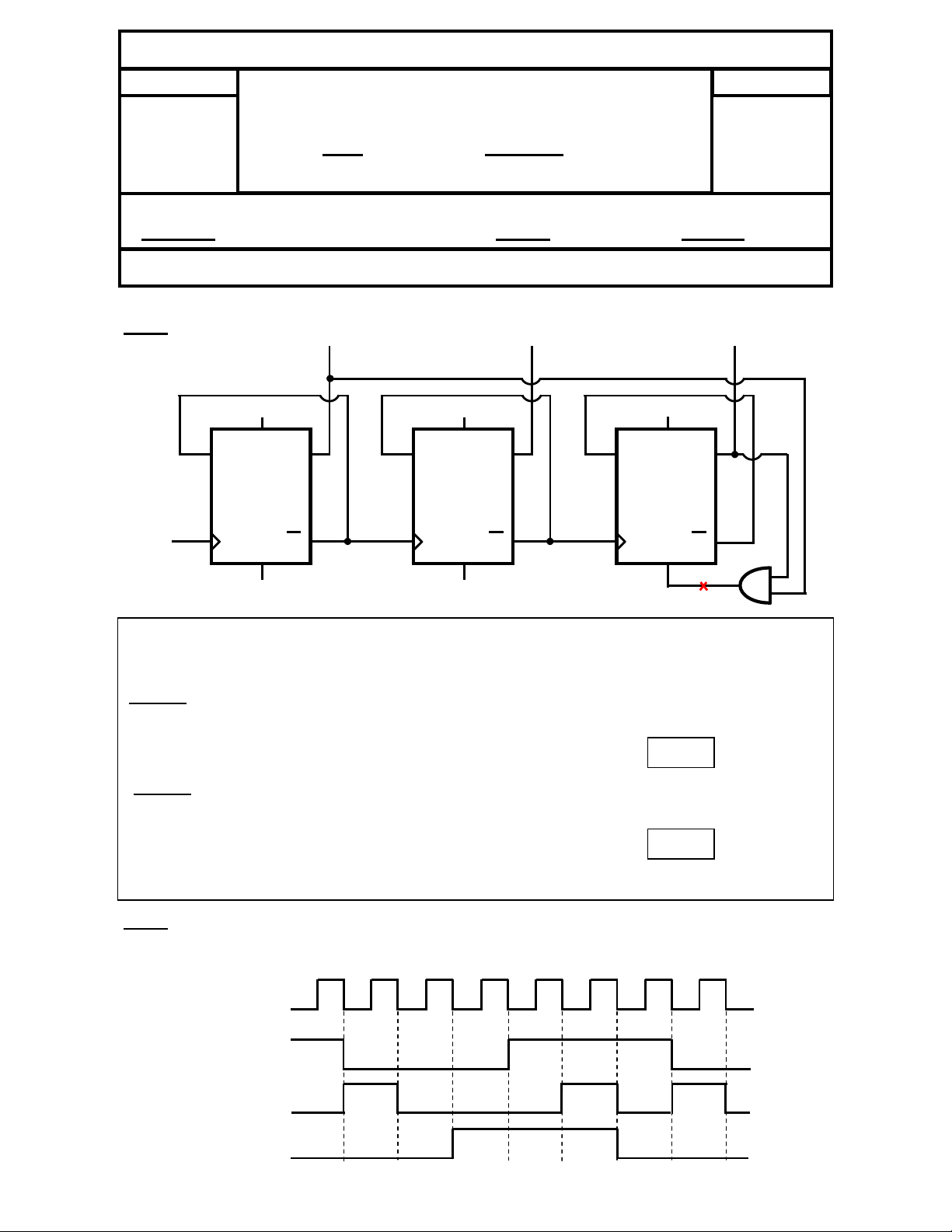

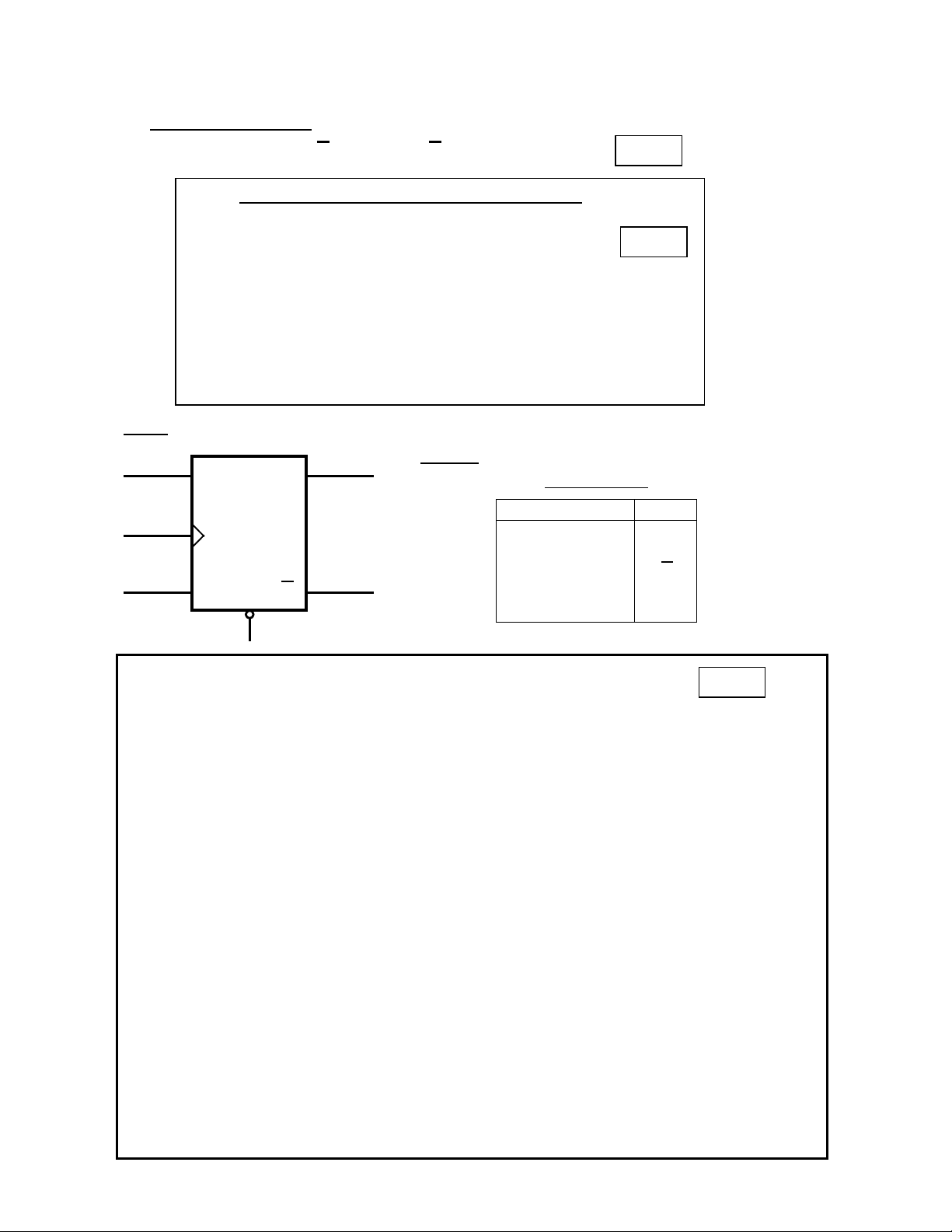

Câu 1 (1,0 điểm) Phân tích và xác định dãy đếm của bộ đếm như hình vẽ.

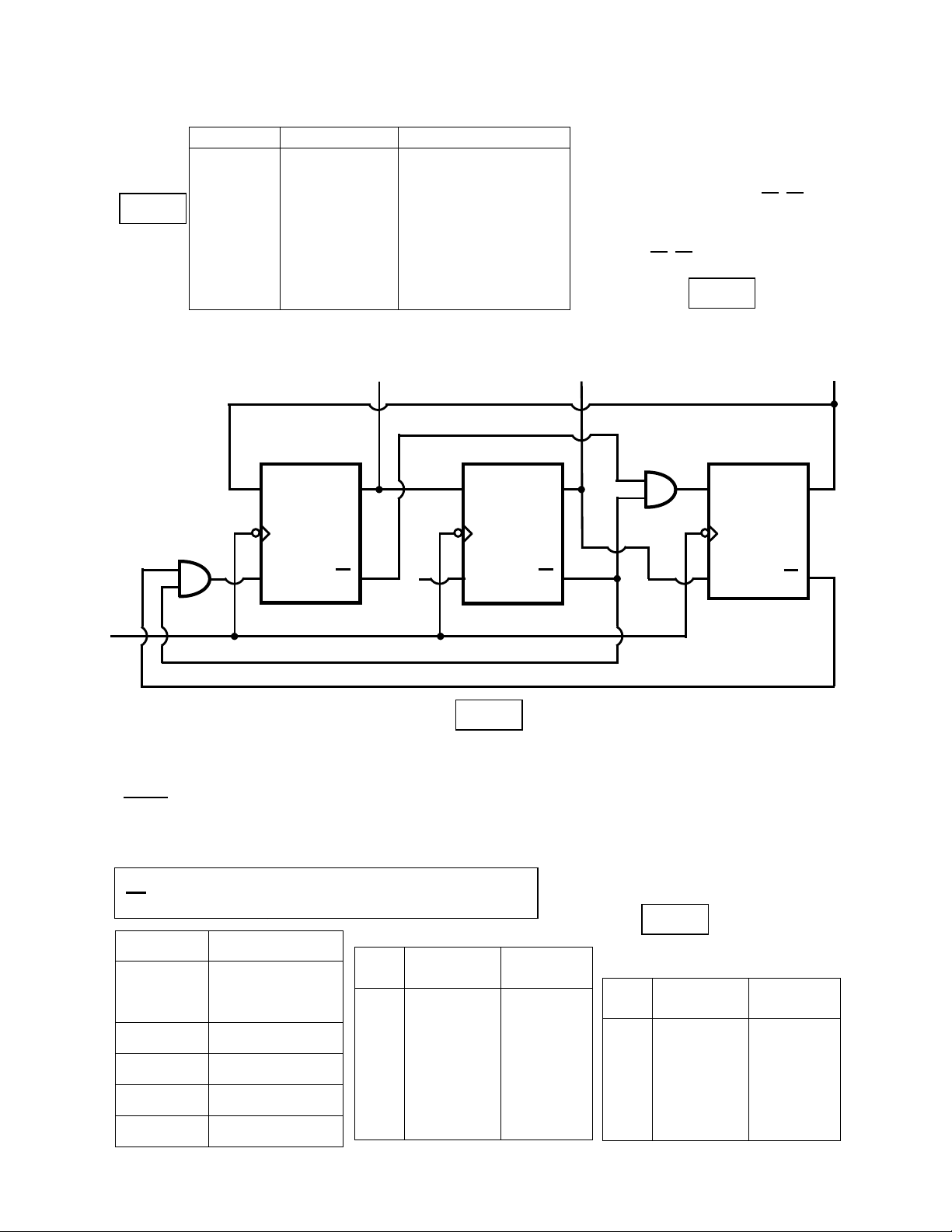

Câu 2 (2,0 điểm) Sử dụng JK-FF, thiết kế bộ đếm song song có giản đồ xung như hình vẽ (các

trạng thái không có trong vòng đếm đều chọn trạng thái kế tiếp là trạng thái đầu của giản

đồ).

Điểm Chữ kí giám thị

Điểm

SINH VIÊN LÀM BÀI NGAY TRÊN ĐỀ THI - ĐỀ THI CÓ 6 TRANG

ĐỀ THI HK1 (2013-2014)

Môn: Kỹ thuật số Thời gian: 110 phút

(SINH VIÊN KHÔNG ĐƯỢC SỬ DỤNG TÀI LIỆU)

HỌ TÊN: ………………………………………. MSSV: ………………… NHÓM: ………..

ĐH BÁCH KHOA TP.HCM * KHOA ĐIỆN - ĐIỆN TỬ * BỘ MÔN ĐIỆN TỬ

CK

Q

A

(msb)

Q

B

Q

C

D

CK

Q

Q

Q

0

CK

Pr

Cl

D

CK

Q

Q

Q

1

Pr

Cl

D

CK

Q

Q

Q

2

Pr

Cl

0

0

0

0

0

Z

Từ hình vẽ, ta thấy đây là bộ đếm lên, không đầy đủ. Ta có, tín hiệu reset: Z = Q

2

Q

0

,

vậy khi Q

2

Q

1

Q

0

= 1x1, bộ đếm sẽ reset về trạng thái đầu. Xét 2 trường hợp:

* T/H1: Q

2

Q

1

Q

0

= 101, trạng thái đầu là Q

2

Q

1

Q

0

= 001 (do Z chỉ đưa vào chân Clear của Q

2

).

Từ trạng thái 001, bộ đếm sẽ đếm lên: 001 -> 010 -> 011 -> 100. Xung clock tiếp theo sẽ reset

bộ đếm về lại 001. Ta có bộ đếm lên m=4, bắt đầu từ trạng thái 001.

* T/H2: Q

2

Q

1

Q

0

= 111, trạng thái đầu là Q

2

Q

1

Q

0

= 011. Từ trạng thái 011, bộ đếm sẽ đếm

lên: 011 -> 100. Với xung clock tiếp theo sẽ reset bộ đếm về lại 001. Ta cũng lại có bộ đếm

lên m=4, bắt đầu từ trạng thái 001 như trường hợp 1.

Vậy ta có dãy đếm là: Q

2

Q

1

Q

0

= 001, 010, 011, 100, 001, …

0

,5

đ

0

,5

đ

2

Câu 3 (1,0 điểm) Một hệ tuần tự kiểu MEALY có một ngõ vào X và một ngõ ra Z. Ngõ ra Z là

1 khi ngõ vào X nhận được chuỗi bit liên tiếp là 010 hoặc 0110. Biết rằng chuỗi được xét liên

tục. Hãy thành lập bảng chuyển trạng thái. Rút gọn bảng trạng thái (nếu được)

(1,0 đ)

Trạng thái

Ý nghĩa

A Trạng thái reset

(chưa nhận bit)

B 1 bit 0

C 1 bit 1

D 2 bit 0,1

E 3 bit 0,1,1

Vd: X = 0,1,1,1,0,1,0,1,1,0,1,0,0,0,1,1,0,1,1,1,0,1,0,1,..

Z = 0,0,0,0,0,0,1,0,0

,1

,0,1,0,0,0,0,1,0,0,0,0,0,1,0,..

HT KT

X=0 X=1

Z

X=0 X=1

A

B

C

D

E

B C

B D

B C

B E

B C

0 0

0 0

0 0

1 0

1 0

Ta có, A và C tương đương

HT KT

X=0 X=1

Z

X=0 X=1

A

B

D

E

B A

B D

B E

B A

0 0

0 0

1 0

1 0

1,0 đ

J

A

Q

A

Q

A

Q

A

CK

J

B

Q

B

Q

B

Q

B

J

C

Q

C

Q

C

Q

C

1

K

A

K

B

K

C

0

,5

đ

Dãy đếm Q

A

Q

B

Q

C

= 100, 010, 000, 001, 101, 111, 100, …

Q

A

Q

B

Q

C

Q

+A

Q

+B

Q

+C

J

A

K

A

J

B

K

B

J

C

K

C

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 1

1 0 1

0 0 0

1 0 0

0 1 0

1 1 1

1 0 0

1 0 0

0 X 0 X 1 X

1 X 0 X X 0

0 X X 1 0 X

1 X X 1 X 1

X 1 1 X 0 X

X 0 1 X X 0

X 0 X 1 0 X

X 0 X 1 X 1

Rút gọn bìa K, ta có:

J

A

= Q

C

K

A

= Q

B

Q

C

J

B

= Q

A

K

B

= 1

J

C

= Q

A

Q

B

K

C

= Q

B

0,75

đ

0,75

đ

3

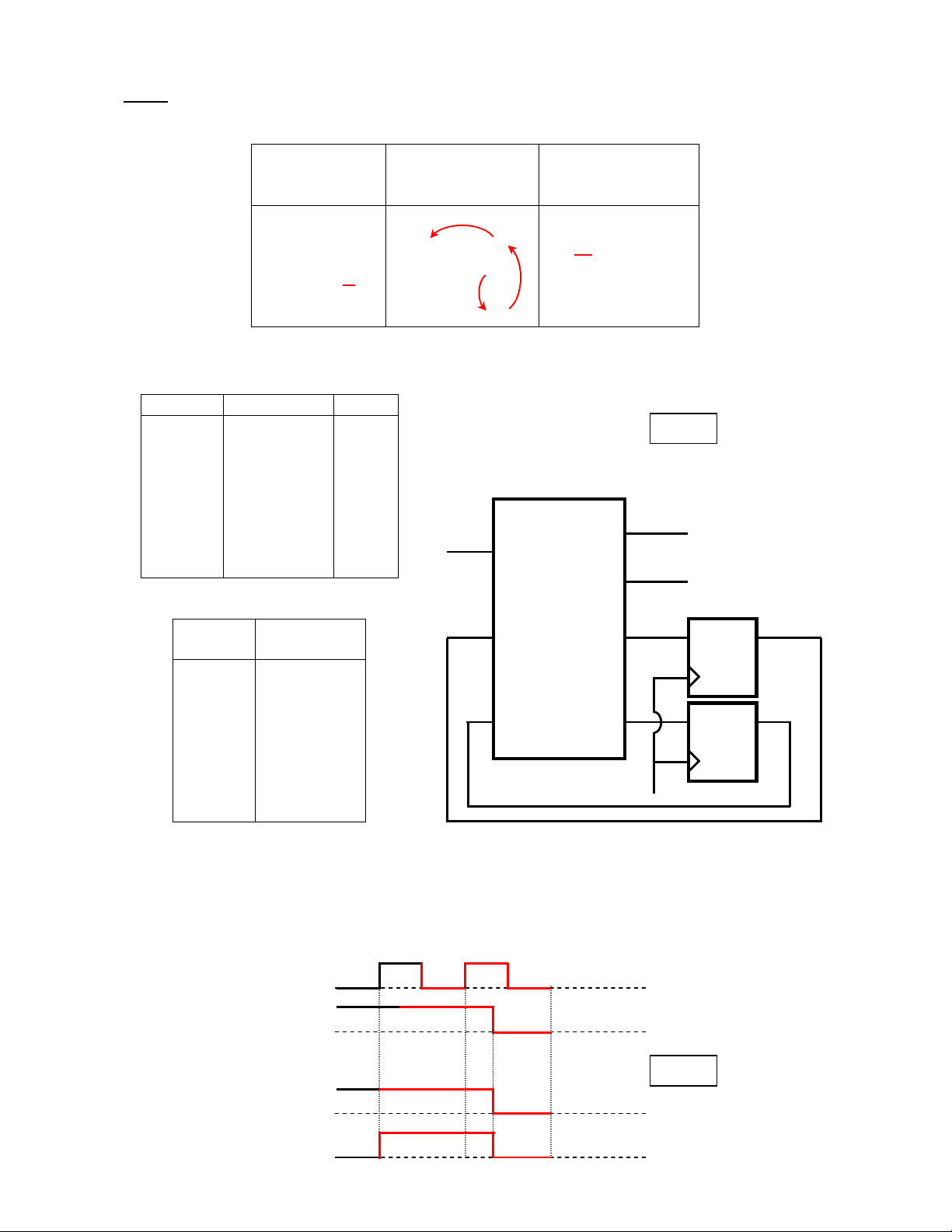

Câu 4 (2,0 điểm) Hệ tuần tự có 1 ngõ vào X và 2 ngõ ra U, V. Khi có xung clock cạnh lên thì hệ

chuyển trạng thái theo bảng sau:

TT hiện tại

Q

1

Q

0

TT kế tiếp

X = 0 X = 1

Ngõ ra (UV)

X = 0 X = 1

10 A

01 B

00 C

11 D

A B

C A

B D

C B

01 01

00 11

01 10

10 11

a. Thiết kế hệ trên bằng T-FF và ROM (vẽ sơ đồ kết nối ROM với Flipflop và bảng

nạp ROM)

b. Biết rằng ban đầu hệ tuần tự ở trạng thái C và X = 1 khi hệ có cạnh lên clock như

hình vẽ. Xác định ngõ vào X cần thiết để có U = V= 0 với số xung clock ít nhất. Vẽ xung của

ngõ vào X và ngõ ra U và V trong trường hợp này. (Chú ý tín hiệu X không thay đổi tại cạnh

lên của clock)

X Q

1

Q

0

U V Q

+

1

Q

+

0

T

1

T

0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 1 0 1

0 0 0 0

0 1 1 0

1 0 0 0

1 0 1 1

1 1 1 0

0 1 0 1

1 1 0 1

0 1

0 1

0 0

1 1

1 1

1 1

1 1

1 0

Bảng nạp ROM

X Q

1

Q

0

A

2

A

1

A

0

U V T

1

T

0

D

3

D

2

D

1

D

0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 1 0 1

0 0 0 1

0 1 0 0

1 0 1 1

1 0 1 1

1 1 1 1

0 1 1 1

1 1 1 0

A

2

A

1

A

0

D

1

D

0

T

1

Q

1

T

0

Q

0

CK

V

D

2

U

D

3

X

ROM 2

3

x 4 (bit)

1,0 đ

C

lock

Trạng thái

U

V

X

C D B

1,0 đ

4

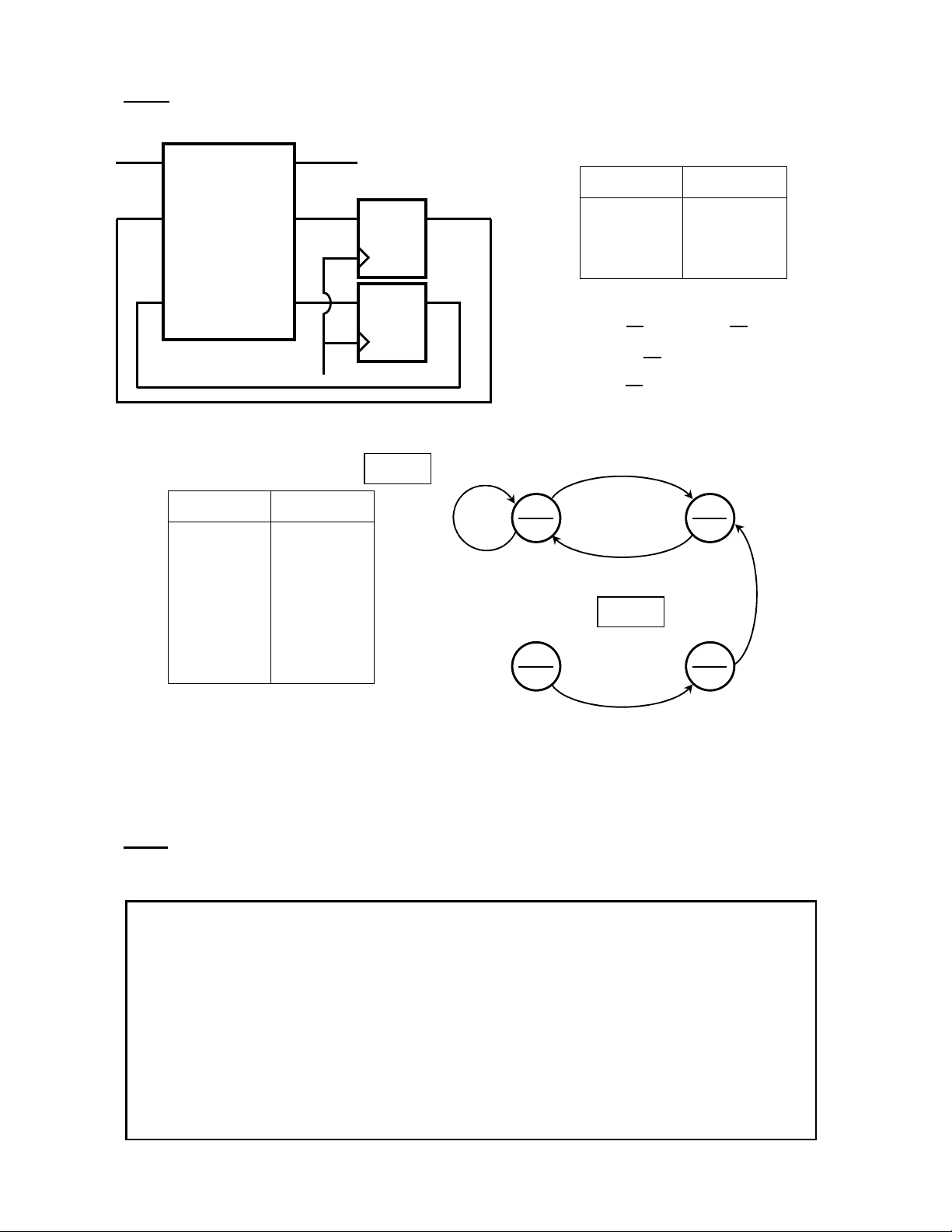

Câu 5 (1,0 điểm) Hệ tuần tự được thiết kế bằng PLA và D-FF như hình vẽ. Hãy vẽ giản đồ

trạng thái của hệ.

Câu 6 (1,0 điểm)

Cho code VHDL mô tả hàm logic F. Hãy xác định biểu thức của F và viết lại code bằng

lệnh WITH-SELECT-WHEN (chỉ viết từ phần architecture)

library ieee;

use ieee.std_logic_1164.all;

entity CAU6 is

port ( A, B, C, D : IN std_logic; F : OUT std_logic);

end CAU6;

architecture THI of CAU6 is

begin

process (A, B, C, D)

begin

if A = ‘0’ then F <= B and C; else F <= not C or D; end if;

end process;

end THI

;

Bảng nạp PLA

X Q

A

Q

B

Z D

A

D

B

1 0 -

- - 1

- 0 1

- 1 0

0 1 0

0 1 0

1 0 1

1 0 0

Z

X

Q

A

Q

B

D

A

D

B

D

Q

D

Q

CK

ck

ck

Từ bảng PLA, ta có:

Z = Q

A

Q

B

+ Q

A

Q

B

D

A

= X Q

A

+ Q

B

= Q

+A

D

B

= Q

A

Q

B

= Q

+B

B

ảng chuyển trạng thái

X Q

A

Q

B

Z Q

+A

Q

+B

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 0

1 1 1

1 0 0

0 1 0

0 1 0

1 1 1

1 0 0

0 1 0

0

,5

đ

00

0

10

1

01

1

11

0

X = 0 0, 1

0, 1

0, 1

1

0

,5

đ

5

Câu 7 (1,0 điểm) Cho Flip-flop như hình vẽ. Hãy viết code VHDL mô tả Flip-flop này.

Bảng hoạt động

Cl M N

Q

+

0 X X

1 0 0

1 0 1

1 1 0

1 1 1

0

0

Q

Q

1

M

N

CK

Q

Q

Cl

*Chú ý: Ngõ vào Cl (clear) là ngõ vào đồng bộ

entity MN_FF is

port ( CK, Cl, M, N : IN std_logic;

Q, nQ : BUFFER std_logic);

end MN_FF;

architecture THI of MN_FF is

begin

process (CK)

begin

if rising_edge (CK) then

if Cl = ‘0’ then Q <= ‘0’ ;

elsif M = ‘0’ and N = ‘0’ then Q <= ‘0’;

elsif M = ‘0’ and N = ‘1’ then Q <= not Q;

elsif M = ‘1’ and N = ‘1’ then Q <= ‘1’;

end if;

end if;

nQ <= not Q;

end process;

end THI

;

1,0 đ

Viết lại bằng lệnh WITH – SELECT - WHEN

architecture THI of CAU6 is

begin

WITH A SELECT

F <= B and C WHEN ‘0’,

not C or D WHEN OTHERS;

end THI

;

0

,5

đ

Biểu thức của hàm F:

F = A . B C + A (C + D)

0

,5

đ

![Đề thi trắc nghiệm Kỹ thuật mạch điện tử: Tổng hợp [Năm]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250920/kimphuong1001/135x160/23481758356189.jpg)

![Giáo trình Trang bị điện cơ bản (Nghề Điện công nghiệp TC) - Trường Cao đẳng Kỹ thuật Đồng Nai [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251212/laphong0906/135x160/58031779074467.jpg)

![Giáo trình Trang bị điện nước (TC) - Trường Cao đẳng Công nghiệp Thanh Hóa [Ngành Điện nước]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260511/hoatrami2026/135x160/14221778681890.jpg)