B¸o c¸o tèt nghiÖp t« kim hïng – tù ®éng 46

Tr−êng ®hnni – hµ néi khoa c¬ ®iÖn

51

- KÝch vµo “OK” ®Ó b¾t ®Çu.

- NÕu Download thµnh c«ng hép tho¹i “Download Successful” xuÊt hiÖn.

- ChuyÓn tr¹ng th¸i cña PLC tõ STOP sang RUN tr−íc khi ch¹y ch−¬ng tr×nh

trªn PLC.

- NÕu Download kh«ng thµnh c«ng ta ph¶i thiÕt lËp l¹i truyÒn th«ng gi÷a PLC

vµ PC vµ thùc hiÖn l¹i c¸c b−íc nh− trªn.

3.1.9. Mét sè lÖnh c¬ b¶n cña S7-200

1. LÖnh vµo/ra

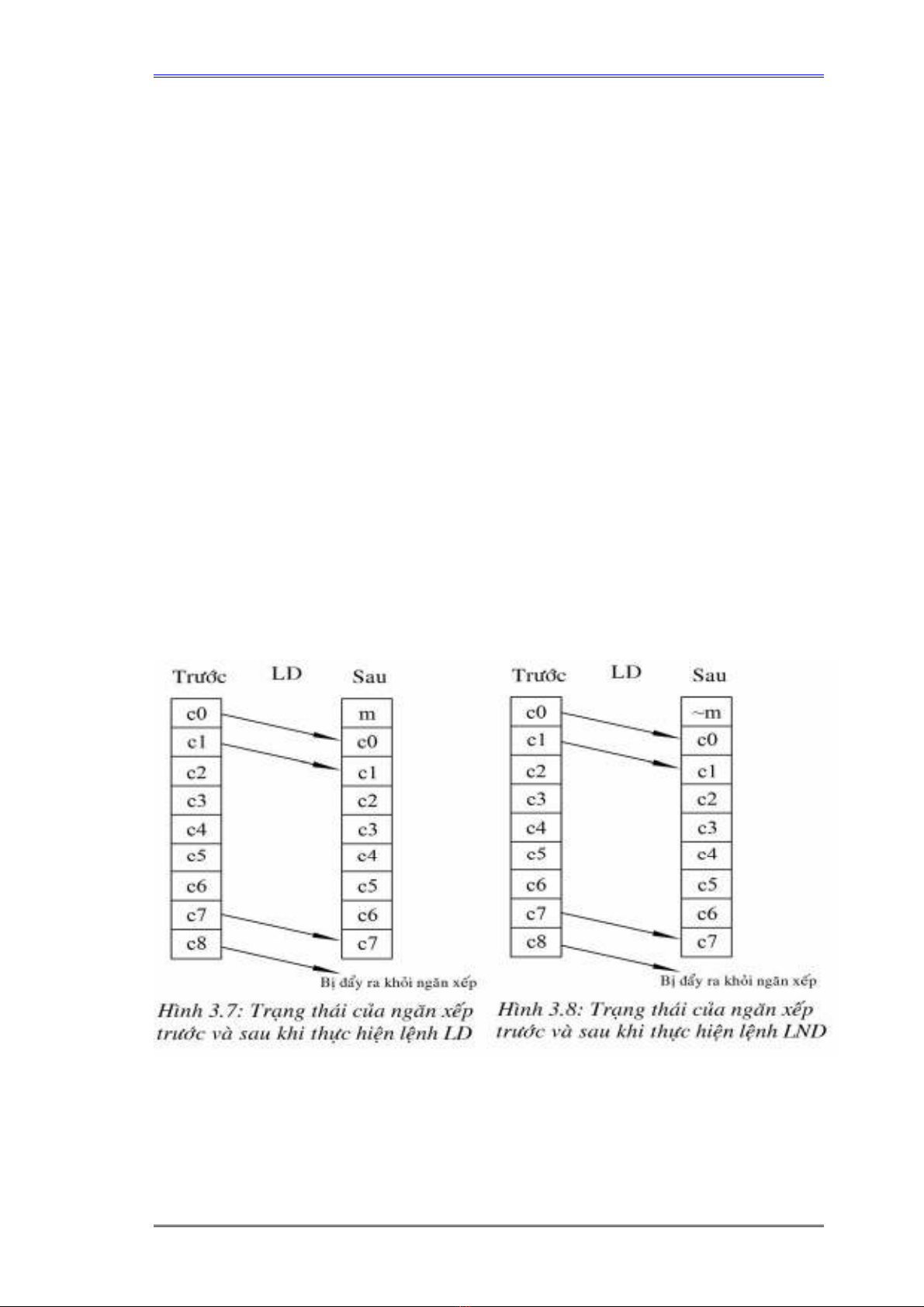

Load(LD): LÖnh LD n¹p gi¸ trÞ logic cña mét tiÕp ®iÓm vµo trong bit ®Çu tiªn

cña ng¨n xÕp, c¸c gi¸ trÞ cò cßn l¹i trong ng¨n xÕp bÞ ®Èy lïi xuèng mét bit (H×nh

3.7).

Load Not(LD): LÖnh LDN n¹p gi¸ trÞ logic nghÞch ®¶o cña mét tiÕp ®iÓm vµo

trong bit ®Çu tiªn cña ng¨n xÕp, c¸c gi¸ trÞ cò cßn l¹i trong ng¨n xÕp bÞ ®Èy lïi xuèng

mét bit (H×nh 3.8).

B¸o c¸o tèt nghiÖp t« kim hïng – tù ®éng 46

Tr−êng ®hnni – hµ néi khoa c¬ ®iÖn

52

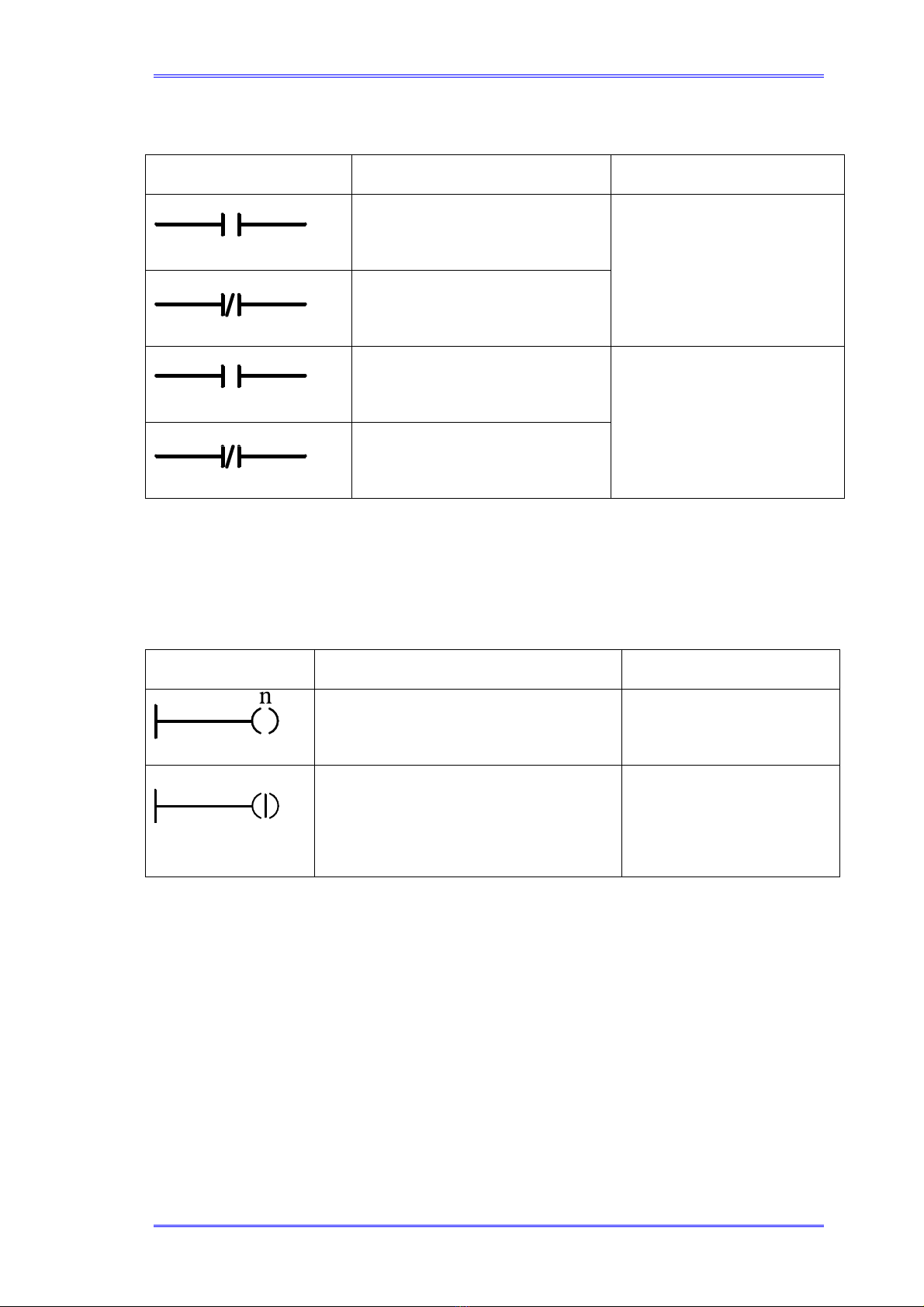

C¸c d¹ng kh¸c nhau cña lÖnh LD, LDN cho LAD nh− sau:

LAD M« t¶ To¸n h¹ng

n

TiÕp ®iÓm th−êng më sÏ

®−îc ®ãng nÕu n=1

n

TiÕp ®iÓm th−êng ®ãng sÏ

më khi n=1

n:I,Q,M,SM,T,C,V (bit)

n

TiÕp ®iÓm th−êng më sÏ

®ãng tøc thêi khi n=1

n

TiÕp ®iÓm th−êng ®ãng sÏ

më tøc thêi khi n=1

n:I (bit)

OUTPUT (=) LÖnh sao chÐp néi dung cña bit ®Çu tiªn trong ng¨n xÕp

vµo bit ®−îc chØ ®Ønh trong lÖnh. Néi dung cña ng¨n xÕp kh«ng bÞ thay ®æi.

LAD M« t¶ To¸n h¹ng

Cuén d©y ®Çu ra ë tr¹ng th¸i kÝch

khi cã dßng ®iÒu khiÓn ®i qua

n:I,Q,M,SM,T,C,V(bit)

n

Cuén d©y ®Çu ra ®−îc kÝch tøc

thêi khi cã dßng ®iÒu khiÓn ®i

qua

n: Q (bit)

2. LÖnh ghi/xo¸ gi¸ trÞ cho tiÕp ®iÓm

SET(R)

RESET(R) LÖnh dïng ®Ó ®ãng vµ ng¾t c¸c tiÕp ®iÓm gi¸n ®o¹n ®·

®−îc thiÕt kÕ.

Trong LAD, logic ®iÒu khiÓn dßng ®iÖn hoÆc c¸c cuén d©y ®Çu ra. Khi

dßng ®iÒu khiÓn ®Õn c¸c cuén d©y th× c¸c cuén d©y ®ãng hoÆc më c¸c tiÕp

®iÓm (hoÆc mét dÉy c¸c tiÕp ®iÓm).

Trong STL, lÖnh truyÒn tr¹ng th¸i bÝt ®Çu c¶u ng¨n xÕp ®Õn c¸c ®iÓm

B¸o c¸o tèt nghiÖp t« kim hïng – tù ®éng 46

Tr−êng ®hnni – hµ néi khoa c¬ ®iÖn

53

thiÕt kÕ. NÕu bit nµy cã gi¸ trÞ b»ng 1, c¸c lÖnh S vµ R sÏ ®ãng ng¾t tiÕp ®iÓm

hoÆc mét dÉy c¸c tiÕp ®iÓm (giíi h¹n tõ 1 ®Õn 255). Néi dung cña ng¨n xÕp

kh«ng bÞ thay ®æi.

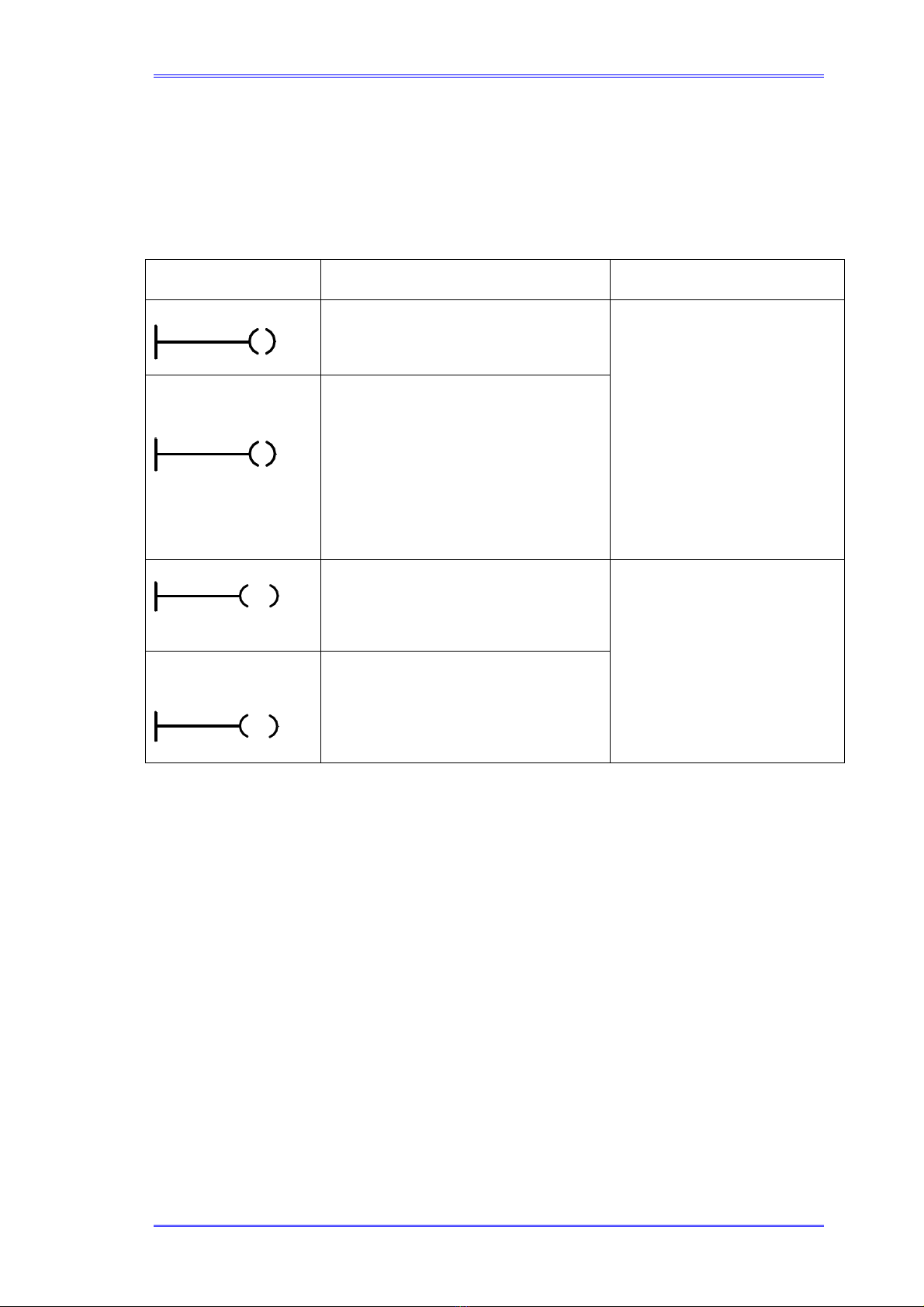

M« t¶ S vµ R b»ng LAD:

LAD M« t¶ To¸n h¹ng

n

s_bit

s

§ãng mét m¶ng gåm c¸c tiÕp

®iÓm kÓ tõ S_BIT

n

s_bit

r

Ng¾t mét m¶ng gåm n c¸c tiÕp

®iÓm kÓ tõ S_BIT. NÕu S_BIT

l¹i chØ vµo Timer hoÆc Counter

th× lÖnh sÏ xãa bit ®Çu ra cña

Timer/Counter ®ã

S_BIT:I,Q,M,SM,T,C,V

(bit)

n: IB,QB,MB,SMB,VB

(byte)

AC,h»ngsè,*VD,*AC

n

s_bit

s_bit

s i

§ãng tøc thêi mét m¶ng gåm

n c¸c tiÕp ®iÓm kÓ tõ S_BIT

n

s_bit

r i

Ng¾t tøc thêi mét m¶ng gåm n

c¸c tiÕp ®iÓm kÓ tõ ®Þa chØ

S_BIT

S_BIT: Q(bit)

n: IB,QB,MB,SMB,VB

(byte)

AC, h»ng sè, *VD,*AC

3. C¸c lÖnh so s¸nh

Khi lËp tr×nh nÕu, cã c¸c quyÕt ®Þnh vÒ ®iÒu khiÓn ®−îc thùc hiÖn dùa trªn kÕt

qu¶ cña viÖc so s¸nh th× cã thÓ sö dông lÖnh so s¸nh cho byte, tõ kÐp cña S7 -200.

LAD sö dông lÖnh so s¸nh ®Ó c¸c gi¸ trÞ cña byte, tõ vµ tõ kÐp (gi¸ trÞ thùc

hoÆc nguyªn). Nh÷ng so s¸nh th−êng lµ nhá h¬n hoÆc b»ng (<=); so s¸nh (=) vµ so

s¸nh lín h¬n hoÆc b»ng (>=).

Khi so s¸nh gi¸ trÞ cña byte th× kh«ng cÇn ph¶i ®Ó ý ®Õn dÊu cña to¸n h¹ng.

Ng−îc l¹i khi so s¸nh c¸c tõ hoÆc tõ kÐp víi nhau th× ph¶i ®Ó ý ®Õn dÊu cña to¸n

h¹ng lµ bÝt cao nhÊt trong tõ hoÆc tõ kÐp.

B¸o c¸o tèt nghiÖp t« kim hïng – tù ®éng 46

Tr−êng ®hnni – hµ néi khoa c¬ ®iÖn

54

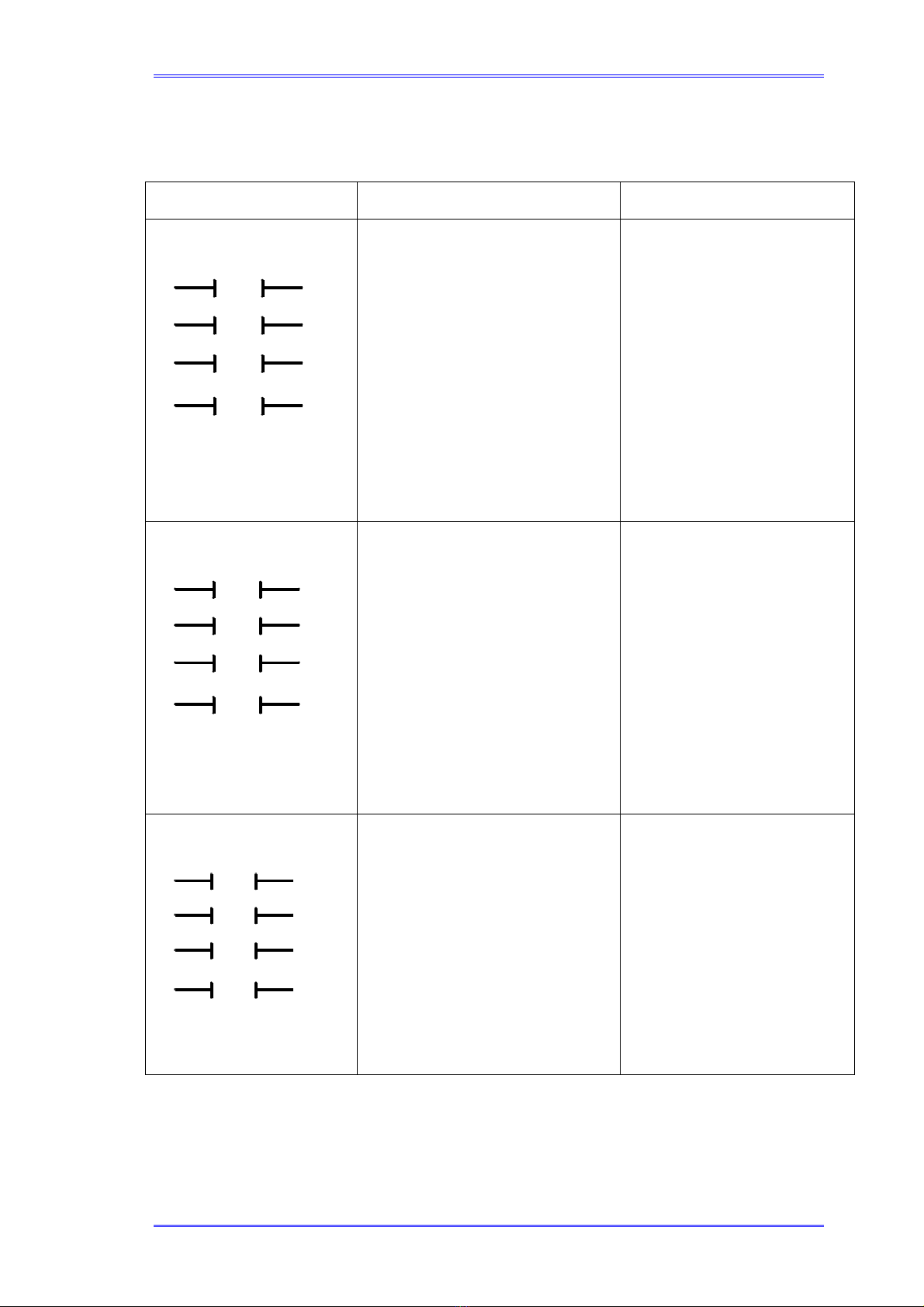

BiÓu diÔn c¸c lÖnh so s¸nh trong LAD:

LAD Moâ taû Toaùn haïng

n1 n2

= = B

= = I

n1 n2

= = D

n1 n2

= = R

n1 n2

Tieáp ñieåm ñoùng khi n1 = n2

B = Byte

I = Integer

D = Double Integer

R = Real

n1,n2 (byte) :VB, IB, QB,

MB, SMB, AC, H»ng sè,

*VD, *AC

n1

n1 > = R

> = D

n1 > = I

> = B

n1

n2

n2

n2

n2

Tieáp ñieåm ñoùng khi n1> n2

B = Byte

I = Integer

D = Double Integer

R = Real

n1,n2(word):VW, T, C, I,

QW, MW, SMW, AC, AI,

Haèng soá, *VD, *AC

n1

n1

n1

n1

n2

n2

< = R

< = D

n2

< = I

< = B n2

Tieáp ñieåm ñoùng khi n1≤ n2

B = Byte

I = Integer

D = Double Integer

R = Real

n1,n2: VD, ID, QD, MD,

SMD, AC, HC, h»ng sè,

*VD, *AC.

B¸o c¸o tèt nghiÖp t« kim hïng – tù ®éng 46

Tr−êng ®hnni – hµ néi khoa c¬ ®iÖn

55

4 C¸c lÖnh ®iÒu khiÓn Timer

Timer lµ bé t¹o thêi gian trÔ gi÷a tÝn hiÖu vµo vµ tÝn hiÖu ra nªn trong

®iÒu khiÓn vÉn th−êng ®−îc gäi lµ kh©u trÔ. NÕu ký hiÖu tÝn hiÖu (logic) vµo lµ

x(t) vµ thêi gian trÔ ®−îc t¹o ra b»ng Timer lµ T th× tiÕn hiÖu ®Çu ra cña Timer

®ã sÏ lµ x(t-T).

S7-200 cã rÊt nhiÒu Timer kh¸c nhau vµ ®−îc chia lµm hai lo¹i kh¸c

nhau, ®ã lµ:

- Timer t¹o thêi gian kh«ng cã nhí (On-Delay Timer), ký hiÖu lµ

TON.

- Timer t¹o thêi gian cã nhí(Retentive On-Delay Timer), ký hiÖu lµ

TONR.

Hai kiÓu Timer cña S7-200 (TON vµ TONR) ph©n biÖt víi nhau ë ph¶n

øng cña nã ®èi víi tr¹ng th¸i tÝn hiÖu ®Çu vµo.

C¶ hai Timer kiÓu TON vµ TONR cïng b¾t ®Çu t¹o thêi gian trÔ tÝn hiÖu

kÓ tõ thêi ®iÓm cã s−ên lªn ë tÝn hiÖu vµo, tøc lµ khi ®Çu vµo chuyÓn tr¹ng

th¸i logic tõ 0 lªn 1, ®−îc gäi lµ thêi ®iÓm Timer ®−îc kÝch, vµ kh«ng tÝnh

kho¶ng thêi gian khi ®Çu vµo cã gi¸ trÞ logic 0 vµo thêi gian trÔ tÝn hiÖu

®−îc ®Æt tr−íc.

Khi ®Çu vµo cã gi¸ trÞ logic b»ng 0, TON tù ®éng Reset cßn TONR th×

kh«ng tù ®éng Reset. Timer TON ®−îc dïng ®Ó t¹o thêi gian trÔ trong mét thêi

gian (miÒn liªn tôc th«ng), cßn TONR thêi gian trÔ sÏ ®−îc t¹o trong nhiÒu

kho¶ng thêi gian kh¸c nhau.

Timer TON vµ TONR bao gåm 3 lo¹i víi ba bé ph©n gi¶i kh¸c nhau, ®é

ph©n gi¶i 1ms, 10ms, 100ms. Thêi gian trÔ T t¹o ra chÝnh lµ tÝch cña ®é ph©n gi¶i

cña bé Timer ®−îc chän vµ gi¸ trÞ ®Æt tr−íc cho Timer. VÝ dô mét bé Timer cã

®é ph©n gi¶i b»ng 10ms vµ gi¸ trÞ ®Æt tr−íc lµ 50 th× thêi gian trÔ sÏ lµ T=500ms.

![Thu truyền hình cáp trên máy vi tính [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130322/bibocumi35/135x160/1390540_056.jpg)