Tuyển tập Hội nghị Khoa học thường niên năm 2024. ISBN: 978-604-82-8175-5

282

THIẾT KẾ VÀ MÔ PHỎNG MẠCH KHUẾCH ĐẠI

TẠP ÂM THẤP CHO BỘ THU SÓNG WIFI 5G

Đoàn Hữu Chúc, Trần Văn Hội

Trường Đại học Thủy lợi, email: chucdh@tlu.edu.vn

1. GIỚI THIỆU CHUNG

Ngày nay, hệ thống truyền thông sử dụng

sóng siêu cao tần đóng vai trò quan trọng

trong sự phát triển của việc truyền thông tin.

Trong hệ thống siêu cao tần, bộ khuếch đại là

thành phần cơ bản và phổ biến. Các transistor

trong bộ khuếch đại có thể hoạt động trong

khoảng tần số rất rộng lên tới 100 GHz ở

những ứng dụng yêu cầu kích thước nhỏ gọn,

hệ số tạp âm NF thấp, dải thông rộng và tiêu

hao năng lượng thấp. Kỹ thuật thiết kế mạch

khuếch đại sử dụng BJT và FET dựa trên các

khái niệm được nghiên cứu về đường truyền

sóng siêu cao tần, mạng hai cổng và giản đồ

Smith. Trong lĩnh vực siêu cao tần, lý thuyết

mạch thông thường không thể sử dụng trực

tiếp để giải quyết các vấn đề của mạng siêu

cao tần. Trong trường hợp đó, lý thuyết mạch

thông thường được gần đúng hoặc sử dụng lý

thuyết trường điện từ được mô tả bằng các

phương trình Maxwell. Điều đó có nghĩa cách

thức thiết kế ở mạch siêu cao tần khác biệt so

với khi thiết kế mạch ở tần số thấp. Điều này

được gọi là kỹ thuật phối hợp trở kháng [1,2].

Khi thiết kế mạch khuếch đại dùng transistor

chúng ta phải dựa trên tham số S. Khối xử lý

tín hiệu đầu tiên của bộ thu trong hệ thống

truyền thông sau anten là bộ khuếch đại tạp

âm thấp (Low Noise Amplifier viết tắt là

LNA). Mạch LNA sẽ khuếch đại tín hiệu thu

được với hệ số khuếch đại hợp lý và có tạp

nhiễu nhỏ nhất có thể.

Tiêu chuẩn IEEE 802.11 ac được xem là

tiêu chuẩn dành cho thế hệ mạng Wifi thứ 5,

thường gọi tắt là mạng Wifi 5G[3]. Công

nghệ phát sóng wifi hiện đại sử dụng các tần

số là 2,4 GHz và 5 GHz[3]. Thiết kế mạch

khuếch đại tín hiệu tạp âm thấp LNA là

nhiệm vụ quan trọng nhất trong bộ thu. Mạch

LNA phải đảm bảo có hệ số khuếch đại tín

hiệu đủ lớn và tạp nhiễu nhỏ nhất. Việc thiết

kế mạch LNA cần cân bằng giữa các thông

số như hệ số khuếch đại, các hệ số phản xạ,

nhiễu và công suất tiêu thụ.

Hình 1. Sơ đồ khối bộ thu tín hiệu siêu cao tần

Bài báo này trình bày việc thiết kế và mô

phỏng một mạch LNA sử dụng cho mạng

wifi 5G. Mạch có hệ số khuếch đại đạt 18dB,

hệ số phản xạ lối vào là -19.2 dB, hệ số phản

xạ lối ra là -10.88 dB, tỷ số sóng đứng điện

áp (Voltage Standing Wave Ratio viết tắt là

VSWR) bằng 1.244 và nhiễu hình (Noise

Figure viết tắt là NF) nhỏ nhất NFmin nhỏ

hơn 0.6 tại tần số thiết kế 5GHz.

2. PHƯƠNG PHÁP NGHIÊN CỨU

Để đạt được mục tiêu nghiên cứu, tác giả

sử dụng các phương pháp như phân tích, tổng

hợp, phương pháp mô hình hóa và phương

pháp thực nghiệm để kiểm chứng kết quả.

3. THIẾT KẾ VÀ MÔ PHỎNG

Mạch khuếch đại Transistor đơn tầng với

mạch phối hợp trở kháng đầu vào và ra được

biểu diễn như ở hình 2[1-3]. Mạch khuếch đại

LNA hoạt động ở tần số 5GHz, sử dụng

transistor SPF3043 được thiết kế và mô phỏng

trên phần mềm ADS. Quá trình thiết kế các

Tuyển tập Hội nghị Khoa học thường niên năm 2024. ISBN: 978-604-82-8175-5

283

mạch phối hợp trở kháng, hệ số khuếch đại

cũng như hệ số tạp âm NF, được thực hiện dựa

trên các tham số S của SPF3043. Các tham số

S của transistor được tra cứu từ nhà sản xuất.

Với mục đích thiết kế mạch LNA sử dụng cho

bộ thu tín hiệu mạng Wifi 5G, tác giả chọn tần

số mạch hoạt động có giá trị là 5 GHz.

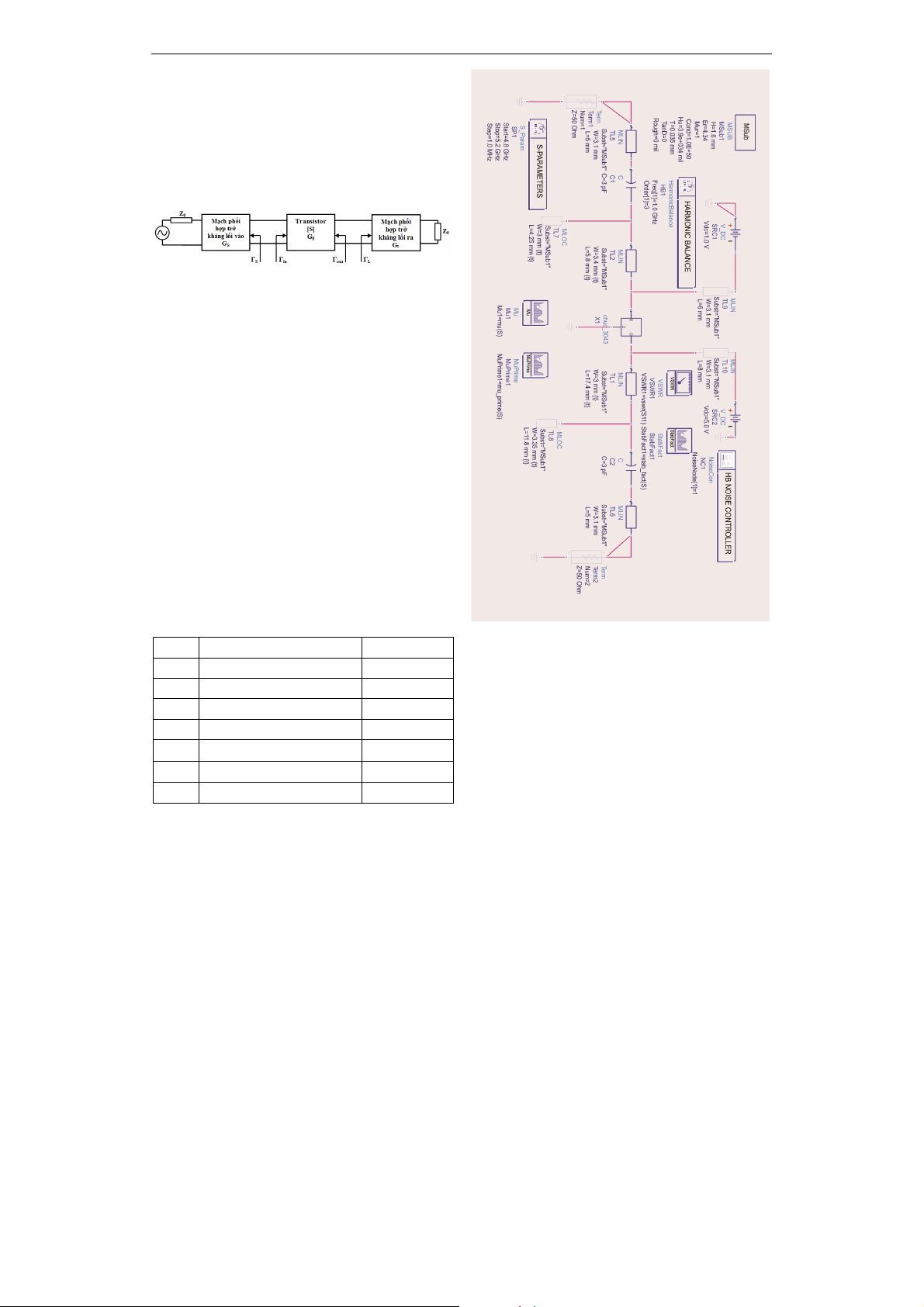

Hình 2. Sơ đồ khối mạch khuếch đại

tạp âm thấp

Từ các tham số S tra cứu được, ta lần lượt

có được trở kháng lối và và trở kháng lối ra

của SPF3043 tại tần số trung tâm f = 5 GHz là:

Z

in = 20.9 - j*23.9 ()

Z

out = 54.8 - j*36.35 ()

trong đó:

Zin là trở kháng lối vào, Zout là trở kháng

lối ra và j là đơn vị phức.

Có nhiều phương pháp thực hiện thiết kế

mạch phối hợp trở kháng cho LNA. Trong

trường hợp này, để giảm kích thước của

mạch và tăng tính lựa chọn tần số chúng ta sử

dụng phương pháp sử dụng đoạn dây chêm

hở mạch. Chi tiết các thông số thiết kế của

mạch LNA được đưa ra ở bảng 1 dưới đây.

Bảng 1. Các thông số thiết kế

STT Thông số Đơn vị

1 Tần số trung tâm 5 GHz

2 Dải thông ± 5%

3 Tạp nhiễu NF < 2dB

4 Hệ số khuếch đại > 15 dB

5 Trở kháng nguồn 50

6 Trở kháng tải 50

7 Transistor SPF3043

Sử dụng công cụ LineCal xác định được

kích thước của mạch phối hợp trở kháng khi

sử dụng loại phíp đồng FR4 có hằng số điện

môi =4,34; độ dày H=1,6mm và độ dày lớp

dẫn điện T=0,035mm. Sơ đồ nguyên lý mạch

phối hợp trở kháng lối vào và lối ra cho LNA

thiết kế trên phần mềm ADS 2020 được đưa

ra ở hình 3 dưới đây.

Hình 3. Sơ đồ nguyên lý chi tiết mạch

khuếch đại tạp âm thấp dùng SPF3043

Từ các giá trị trở kháng vào và trở kháng

ra chúng ta thực hiện tính toán các đoạn dây

chêm cho mạch phối hợp trở kháng lối vào và

lối ra của LNA. Trên cơ sở công cụ phỏng

phỏng của phần mềm ADS2020 ta hiệu chỉnh

để được kết quả mô phỏng một cách tối ưu

nhằm cân bằng các giá trị đạt được.

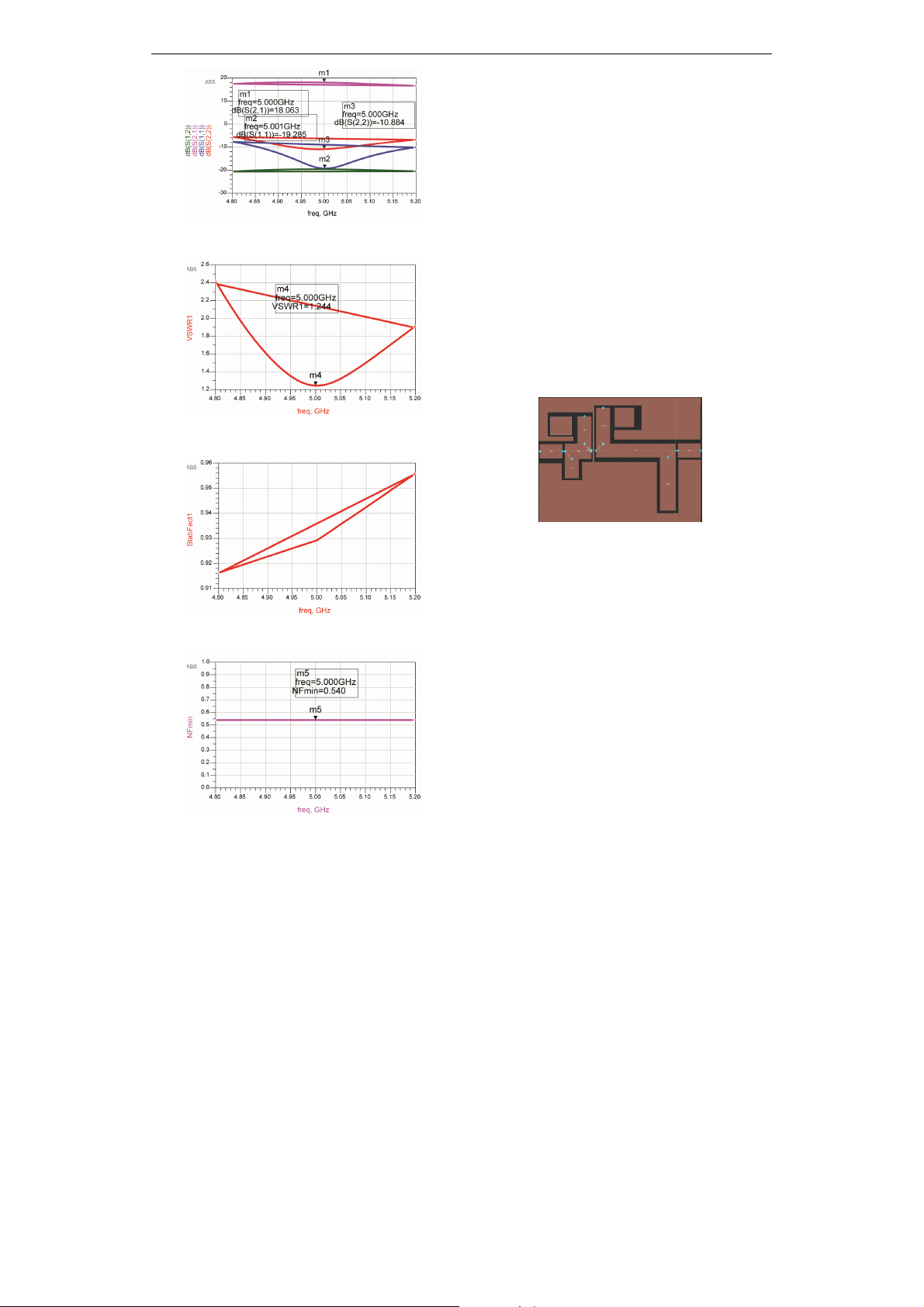

Kết quả mô phỏng các giá trị tham số S

được đưa ra ở hình 4. Theo đó hệ số khuếch

đại lớn hơn 17.8 dB trong dải tần từ 4,95 GHz

đến 5,05 GHz. Đây là giá trị lớn đối với mạch

khuếch đại đơn tầng. Giá trị này thỏa mãn yêu

cầu thiết kế đặt ra. Kết quả mô phỏng hệ số

sóng đứng, hệ số ổn định và nhiễu hình nhỏ

nhất đưa ra trên các hình 5, 6 và 7.

Tuyển tập Hội nghị Khoa học thường niên năm 2024. ISBN: 978-604-82-8175-5

284

Hình 4. Kết quả mô phỏng các tham số S

Hình 5. Kết quả mô phỏng VSWR

Hình 6. Kết quả mô phỏng hệ số ổn định

Hình 7. Kết quả mô phỏng nhiễu hình

Hệ số phản xạ lối vào S11< -15 dB trong

dải tần 4,95 GHz đến 5,05 GHz. Điều đó có

nghĩa là mạch được phối hợp trở kháng rất

tốt. Hệ số phản xạ lối ra S22 < -10 dB cũng

trong dải tần như trên. Do đó mạch phối hợp

trở kháng lối ra cũng được thiết kế tốt.

Hệ số sóng đứng như thể hiện ở hình 5

bằng 1,244 dB gần đạt tới giá trị bằng 1 vì

vậy hệ số phản xạ thấp. Giá trị lý tưởng bằng

1 tức hệ số phản xạ bằng 0. Hệ số ổn định

K<1 trong khoảng dải tần từ 4,9 GHz đến 5,1

GHz cho thấy mạch khuếch đại đạt điều kiện

ổn định vô điều kiện.

Một thông số quan trọng nữa là hệ số

nhiễu hình. Theo hình 7 kết quả mô phỏng

nhiễu hình nhỏ nhất NFmin =0,54, điều này

nghĩa là hệ số khuếch đại lối ra đủ lớn đảm

bảo cho việc chế tạo mạch LNA.

Sau khi thiết kế và mô phỏng chúng ta thực

hiện thiết kế mạch in. Sơ đồ thiết kế mạch in

của LNA được đưa ra ở hình 8. Từ sơ đồ

nguyên lý mạch in này chúng ta có thể tiếp tục

thực hiện chế tạo và đo kiểm thực nghiệm.

Hình 8. Sơ đồ mạch in

4. KẾT LUẬN

Một mạch LNA sử dụng SPF3043 hoạt

động ở tần số trung tâm 5GHz đã được thiết

kế và mô phỏng với hệ số khuếch đại lớn hơn

18 dB, hệ số phản xạ lối vào nhỏ hơn -19 dB,

hệ số phản xạ lối ra nhỏ hơn -10 dB. Mạch

cũng có hệ số sóng đứng và tạp âm nhỏ đáp

ứng yêu cầu của một mạch khuếch đại LNA.

Do đó có thể ứng dụng mạch cho hệ thống

wifi 5G cũng như cho các hệ thống thu phát

siêu cao tần khác.

5. TÀI LIỆU THAM KHẢO

[1] David M. Pozar (2012), Microwave

Engineering, Fourth Edition, John Wiley &

Sons, Inc.

[2] T. V. Hoi, et al., “Design and Fabrication of

High Gain Low Noise Amplifier at 4Ghz,”

International Journal of Engineering and

Innovation Technology (IJEIT), vol/issue:

4(7), 2015.

![Tài liệu CCS4 DSP Workshop ĐH Công nghiệp [CHUẨN SEO]](https://cdn.tailieu.vn/images/document/thumbnail/2014/20141221/dinhbinh296/135x160/5111419134904.jpg)