1

P&I-Ch1:Architecture 1

Ch.1 Kiến trúc hệVXL – MT

Kiến trúc thiết bịhệkinh điển, các hệnhúng

Kiến trúc hệmáy tính ‘Hi Performance’ - desktop

Hoạtđộng của hệthống.

P&I-Ch1:Architecture 2

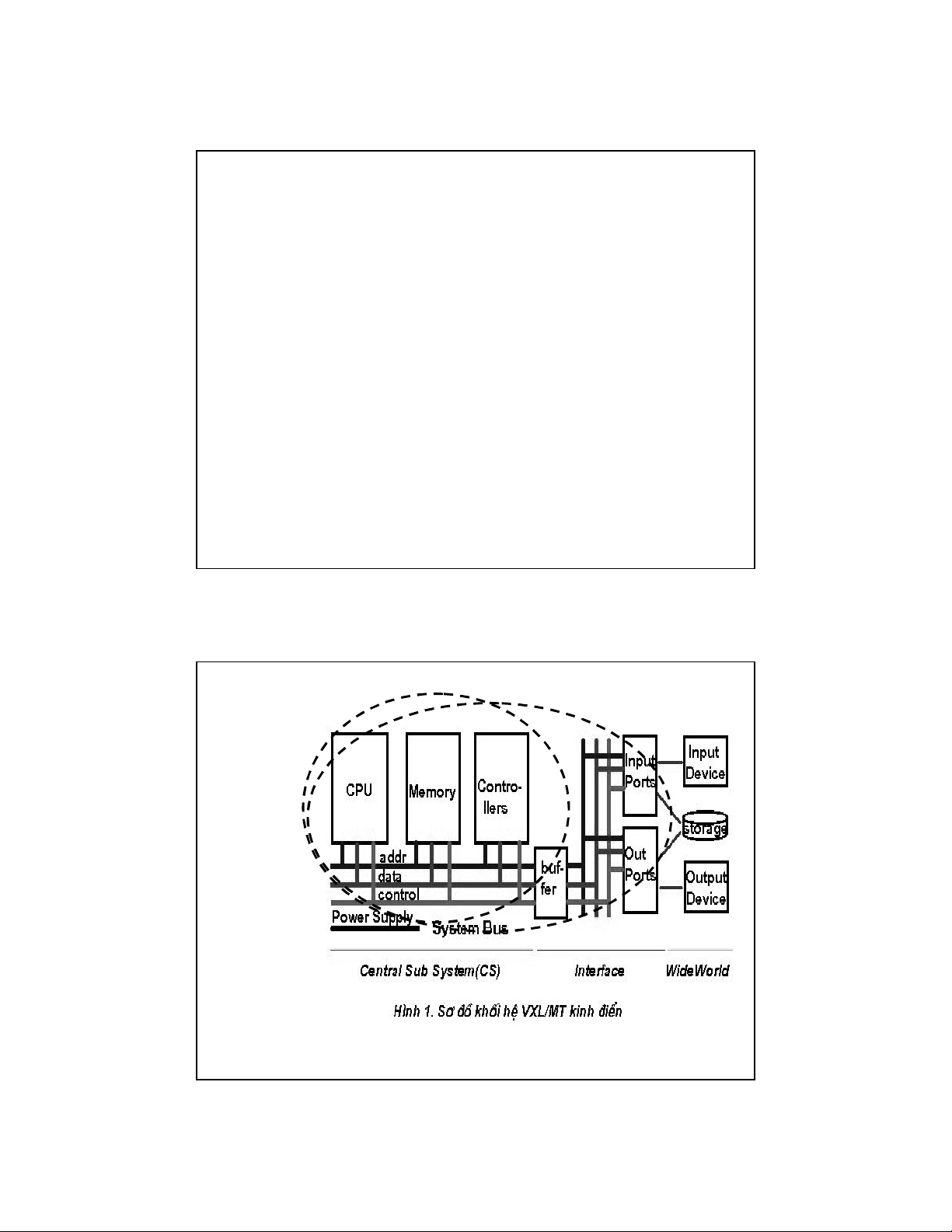

1.1. Kiến trúc HệVXL, Máy tính kinh điển – Embedded systems

1.1.1. Sơ đồ:

3 phần:

- CS,

- Ngoại vi &

- Interface

2

P&I-Ch1:Architecture 3

1.1.1. a. Central Sub System – CS:

+ CPU: Central Processing Unit:

•Khái niệm: Là bộ điều khiển trung tâm, thực hiện

công việcđược giao đặt trong bộnhớ chương trình

bằng cách thực hiện các phép xửlý lên các biến nhị

phân và điều khiển thiết bịngoại vi.

•Công việc bao gồm:

–Tìm lệnh, giải mã lệnh, [tìm toán hạng, xửlý và cất kết

quả],

–In/Out với các port kiểu Interrupt và DMA để điều khiển

thiết bịngoại vi.

P&I-Ch1:Architecture 4

Đặctrưng – Specifications:

•Kích thước toán hạng (bit): 4, 8, 12, 16, 32, 64...

•Tốcđộ xửlý: Mips/Gips, clock multiplier,

•Kiến trúc:

–RISC (Reduced Instruction Set Computer)vs CISC (Complex

Instruction Set Computer),

–DSP – Digital Signal Processor,

–Micro Controller (Micro Computer One Chip - All in one):

•Atmel: ATmega nnn (8bit, RISC), AT91SAMnnn (ARM core)

•MicroChip, PICxxx

•Cypress: PSoC...

•Pinning/Signalling (Data/Address - Mux, Control bus, IRQ, HRQ,

RD/WR...),

•Register set,

•Instruction set – Addressing Modes,

•Power Modes: Slow/ sleep/ power down modes, Mips/Wattage

•...

3

P&I-Ch1:Architecture 5

+ Memories (Semiconductor): K/n & ROM:

Khái niệm:

•Lưu thông tin (ch/tr và sốliệu) dạng nhịphân,

•Dung lượng lớn (upto 100s Mega bit), tốcđộ truy

nhập nhanh (downto ns access time).

–Physically: tính chất vật lý như thếnào?

•ROMs: Mask ROM, PROM, EPROM, EAROM, OTROM,

NonVolatile mem, ...

•Là bộnhớchỉ đọc, vẫnlưu thông tin khi mấtđiện,

•Package : byte

•Access time:100..120ns

•Ghi/nạp nội dung: T/bịchuyên dùng (ROM Burner

/Programmator)

•Shadow ROM?: copy nội dung từROM sang DRAM mỗi khi khởi

động

P&I-Ch1:Architecture 6

•Lưu thông tin tạm thời, không lưu được khi mấtđiện,

đọc và ghi được, [Read/Write Mem],

- Static RAM:

nhanh (80..3 ns),

byte/nibble package,

mậtđộ byte/chip nhỏ(upto 64/256 KB/ chip),

đắt, tiêu thụcông suất nhiều,

- CMOS RAM: chậm và tiêu thụcực ít, less W.

Vdụ: MC 146818 RealTimeClock-CMOS RAM

• Dùng trong các hệnhỏ, cache memory.

Memories (Semiconductor): SRAM

4

P&I-Ch1:Architecture 7

Memories (Semiconductor): DRAM

Dynamic RAM - DRAM:

Tốcđộ/Access time (50-70ns), [10..20ns] Pre-fetched

Mậtđộ: bit/chip >> (1 Gbit/chip – 1996, Korea),

bit package => DRAM bank,

Tiêu thụW, công suất nhỏ.

Thông tin chỉ lưu được 10ms => refreshing DRAM với chu

ký @ 7,5ms => phức tạp.

Dùng trong các hệcó dung lượng nhớlớn: desktop, laptop,

server…

P&I-Ch1:Architecture 8

Memories (Semiconductor): FLASH & Others

Flash memory:

- EAROM typed, đọcđược, xoá từng bank, ghi lạiđược từng byte.

- Thông tin lưu được 20 năm, dùng nhiều hiện tại và tương lai:

BIOS, diskchip, USB stick Mem, uC...

- Serial EAROM/FLASH: dùng để lưu configuration, dùng bus

I2C (Philips). Ví dụ ứng dụng : thẻvi mạch, TV, ...

Dual [Quad] Ported RAM: Switching Sys., PGA

•RAM-DAC: VGA, VoiceChip

•PCMCIA

•....

5

P&I-Ch1:Architecture 9

Memories (Semiconductor): Logically:

Bộnhớ chưa thông tin gì?

Program memory:

Chứa ch/tr đang thực hiện

Data memory:

Các biến ngẫu nhiên, các biến có cấu trúc,

các sốliệu có kiểu truy nhậpđặc biệt (FIFO, LIFO…)

P&I-Ch1:Architecture 10

+Controllers: [Optional], vi mạch, nâng hiệu nang

(performance) hệthống, bao gồm:

- Bộ điều khiểnưu tiên ngắt PIC – Priority Interrupt

Controller, Intel 8259A

- Bộ điều khiển truy nhập trực tiếp bộnhớDMAC –

Direct memory Access Controller, Intel 8237A.

- Timer: mạch tạo các khoảng thời gian, PIT-

Programmable Interval Timer, Intel 8254.

- Mạch quản trịnhớ: MMU- Memory Management

Unit, sau này, thường được built on chip với CPU.

Bus controller/Arbitor

![Bài tập Lập trình C++: Tổng hợp [kinh nghiệm/mới nhất/chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250826/signuptrendienthoai@gmail.com/135x160/45781756259145.jpg)