1

Chương 4

MẠCH TỔ HỢP

2

Mục tiêu

Trang bị nguyên lý:

Phân tích

Thiết kế

các mạch tổ hợp

Cung cấp các kiến thức cơ bản về:

Cấu tạo

Nguyên lý hoạt động

Ứng dụng

của các mạch tổ hợp

3

Nội dung

Khái niệm chung và mô hình toán học

Phân tích và thiết kế mạch tổ hợp

Một số mạch tổ hợp cơ bản

4

4.1 Khái niệm chung và mô hình toán

học

Khái niệm chung:

Mạch tổ hợp là một mạch điện tử số

Tín hiệu đầu ra của mạch tại thời điểm xét chỉ phụ

thuộc vào tín hiệu vào tại thời điểm đó

Mạch tổ hợp không có nhớ

Mạch tổ hợp chỉ cần thực hiện bằng những phần

tử logic cơ bản

5

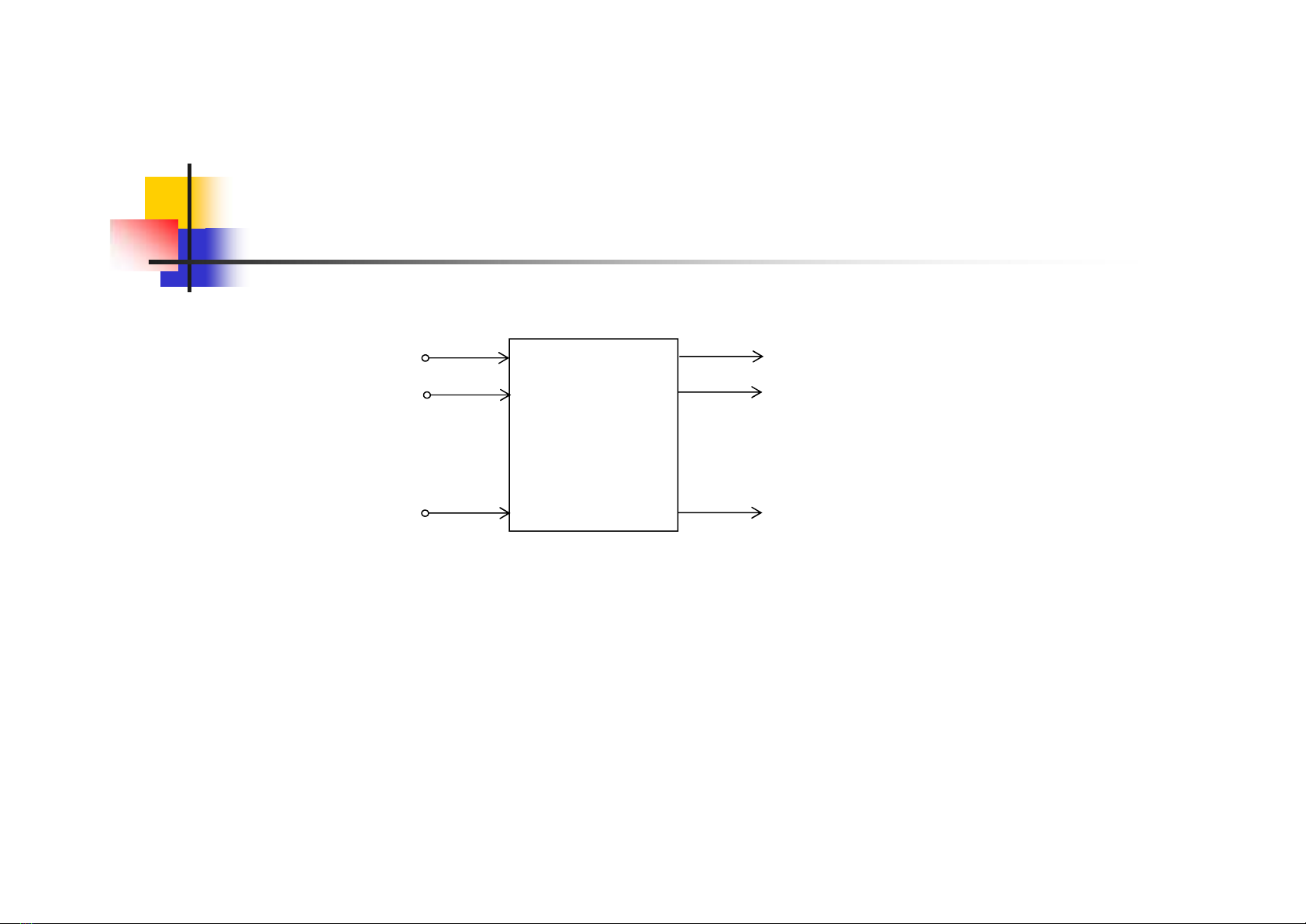

Mô hình toán học của mạch tổ hợp

X = (x1, x2, … , xn) là tập các tín hiệu vào có giá trị 0 hoặc 1

Y = (y1, y2, … , ym) là tập các tín hiệu ra có giá trị 0 hoặc 1

Quan hệ toán học của mạch tổ hợp là:

với mọi

Mạch

tổ hợp

x1

x2

xn

y1

y2

ym

.

.

.

.

.

.

),...,,( 21 njj xxxfy

mj

1

![Bài giảng Nhập môn mạch số: Chương 3 (Phần 2) - TS. Trịnh Lê Huy [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250515/hoatrongguong03/135x160/38491750824827.jpg)

![Bài giảng Nhập môn Kỹ thuật điện [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251208/nguyendoangiabao365@gmail.com/135x160/60591765176011.jpg)