1

NGÔN NGỮ VERILOG

Chương 2

2

I. GIỚI THIỆU

Trường ĐH Bách Khoa TP.HCM

1.1. Ngôn ngữmô tảphầncứng HDL

(Hardware Description Language)

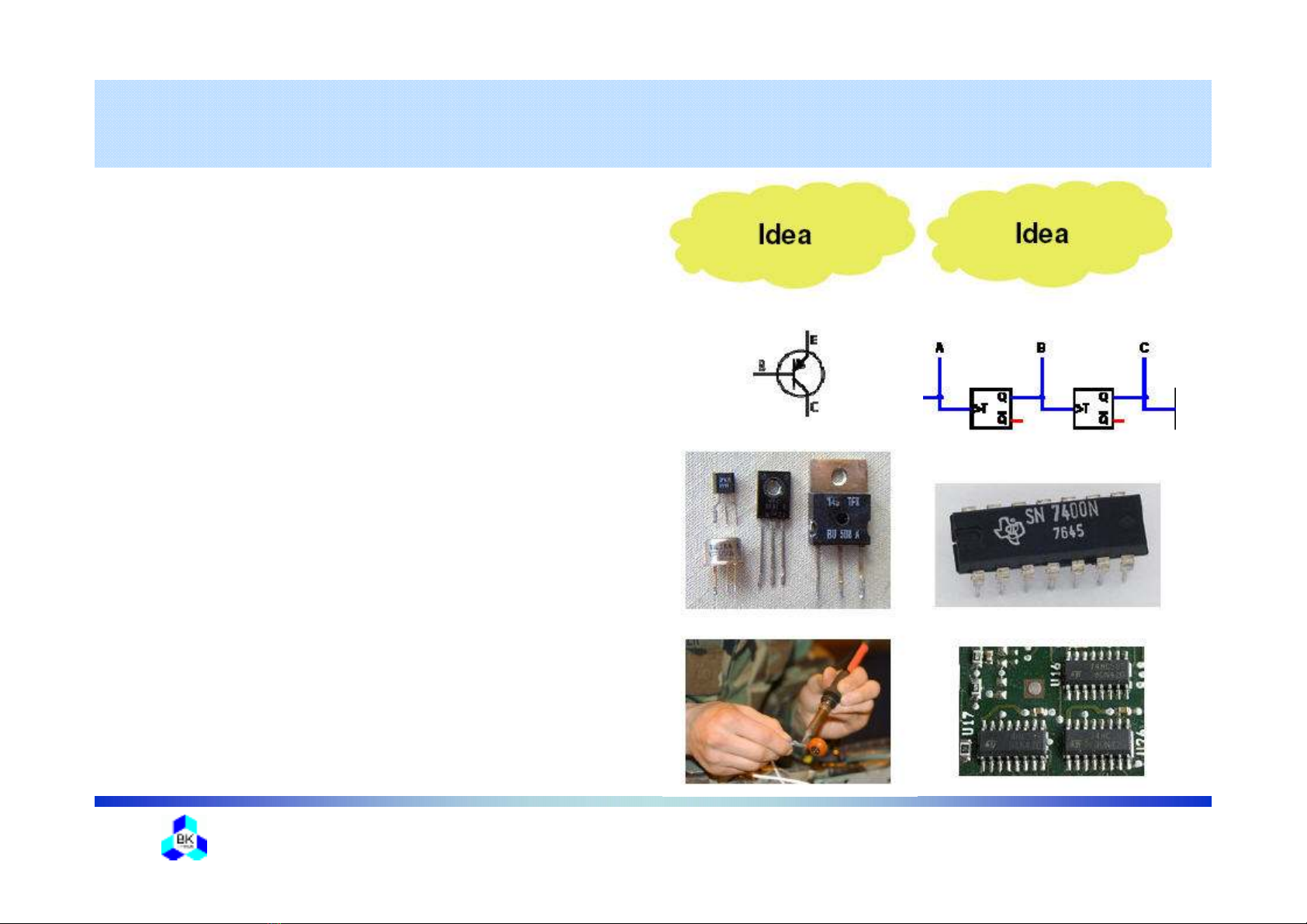

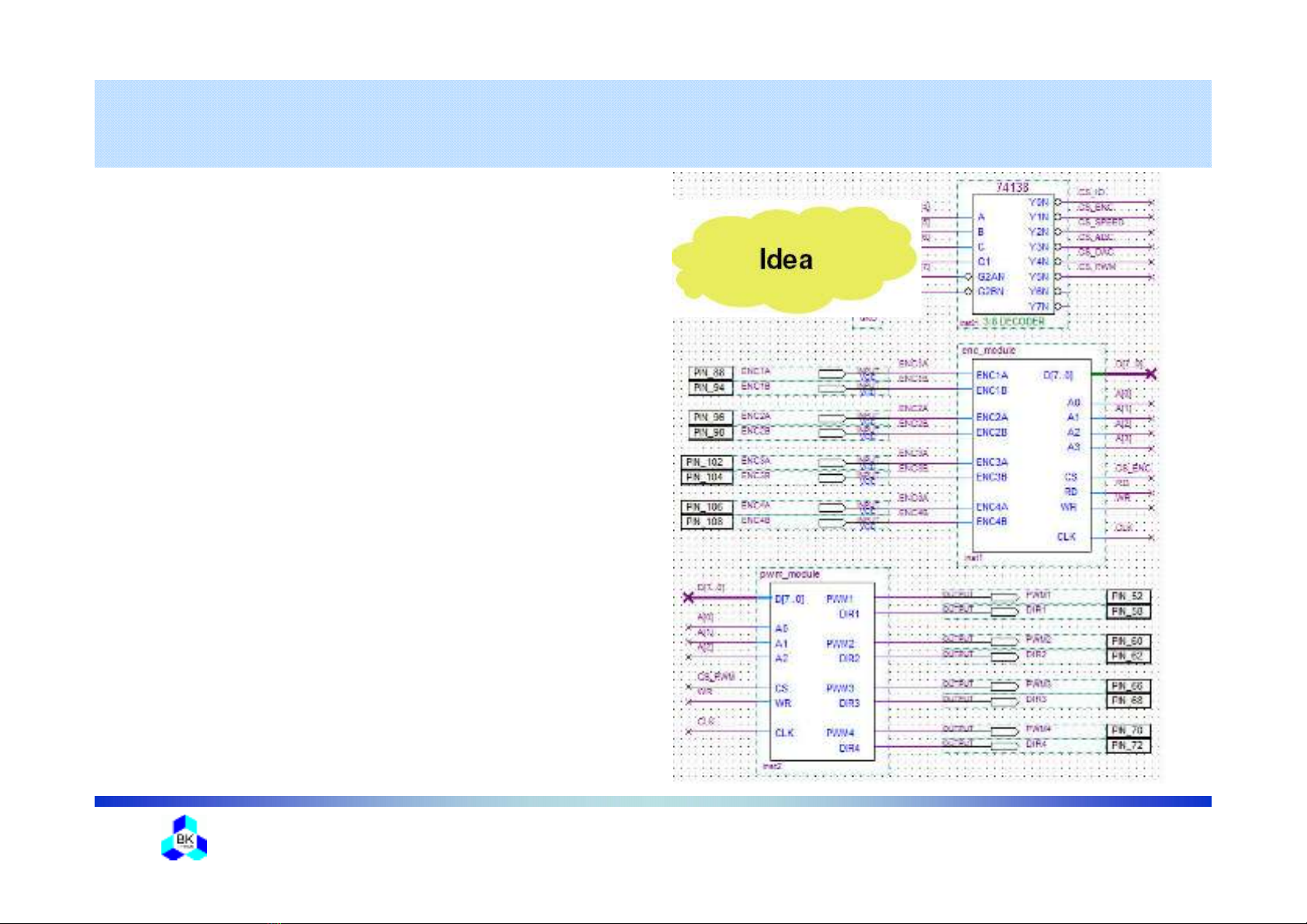

-Thiếtkếmạch số(1950’s, 1980’s):

vẽmạch schematic -> lựachọn linh

kiện -> thi công.

-Mạch schematic gồmcó:

•Phầntử(component): Cổng

(Gate), Điệntrở, (LEDs, LCD)

Chips,…

•Dâykếtnốicácphầntử

• Input, Output -> xem 1 mạch

schematic như1 phầntử-> kết

nối phân cấp.

1950’s 1980’s

3

I. GIỚI THIỆU

Trường ĐH Bách Khoa TP.HCM

1.1. Ngôn ngữmô tảphầncứng HDL

(Hardware Description Language)

-Thiếtkếmạch số(1995’s ->): vẽ

mạch schematic ->... hoàn tất

- Hai ngôn ngữphổbiến: Verilog

HDL (1984) và VHDL (1980).

-Đượcsửdụng rộng rãi trong thiếtkế

và mô phỏng mạch sốởmứcđộ

thanh ghi (register-transfer level).

-MộtthiếtkếHDL bao gồm nhiều

module, mỗi module chứanhiều

phân cấpvàgiaotiếpvới các module

khác thông qua tập input, output, và

bidirectional port.

1995’s

4

I. GIỚI THIỆU

Trường ĐH Bách Khoa TP.HCM

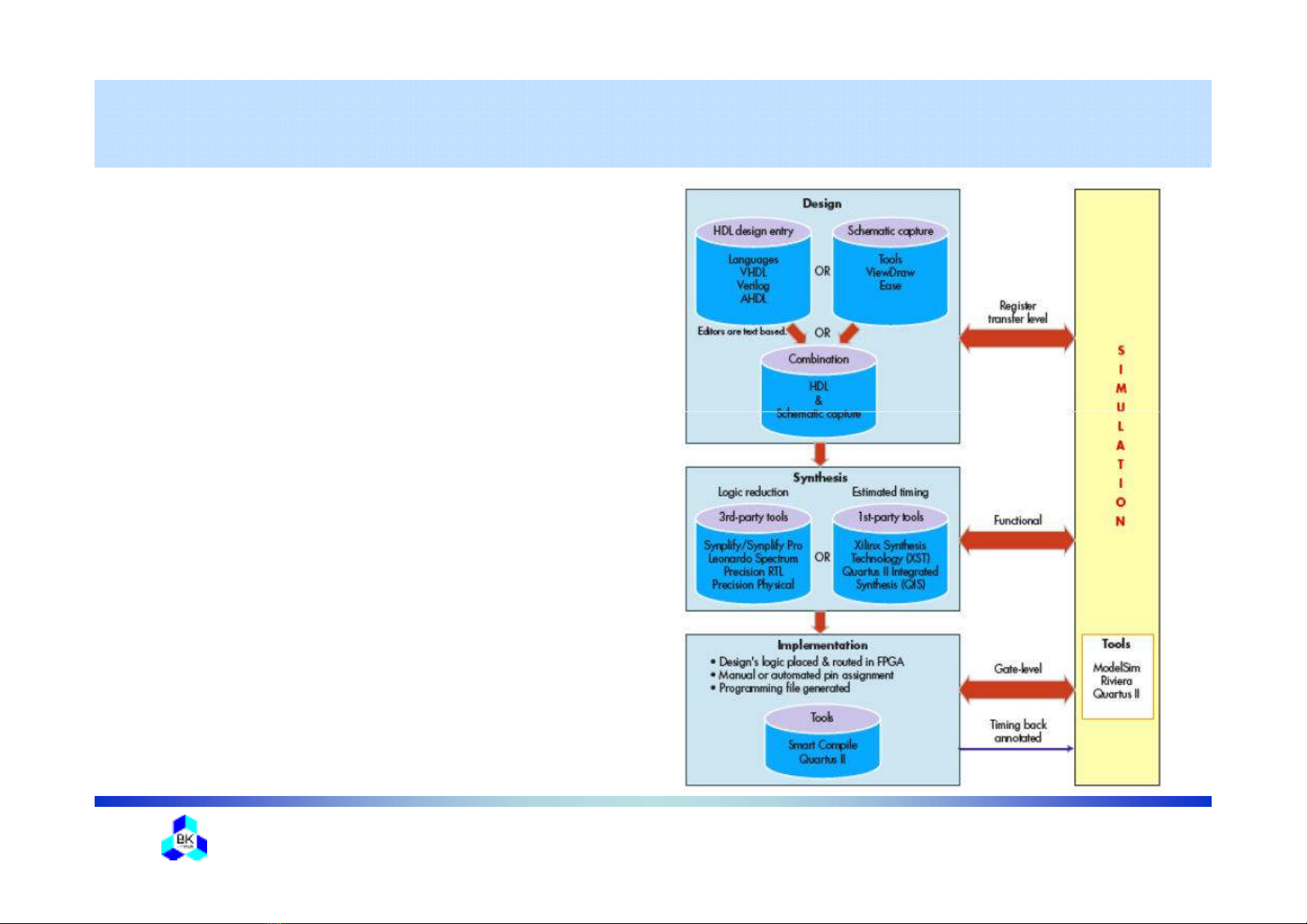

1.2. ƯuđiểmHDL so với Schematic:

-Xâydựng và lưutrữHDL trong các

file.

- Các file có thểđóng gói và xửlý

bởi các công cụ:

•Design: ViếtHDL, vẽsơđồ

• Synthesis: lựachọnphầntử, tối

ưulogic, ướclượng thờigian

• Implementation: gán chân, lập

trình vào FPGA

-Dễdàng thay đổi, chỉnh sửathiếtkế

mà không cầnthayđổiphầncứng.

-Đáp ứng các yêu cầuthiếtkếphức

tạp

5

II. THIẾT KẾ PHÂN CẤP

Trường ĐH Bách Khoa TP.HCM

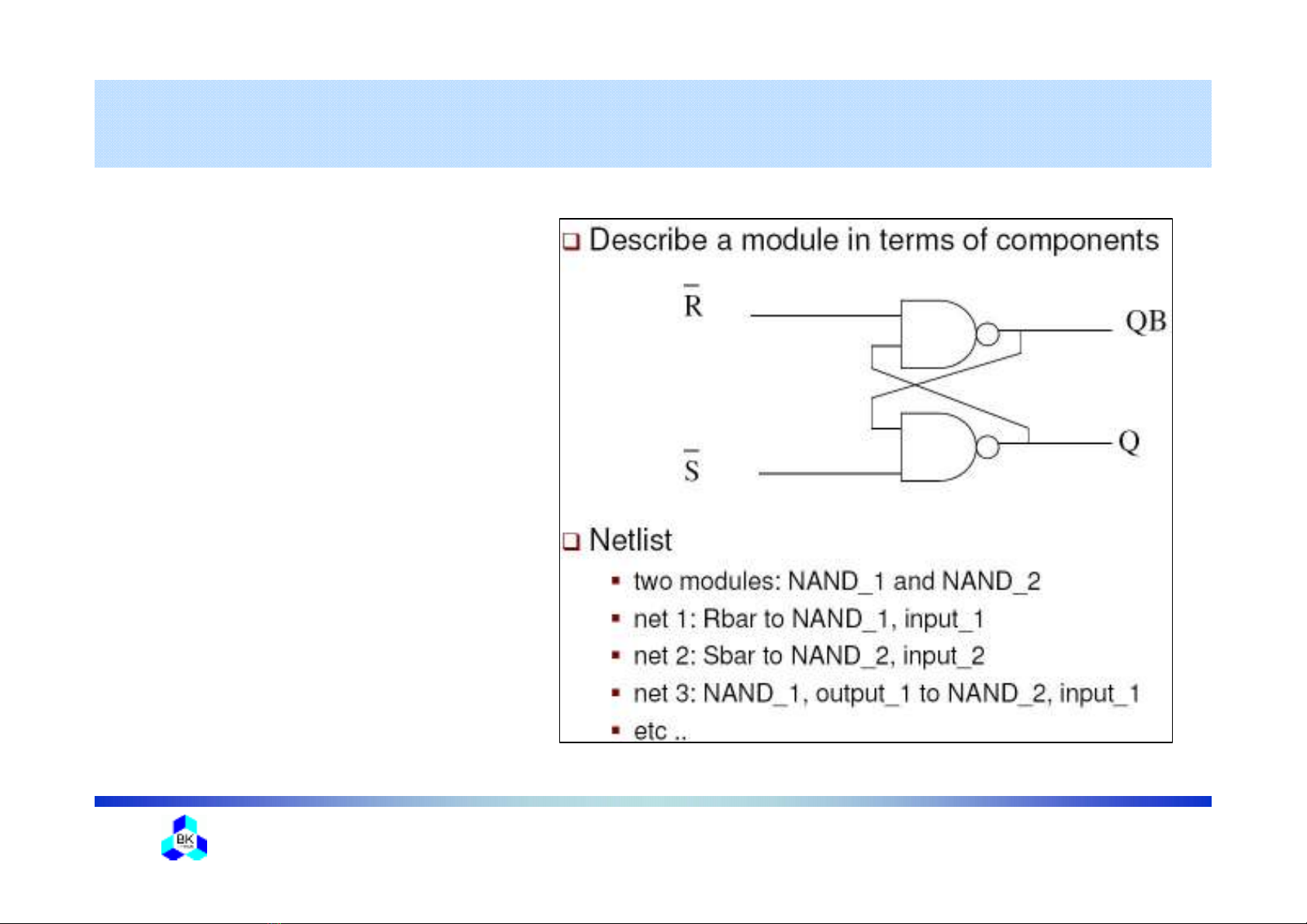

2.1. Các mô tả(abstraction)

trong thiếtkếphầncứng:

-Môtảcấu trúc (Structural

modeling).

-Môtảdòng dữliệu

(Dataflow modeling).

-Môtảhành vi (Behavioral

modeling).

![Tài liệu học tập Thiết kế hệ thống nhúng [mới nhất, đầy đủ]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/37051773135929.jpg)