Chương 7

Bộ định thì (Timer)

Nguyễn Lý Thiên Trường 1

Tài liệu tham khảo:

1. Chương 7: Bộ định thì (Timers) (Giáo trình VXL)

2. Muhammad Ali Mazidi, AVR Microcontroller and Embedded Systems: Using Assembly and C,

Pearson New International Edition, 2014.

3. Datasheet ATmega324P

4. https://nicerland.com/avr/

5. http://www.hocavr.com/

6. https://www.youtube.com/watch?v=Fr2K9pzec8g&list=PLgwJf8NK-

2e55CdbY_WnY6pejPHoojCkJ

Nguyễn Lý Thiên Trường 2

7.1 Giới thiệu

7.2 Lập trình Timer0

7.2.1 Normal mode

7.2.2 CTC mode

7.3 Lập trình Timer2 chế độ NOR và CTC

7.4 Timer1

7.4.1 Normal mode

7.4.2 CTC mode

7.4.3 Chức năng bắt ngõ vào (Input Capture)

7.5 Lập trình Timer chức năng đếm sự kiện

7.6 Lập trình tạo sóng với Timer0 và Timer2

7.7 Lập trình tạo sóng với Timer1

7.1 Giới thiệu

3

Nguyễn Lý Thiên Trường

Counter register

External

source

Oscillator

Counter/Timer

COUT

0

1

Flag

▪Bộ định thì được ứng dụng tạo thời gian trễ (delay time), tạo hàm, dạng

sóng, đếm các sự kiện, biến cố…

▪ATmega324P có 3 bộ định thì ký hiệu là: Timer0, Timer1, Timer2.

oTimer0, Timer2 là 8 bit.

oTimer1 là 16 bit.

▪Xung CK kích mạch đếm có thể chọn từ mạch dao động chuẩn (Oscillator) khi dùng với

chức năng Timer hoặc từ xung đếm ngoài (External source) khi dùng với chức năng

Counter.

CK

Flag: Cờ báo

4

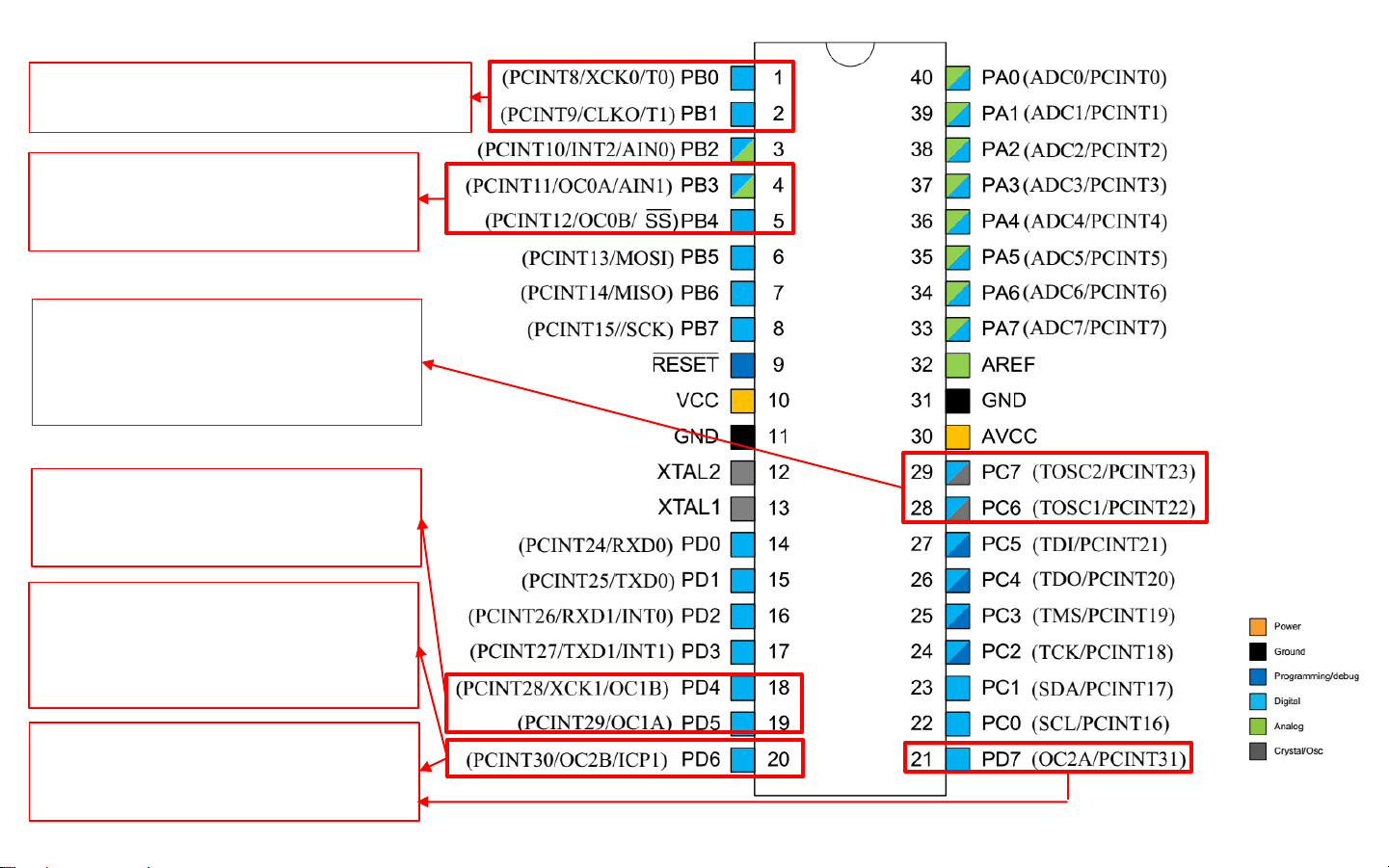

Ngõ vào xung CK ngoài, chức năng đếm sự

kiện (Counter) ở Counter0 và Counter1

Tạo chuyển biến logic hoặc chuỗi xung

ngõ ra OC0A, OC0B trong các chế độ

Timer0 có khai báo tạo sóng ngõ ra.

Tạo chuyển biến logic hoặc chuỗi xung

ngõ ra OC1A, OC1B trong các chế độ

Timer1 có khai báo tạo sóng ngõ ra.

Tạo chuyển biến logic hoặc chuỗi xung

ngõ ra OC2A, OC2B trong các chế độ

Timer2 có khai báo tạo sóng ngõ ra.

Timer2 thay thế chức năng đếm xung

ngoài bằng chức năng đếm thời gian

thực, bằng cách gắn một bộ thạch anh

FXTAL ở 2 ngõ TOSC1 và TOSC2.

Timer1 có ngõ vào Input Capture

dùng để phát hiện sự thay đổi mức

logic (sự kiện), đo thông số sự kiện

xảy ra trên chân ICP1.

ATmega324P

Nguyễn Lý Thiên Trường

7.1 Giới thiệu

5

Nguyễn Lý Thiên Trường

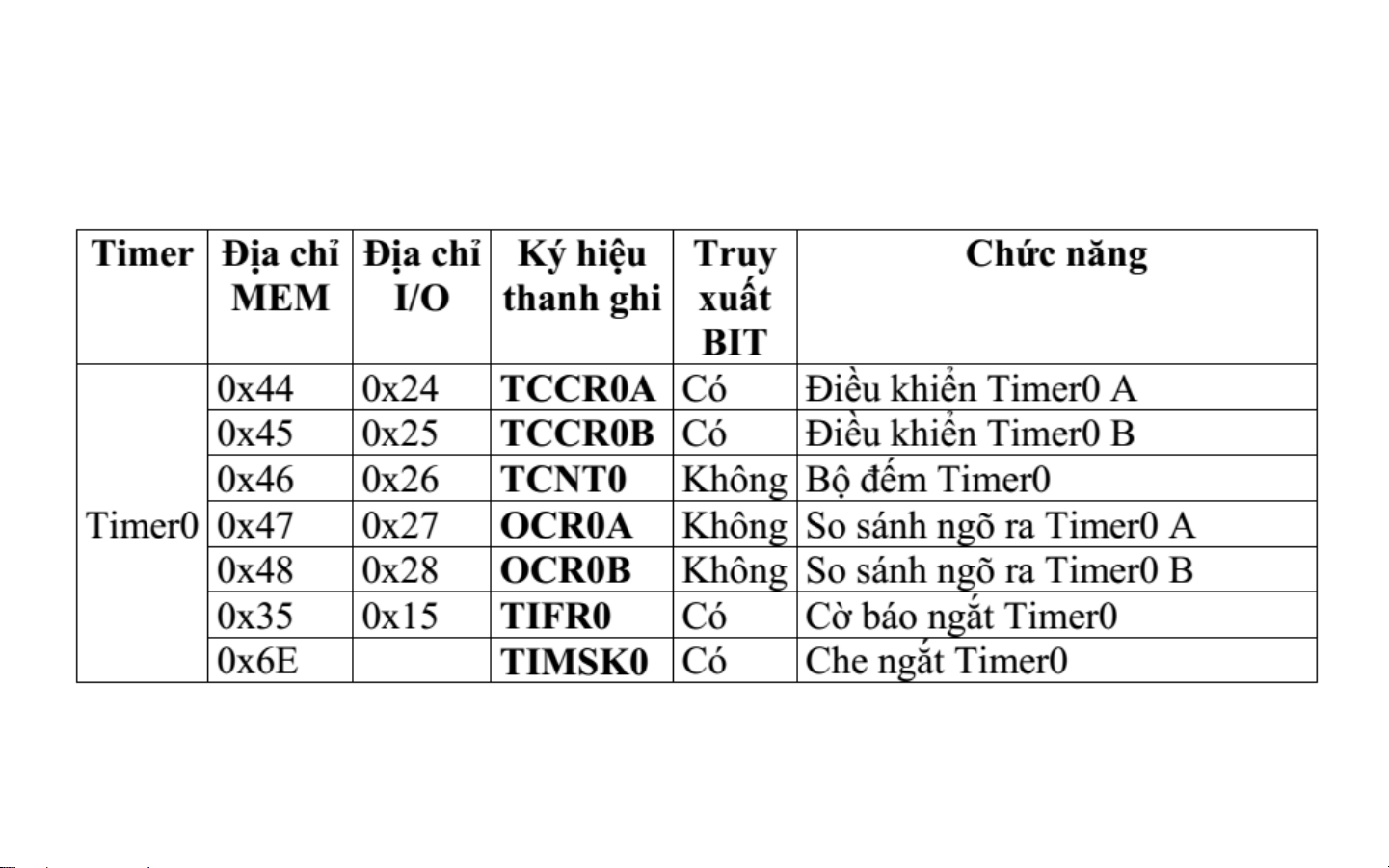

▪Hoạt động của các Timer trong MCU324P được quản lý và điều

khiển bởi các thanh ghi như sau:

![Bài giảng Kiến trúc máy tính: Chương 1 - Giới thiệu tổng quan [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250729/kimphuong1001/135x160/47331753774510.jpg)