1

Họ và tên: Lê Anh Tiến

SHSV: 20092698

Lớp Tin học công nghiệp - kĩ sư chất lượng cao K54

Số điện thoại: 01696572668

ĐIỆN TỬ SỐ

BÀI TẬP

- Bài tập trong cuốn : Điện Tử số

- Của tác giả Lương Ngọc Hải-Lê Hải Sâm- Nguyễn Trịnh Đường-

Trần Văn Tuấn

PHẦN I: BÀI TẬP TRONG SÁCH

Chương 1- KIẾN THỨC CỞ CỦA KĨ THUẬT SỐ

1.1

- Trong điều khiển kĩ thuật, điều khiển kinh tế... ta thường gặp những

bài toán mà thông tin cho trước (dữ liệu vào) và các đáp ứng của bài toán,

đều chỉ có thể ở một trong hai trạng thái đối kháng nhau: đúng/sai,

nóng/lạnh... Các bài toán điều khiển như vậy gọi là bài toán logic.

- Đại số Boole là công cụ để giải những bài toán logic. Các biến trong

đại số Boole gọi là biến logic. Nó chỉ có 2 giá trị, kí hiệu là 1/0, đặc trưng

cho hai trạng thái đối kháng của một hiện tượng. Hai giá trị của biến logic

hoàn toàn không có ý nghĩa về lượng.

- Trong các mạch logic điện, điện áp mang thông tin về hai giá trị của

biến logic, và nó chỉ có thể nằm ở hai miền giá trị hoàn toàn phân biệt

nhau, gọi là hai mức logic, gồm mức cao H và mức thấp L.

1.2

- Mạch logic gồm những linh kiện, chủ yếu là các khóa đóng/mở, ghép

nối với nhau; nhằm thực hiện những quan hệ logic cho trước. Tuyệt đại

đa số các mạch logic hiện nay là mạch logic điện. Nếu các khóa đóng/mở

trong mạch logic điện là tiếp điểm của các rơ le điện từ, thì mạch gọi là

mạch logic tiếp điểm (hay mạch logic rơ le). Nếu dùng trangzito hay điot

làm khóa đóng mở thì gọi là mạch logic điện tử.

- Nếu một mạch logic, mức thấp L đặc trưng cho giá trị 0 logic, mức

cao H đặc trưng cho mức 1 logic thì mạch gọi là mạch logic dương.

Ngược lại, mức cao H đặc trưng cho giá trị 0 logic, mức thấp L đặc trưng

cho mức 1 logic thì mạch gọi là mạch logic âm.

2

1.3

A

B

C

A

B

AB

AB

A B

+

A B

+

................

A

B

C

A

B

AA

B B

+

A.1

B+1

3

A

B

C

A

B

ABC

A+B+C

ABC

A B C

+ +

A B

Å

A B

Å

A B

Å

A B C

Å Å

1.4

a- Bữa trưa ở nhà máy:

Đầu vào:

-Mua/Không mua bánh mì kẹp.

-Lấy /Không láy canh.

-Lấy /Không lấy rau trộn.

Đầu ra:

-Đưa/Không đưa bánh mì kẹp.

-Đưa/Không đưa canh.

-Đưa/Không đưa rau trộn.

b- Đăng kí giáo trình:

Đầu vào:

4

-Đăng kí/ Không đăng kí học luật.

-Đăng kí/ Không đăng kí học sử.

-Đăng kí/ Không đăng kí học Anh.

-Đăng kí/ Không đăng kí học Pháp.

Đầu ra:

-Xác nhận học/ không học sử.

-Xác nhận học/ không học luật.

-Xác nhận học/ không học Anh.

-Xác nhận học/ không học Pháp.

c-

Người công nhân sơn tường:

Đầu vào:

-Chọn sơn/không sơn tường màu vàng.

-Chọn sơn/không sơn tường màu xanh.

Đầu ra:

-Nhà được/không được sơn màu vàng.

-Nhà được/không được sơn màu xanh.

1.5

a-

A AD A(D 1) A

+ = + =

b-

A AD A D

+ = +

c-

XYZ XY X(YZ Y) X(Y Z)

+ = + = +

d-

A B AB A B A B 1

+ + = + + + =

e-

B BE B E

+ = +

f-

ABC ABC B AB B A B

+ + = + = +

g-

ABC AC C C(AB A) C CA C A C

+ + = + + = + = +

1.6

a-

ABC ABC C BC C B C

+ + = + = +

b-

ABC ABC ABC ABC BC C(AB B) C(A B) CAB

+ + = + = + = + =

c-

ABC ABC ABC ABC (ABC ABC) (ABC ABC) (ABC ABC)

AB BC CA

+ + + = + + + + +

= + +

d-

AB BC AC ABC ABC BC AB AB BC

+ + = + + + = +

1.7

a-

(A B)(A B) AB B BA B

+ + = + + =

b-

(A B C)(A B C)(A B C) (A B)(A B C)

A BA AB AC BC A AC BC A BC

+ + + + + + = + + +

= + + + + = + + = +

5

c-(A B)(B C)(C A) (AB AC BC)(C A)

CBA AC BC AB AC ABC AC BC AB

+ + + = + + +

= + + + + + = + +

1.8

a-

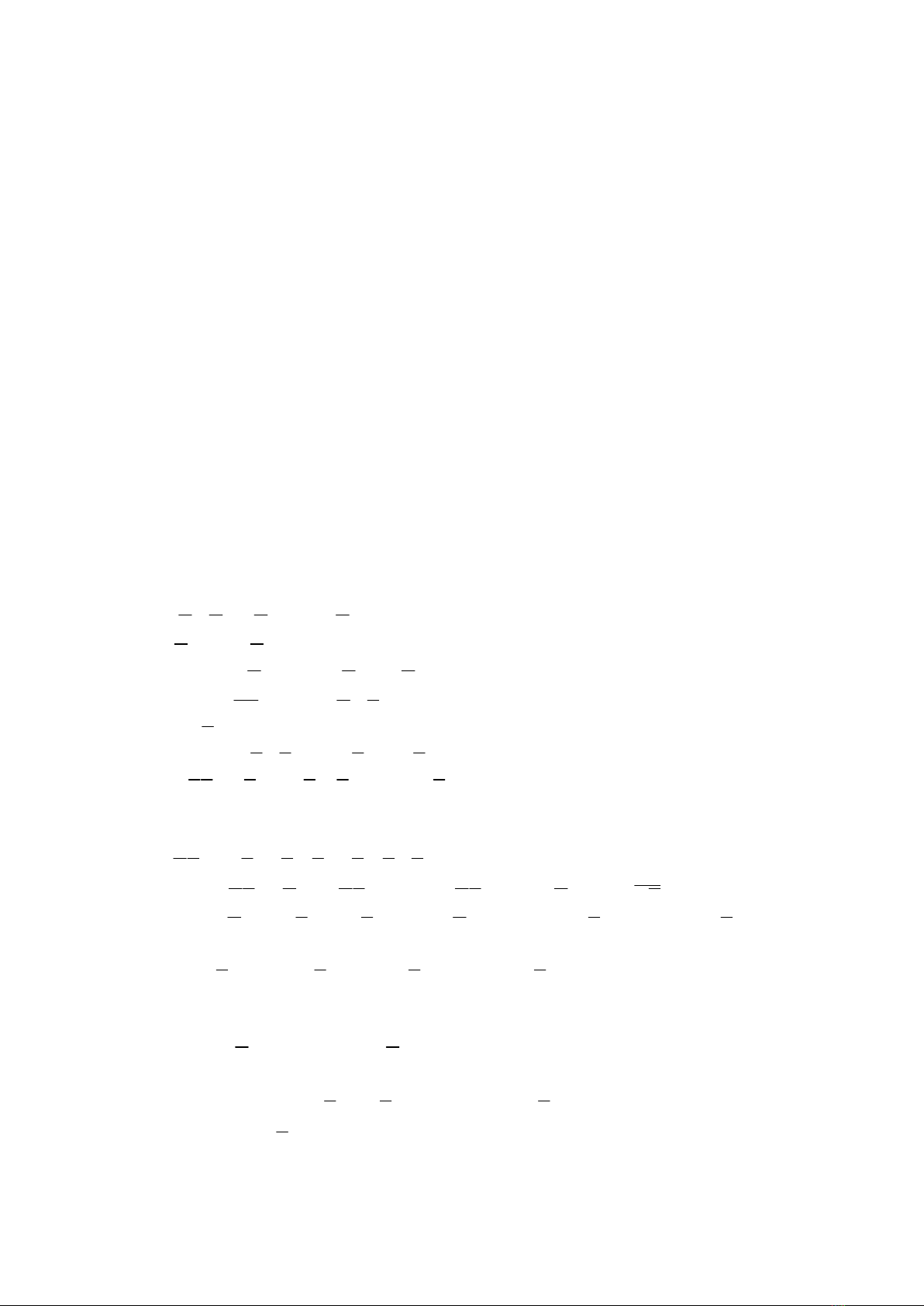

U1

AND_2

U2

AND_2

U3

NOT U4

OR

Q

C

A

B

Q(A,B,C) CA BC

= +

A B C

CA

BC Q

0 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 0 0

0 1 1 0 1 1

1 0 0 1 0 1

1 0 1 0 0 0

1 1 0 1 0 1

1 1 1 0 1 1

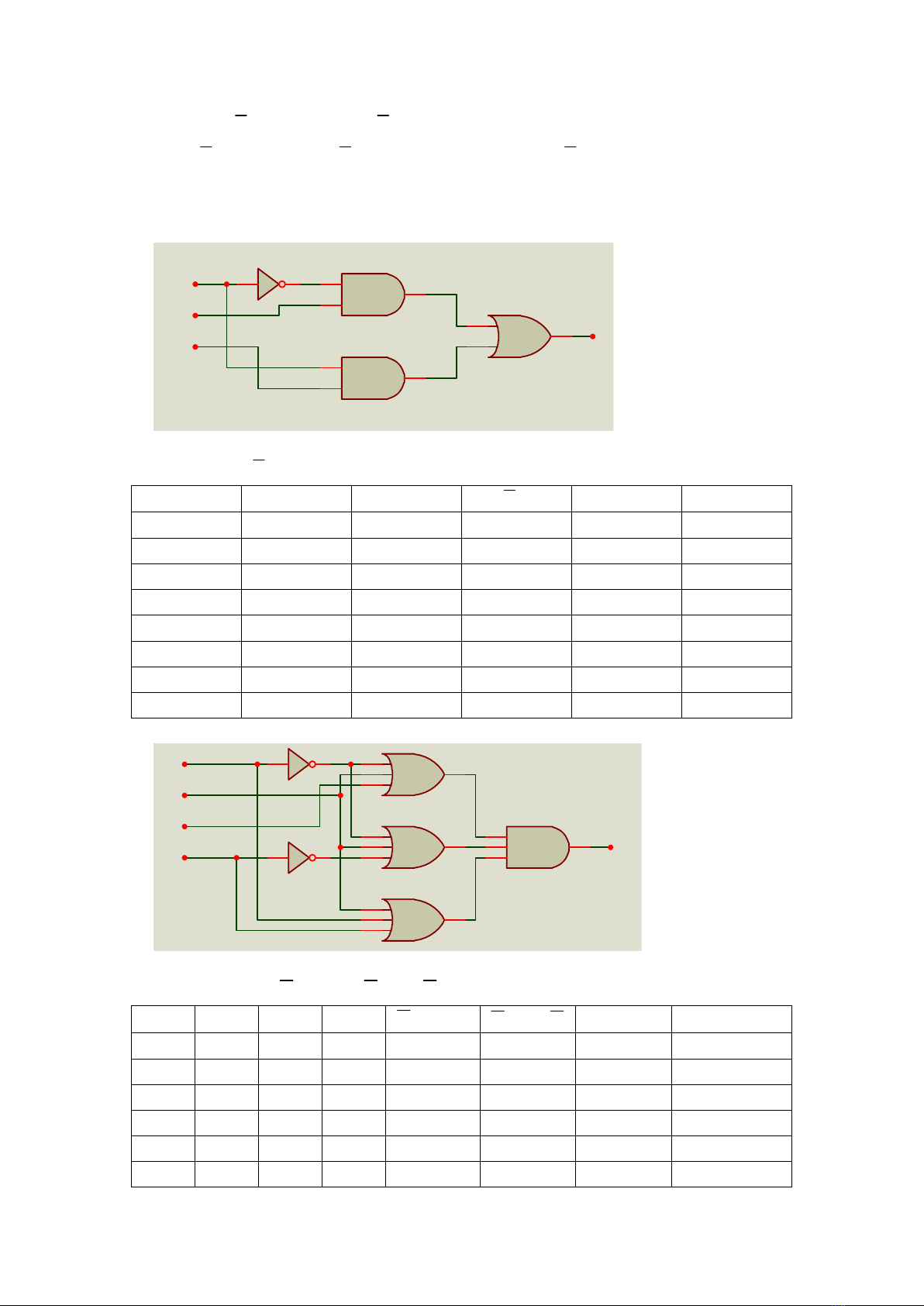

b-

U1

OR_3

U2

OR_3

U3

OR_3

U4

AND_3

U5

NOT

U6

NOT

A

B

C

DQ

Q(A,B,C,D) (A B C)(A B D)(B A D)

= + + + + + +

A B C D

A B C

+ +

A B D

+ +

B A D

+ +

Q(A,B,C,D)

0 0 0 0 1 1 0 0

0 0 0 1 1 1 1 1

0 0 1 0 1 1 0 0

0 0 1 1 1 1 1 1

0 1 0 0 1 1 1 1

0 1 0 1 1 1 1 1

![Công thức đặt câu lệnh với AI: Tài liệu [mô tả/định tính, ví dụ: chuẩn nhất, mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251231/gaupanda090/135x160/1311777371375.jpg)