Ộ Ộ Ủ Ệ

ộ ậ ự ạ C NG HOÀ XÃ H I CH NGHĨA VI T NAM Đ c l pT doH nh phúc

Ố Ệ Ề Ề

Ệ ĐÁP ÁN Ẳ Đ THI T T NGHI P CAO Đ NG NGH KHÓA 3 (20092012) Ệ Ử NGH :Ề ĐI N T CÔNG NGHI P

Ề

ề Ế MÔN THI: LÝ THUY T CHUYÊN MÔN NGH Mã đ thi: ĐA ĐTCN LT45

Đáp án Đi mể

ố Câu 1

ừ ồ ặ ề ế ạ ạ ươ ứ ầ ủ 15 lùi v đ n 0 r i l p 0,5 ầ ớ ộ ế ng ng v i b đ m đ y đ 4 bit t

B

C

D

1

1

1

1

T

Q

T

Q

T

Q

T

Q

C K

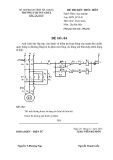

Phân tích lo i m ch và s FF c n dùng. Modul 16 t i.ạ l ơ ồ ạ S đ m ch đ m ế A

C L K

Q

C L K

Q

C L K

Q

C L K

Q

0,5

ố ế S đ m là DCBA

CK

A

B

C

D

0,5 ủ ế ạ ả ồ Gi n đ xung c a m ch đ m

0,5

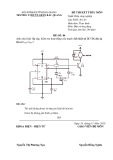

0,5 2 ấ ạ C u t o

ộ ấ ể ề ể ệ ạ ẫ Thysistor là linh ki n chuy n m ch có đi u khi n là m t c u trúc bán d n

ế ạ ớ ớ Silíc có 4 l p, t o thành 3 l p ti p giáp PN.

1 n i ra ngoài t o thành c c A n t;

ừ ớ ẫ ự ạ ố ố T l p bán d n P

ừ ớ ẫ ự ố ố T l p bán d n N t; ạ 2 n i ra ngoài t o thành c c Kat

2 n i ra ngoài t o thành c c đi u khi n G.

ừ ớ ẫ ự ề ể ạ ố T l p bán d n P

A

A

P1

Xung đ.khi nể

N1

P2

G

N2

K

K

ấ C u trúc Thysistor

ấ ạ ề ấ ạ ủ C u t o và hình dáng bên ngoài c a Thysistor có r t nhi u lo i khác

ệ ừ ớ ể ị ế nhau v i dòng đi n t ự miliampe đ n hàng ngàn ampe và có th ch u đ ng

ượ ớ ậ ướ ủ đ ệ c đi n áp t i hàng ngàn vôn. Do v y kích th c c a chúng cũng nh ư

n (n ng đồ

ộ)

Kích th

cướ

P1

N1

P2

N2

ạ ấ ự s pha t o trong 4 vùng silíc cũng r t khác nhau.

ề ủ ố ố ộ ạ ự ấ S phân b n ng đ t p ch t trong các mi n c a Thysistor

ủ ạ ộ Nguyên lý ho t đ ng c a Thysistor

ả ơ ồ ắ ớ Gi i thích theo s đ m c 02 transistor v i nhau

ể ưở ể ượ ệ ủ Đ xét nguyên lý làm vi c c a Thysistor ta có th t ng t ng chia

1N1P2 và N1P2N2

0,5 ầ ươ ệ ự ư linh ki n này ra làm hai ph n t ng t nh hai transistor P

ư ớ ẽ ghép v i nhau nh hình v :

A

Ia

Ia

P1

Ra

α1.Ia

Ra

GE2

T2, α2

N1

N1

Ea

α2.Ia

GC

T1, α1

P2

P2

GE1

N2

K

ả ủ ơ ồ ễ S đ di n gi i c a Thysistor

C

ế ể ự ể ế Khi đó chuy n ti p G ậ E1 và GE2 phân c c thu n còn chuy n ti p G

E1 s có h s truy n đ t α

ượ ệ ố ẽ ề ế ự phân c c ng ế c. Qua ti p giáp G ạ 1 qua ti p giáp

2 nh v y dòng đi n ch y qua các transistor

ề ẽ ạ ư ậ ệ ạ GE2 s có h s truy n đ t α ệ ố

s là:ẽ

IC1 = α1Ia + ICO1; IC2 = α2Ia + ICO2

ư ậ ạ ệ Nh v y dòng đi n m ch ngoài:

I

CO

Ia = α1Ia + α2Ia + ICO;

I

a

(cid:0)

(cid:0) (1

)

1

2

(cid:0) (cid:0) (cid:0)

ị ấ ỏ ượ ạ c ch y qua Trong đó ICO = ICO1+ ICO2 có giá tr r t nh là dòng ng

transistor T1 và T2.

2 và IG > 0.

(cid:0)

ả ử ự ể ượ ố Gi ề s c c đi u khi n G đ c n i vào P

I

a

I CO (cid:0)

I G 1 (cid:0) (1

)

1

2

(cid:0) (cid:0) (cid:0) (cid:0)

ặ ế ậ Khi có dòng đi n Iệ G m t ti p giáp G ậ ự E1 càng phân c c thu n do v y

1 cũng tăng m nh s góp ph n làm cho tăng (α

1 +α2)

ề ạ ẽ ạ ầ h s truy n đ t α ệ ố

ế ớ ố ẽ ộ nhanh chóng ti n t i m t dòng an t s nhanh chóng tăng.

ả ụ ệ Gi i thích theo nguyên lý tích t đi n tích:

AK < Ung.thu nậ : Khi đó vùng ti p giáp J

1, J3

ệ ấ ế C p cho thyristor đi n áp 0 < U

2 b phân c c ng

1 và J3 đ

ượ ậ ự ị ượ ượ đ ự c phân c c thu n, J c. Do J ự c phân c c

1 và các đi n t

ậ ỗ ố ể thu n nên các l tr ng t P N ừ 1 di chuy n sang N ệ ử ừ 2 di t

2. Các đi n tích đó khi di chuy n theo quán tính s r i vào

ể ẽ ơ ệ ể chuy n sang P

ệ ấ ế vùng ti p giáp J ế 2. Do N1 và P2 là hai vùng nghèo đi n tích nh t nên ti p

ự ượ ệ ấ ớ ệ ộ c thì đ cách đi n r t l n, các đi n tích khi ị giáp J2 khi b phân c c ng

ệ ủ ể ộ ờ r i vào vùng J ặ ả 2 thì đ cách đi n c a nó gi m không đáng k . Do đó m c

AK <

ượ ư ủ ớ ư ự ệ ậ dù Thyristor đ ế c phân c c thu n nh ng n u đi n áp ch a đ l n U

ở ượ ư ẫ c. Ung,thu nậ thì thyristor v n ch a m đ

AK thì các đi n tích r i vào vùng J

2 s tăng

ế ụ ế ệ ệ ơ ẽ N u ti p t c tăng đi n áp U

ệ ả ộ ộ ầ d n. Khi U ộ ộ AK = Ung,thu nậ thì đ cách đi n c a J ố ủ 2 gi m xu ng đ t ng t, đ

ướ ủ ụ ệ ệ ệ ẫ d n đi n tăng. D i tác d ng c a đi n áp ngoài các đi n tích trong

ể ẽ ạ thyristor s di chuy n và t o thành dòng đi n I ệ AK.

2 đi nệ

ự ế ệ ế ấ ứ N u cho dòng đi n vào c c G, t c là cung c p cho vùng ti p giáp J

ẽ ả ở ơ ớ tích thì quá trình m thyristor s x y ra s m h n.

IA

IA

SCR d nẫ

IG4>IG3>IG2>IG1=0

IH

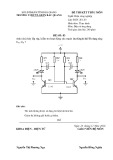

ế ặ Đ c tuy n VA

VBR

VBR

VAK

VAK

VAKO

VBO

VBO

SCR ng tắ

0,5

ế ặ Hình 1.32. Đ c tuy n V A Thysistor

ườ ủ ặ ượ Đ ng đ c tính VA c a m t ộ Thysistor đ ầ c chia ra làm hai ph n:

ấ ằ ầ ư ứ ậ ứ ứ ầ ặ ấ Ph n th nh t n m trong góc ph n t ớ th nh t là đ c tính thu n ng v i

AK > 0; ph n th hai n m trong góc ph n t

ệ ầ ư ứ ứ ầ ặ ằ đi n áp U th III, là đ c tính

AK < 0.

ượ ứ ệ ớ ng c ng v i đi n áp U

G = 0):

ườ ể ề ệ ằ ợ Tr ự ng h p dòng đi n vào c c đi u khi n b ng 0 (I

1; J3 b phân c c ng

ế ự ị ượ ệ + Khi đi n áp U ớ c, l p ớ AK < 0, hai l p ti p giáp J

2 đ

ế ượ ẽ ố ư ự ậ ti p giáp J c phân c c thu n, nh v y ư ậ Thysistor s gi ng nh hai

ố ố ế ự ắ ị ượ ẽ đi t m c n i ti p b phân c c ng c. Qua ệ ấ Thysistor s co dòng đi n r t

ệ ạ ỏ ọ ạ ế ị ớ ộ nh ch y qua, g i là dòng đi n rò. Khi U ấ AK đ t đ n m t giá tr l n nh t

ẽ ả ệ ượ ủ ệ ị ng Thysistor b đánh Ung.max (UBR: đi n áp đánh th ng) s x y ra hi n t

ị ỏ ủ ệ ể th ng, dòng đi n có th tăng lên r t l n. ấ ớ Thysistor đã b h ng.

2

ế ớ ự ế ớ + Khi UAK > 0, hai l p ti p giáp J ậ 1; J3 phân c c thu n, l p ti p giáp J

ượ ự ượ ệ ấ ầ ỏ ỉ đ c phân c c ng ạ ộ c, lúc đ u cũng ch có m t dòng đi n r t nh ch y

AK tăng đ n giá tr đi n áp thu n l n nh t U

th.max

ọ ậ ớ ị ệ ế ấ qua g i là dòng dò. Khi U

ẽ ả ệ ượ ở ươ ươ ủ ạ ả ệ ng đi n tr t ng đ ộ ng c a m ch AK gi m đ t (UBO) s x y ra hi n t

ộ ị ớ ạ ế ạ ở ỉ ng t, dòng qua qua ẽ Thysistor s ch b gi i h n b i m ch ngoài. n u khi

ứ ơ ộ ố ể ọ ớ đó dòng qua Thysistor l n h n m t m c dòng t i thi u, g i là dòng duy trì

ẽ ẫ ườ ặ ậ ng đ c tính tu n. Ih, thì khi đó Thysistor s d n dòng trên đ

ệ ể

ườ ự ế ườ ự ể

ợ ề ậ ẽ ả ặ ng đ c tính ị ớ ề ể ệ ể ớ ậ ơ ệ G > 0): N u có dòng đi n ệ c khi đi n áp thu n đ t đ n giá tr l n

Tr ng h p có dòng đi n vào c c đi u khi n (I vào c c đi u khi n quá trình chuy n đi m làm vi c trên đ ạ ế ướ thu n s x y ra s m h n, tr nh t.ấ ở Các cách m Thyristor

ệ ở ở Theo nguyên lý làm vi c trên có 02 cách m Thyristor.

AK = Ung.thu nậ : Thyristor t

Đ t Uặ ự ở m ;

UAK > 0 và IG > 0.

ể ở ườ ườ Đ m Thyristor th ng ng ở ứ i ta dùng cách m th 2. Vì cách m th ở ứ 0,5

ể ấ ườ ế ị ế ệ ớ nh t nguy hi m cho ng i và thi ặ t b . N u đi n áp đ t vào quá l n thì khi

ự ắ ở ẽ ạ Thyristor m s gây ra s ng n m ch.

ộ ở ể ữ ề

ắ i ta th

ể ờ 3 0,5

ể ở ề ọ ể ử ụ ả ử ụ ộ ị ờ

0,5

ứ ụ ẽ Khi thyristor đã m thì s không ph thu c và xung đi u khi n n a. Do ườ ườ ậ v y đ m Thyristor, ng ng dùng các xung ng n. ộ ị H vi đi u khi n 8051 có hai b đ nh th i là Timer0 và Timer1 Đ s d ng các b đ nh th i này ta ph i s d ng các thanh ghi là: Timer0 (TH0 và TL0), Timer1 (TH1 và TL1), TMOD ủ Ch c năng c a các thanh ghi:

ị ủ ộ ị ư ữ ở + TH0 và TL0 l u tr giá tr c a b đ nh th i timer0 0,5 0,5

ị ủ ộ ị ư ữ ở + TH1 và TL1 l u tr giá tr c a b đ nh th i timer1

0,5 ế ậ ế ộ ủ ệ + Thanh ghi TMOD: thi t l p các ch đ làm vi c khác nhau c a

ấ ượ ờ ồ ộ ị b đ nh th i. Thanh ghi TMOD là thanh ghi 8 bít g m có 4 bít th p đ c

ế ậ ộ thi t l p dành cho b Timer 0 và 4 bít cao dành cho Timer 1. Trong đó hai

ấ ủ ể ế ậ ế ộ ủ ộ ị ờ bít th p c a chúng dùng đ thi t l p ch đ c a b đ nh th i, còn 2 bít

(MSB)

(MSB)

ể ị cao dùng đ xác đ nh phép toán

GATE C/T M1 M0

GATE C/T M1 M0

Timer1

Timer0

0,5

ộ C ng (I) 7

ầ ự ọ II. Ph n t ch n

3

4

ộ

ổ C ng (II) ộ T ng c ng (I+II)

…….., ngày …..tháng …..năm …….

ề

ể

ộ ồ

Duy tệ

Ti u ban ra đ thi

ố t

H i đ ng thi t nghi pệ