Ộ Ộ Ủ Ệ

ộ ậ ự ạ C NG HOÀ XÃ H I CH NGHĨA VI T NAM Đ c l pT doH nh phúc

Ố Ệ Ề Ề

Ệ ĐÁP ÁN Ẳ Đ THI T T NGHI P CAO Đ NG NGH KHÓA 3 (20092012) Ệ Ử NGH :Ề ĐI N T CÔNG NGHI P

Ề

ề Ế MÔN THI: LÝ THUY T CHUYÊN MÔN NGH Mã đ thi: ĐA ĐTCN LT47

Đáp án

Câu 1

Đi mể 1

TỬ 0 0 1 1 1 0 1 0

ĐI NỆ 0 1 1 1 1 0 1 0

NGHI PỆ 0 0 0 0 1 0 1 0

ọ

CÔNG 0 0 0 1 1 0 1 0 ỗ ầ

ế ề ể

A 0 1 0 1 0 0 1 0 ể ử ụ ữ ệ

ầ ộ ớ

ị ị

ạ ả B ng tr ng thái B C D TT 0 0 0 0 0 0 0 1 1 0 0 2 1 0 0 3 0 1 0 4 1 1 0 5 1 1 0 6 0 0 1 7 ề Ch n A,B,C là các bi n đi u khi n s d ng Mux 8:1, M i đ u ra đi u khi n ư ả là m t Mux 8:1 v i các đ u vào d li u nh b ng sau ữ ệ ể ầ Xác đ nh giá tr các đ u vào d li u: ( 1 đi m) ĐI NỆ TỬ CÔNG NGHI PỆ D0 =A D0 =0 D0 =0 D1 =1 D1 =1 D1 =A D2 = A D2 = A D2 = A D3 = A D3 = A D3 = A D4 =0 D4 =0 D4 =0 D5 =0 D5 =0 D5 =0 D6 =0 D6 =0 D6 =0 D7 =0 D7 =0 D7 =0 D0 =0 D1 =0 D2 = A D3 = A D4 =0 D5 =0 D6 =0 D7 =0

SW-HL2

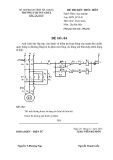

ơ ồ ạ ể * S đ m ch: ( 1 đi m)

L1

L3

L2

L4

H L

SW-HL1

U2 74151

U1 74151

U3 74151

U4 74151

5

7

7

5

5

5

7

7

H L

6

4

4

6

6

6

4

4

Y W

Y W

Y W

Y W

3

3

3

3

2

2

2

2

1

1

1

1

15

15

15

15

U5 SN7490

14

14

14

14

13

13

13

13

U8 1M

12

12

12

12

1

11

11

11

11

QA QB QC QD

2

10

10

10

10

9

9

9

9

R9(1) R9(2) CKA CKB R0(1) R0(2)

G D0 D1 D2 D3 D4 D5 D6 D7 A B C

G D0 D1 D2 D3 D4 D5 D6 D7 A B C

G D0 D1 D2 D3 D4 D5 D6 D7 A B C

G D0 D1 D2 D3 D4 D5 D6 D7 A B C

U6 SN7404

SW-HL3

H L

U7 SN7408

1

A1

A1

P1

N2

N1

P2

G

N1

N2

P1

A2

A2

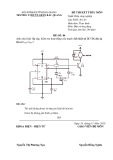

ấ ạ ủ 2 0,5 C u t o c a Triac

ộ ấ ẽ ẫ ấ ồ ớ TRIAC: là m t c u trúc g m 5 l p bán d n ghép xen k và có c u trúc

ư ắ ượ ẫ ủ ừ ề ầ nh 2 Thysistor m c ng c chi u nhau, các ph n bán d n c a t ng Thysistor

ệ ố ộ ượ ệ ớ ố ứ đ i x ng nhau m t cách tuy t đ i. Hai Thysistor này đ c các đi n v i nhau.

ừ ẫ ầ ở ữ ườ ộ ự ứ ố ọ T ph n bán d n P chung gi a ng ự i ta n i ra m t c c th 3 g i là c c

ề ể đi u khi n G.

ố t c a Thysistor 2 và

ớ ự ấ ị ể ồ ố ủ 1 và A2. 0,5

ng Nguyên t c ho t đ ng và cách kích m TRIAC

Còn An t c a Thysistor 1 đ u n i chung v i Kat ượ ạ c l i. Do v y ta có th quy đ nh nó g m 2 c c A ắ ặ ố ủ ậ ạ ộ ế ở ạ ố ứ ủ ắ ố ạ ộ Đ c tuy n VA c a Tri c có d ng đ i x ng nhau qua g c to đ .

ạ ộ ế ủ ể ễ ể ứ ạ ệ ấ Ho t đ ng chi ti t c a linh ki n này r t ph c t p, tuy nhiên đ d hi u ta ch ỉ

ườ ả ợ xét tr ơ ng h p đ n gi n sau:

ạ ộ ế ặ Khi UA1 > UA2 và UG > UA2 thì Thysistor bên trái ho t đ ng đ c tuy n có

ả ạ d ng bên ph i.

ạ ộ ả ặ ế Khi UA2 > UA1 và UG > UA1 thì Thysistor bên ph i ho t đ ng đ c tuy n

ạ có d ng bên trái.

0,5

ủ

ế Hình 1.35. Đ c tuy n V/A c a TRIAC ể ẫ ấ ạ ư ả ở ặ Do TRIAC có c u t o nh trên nên TRIAC có th d n dòng c hai hai

0,5 chi u. ề

ợ ở ủ ẽ ư c kích m cho

ạ ệ ệ

ớ ươ ươ ng so v i A

ở ể c:ượ

ng và G âm so v i A

ươ ớ ng so v i A

ề ọ

ớ ấ ng và G âm so v i A

ươ ớ ng so v i A

ề ạ ng

ộ ị ể 3 0,5

ọ ạ ọ ề ể ử ụ ả ử ụ ộ ị ờ

0,5

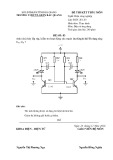

ứ ở ạ ộ trên, triac s đ Theo nguyên lý ho t đ ng c a triac đã nêu ấ ồ 2 và G đ ng d u, nghĩa là: dòng đi n ch y qua khi đi n áp A A2 d 1. ng và G d A1 âm và G âm so v i Aớ 1. ấ Ngoài ra A2 và G trái d u triac cũng có th kích m đ 1, có dòng đi nệ ớ ươ A2 d 1, không dòng đi n.ệ A2 âm và G d ạ ạ ấ ể Lo i này g i là lo i đi u khi n trái d u âm ạ ưở ế ạ ộ ố ng lo i triac M t s nhà ch t o cho xu t x 1, không dòng đi n.ệ ươ A2 d 1 có dòng đi nệ A2 âm và G d ấ ươ ể Lo i này g i là lo i đi u khi n trái d u d ờ H vi đi u khi n 8051 có hai b đ nh th i là Timer0 và Timer1 Đ s d ng các b đ nh th i này ta ph i s d ng các thanh ghi là: Timer0 (TH0 và TL0), Timer1 (TH1 và TL1), TMOD ủ Ch c năng c a các thanh ghi:

0,5

ị ủ ộ ị ư ữ ở + TH0 và TL0 l u tr giá tr c a b đ nh th i timer0 0,5

ị ủ ộ ị ư ữ ở + TH1 và TL1 l u tr giá tr c a b đ nh th i timer1 0,5

ế ậ ế ộ ệ + Thanh ghi TMOD: thi ủ ộ t l p các ch đ làm vi c khác nhau c a b

ấ ượ ờ ồ ế ị đ nh th i. Thanh ghi TMOD là thanh ghi 8 bít g m có 4 bít th p đ c thi t

ấ ộ ậ l p dành cho b Timer 0 và 4 bít cao dành cho Timer 1. Trong đó hai bít th p

ể ế ậ ế ộ ủ ộ ị ờ ủ c a chúng dùng đ thi ể t l p ch đ c a b đ nh th i, còn 2 bít cao dùng đ

ị xác đ nh phép toán

0,5

(MSB)

(MSB)

GATE C/T M1 M0

GATE C/T M1 M0

Timer1

Timer0

ộ C ng (I) 7

II. Ph n t ầ ự ọ ch n

3

4

ộ

ổ C ng (II) ộ T ng c ng (I+II)

…….., ngày …..tháng …..năm …….

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)