Trang 1/18

GIAO DIỆN NỐI TIẾP TỐC ĐỘ CAO DÙNG CHO

CÁC ỨNG DỤNG DI ĐỘNG

Tác giả: Gerrit W. den Besten

NXP Semiconductors

Research Eindhoven (NL)

gerrit.den.besten@nxp.com

Tóm tắt:

Tài liệu này trình bày về giải pháp giao diện cổng nối tiếp (serial) tốc độ cao công

suất nguồn hiệu quả, mục đích dùng trong việc vận hành nguồn pin của các thiết bị di

động hoặc cầm tay. Ở tài liệu này, kể cả cơ chế thu phát và giao thức tín hiệu đều

được trình bày. Tín hiệu vi phân tốc độ cao và CMOS được kết hợp trên cùng một

mạch điện. Kênh tín hiệu bao gồm đường truyền quản lý các thành phần công suất và

cung cấp các cơ chế giao tiếp đa dạng nhằm tương tích một cách hiệu quả đối với các

nhu cầu băng thông. Giao diện này được thiết lập trong CMOS 65nm và kết quả đo

lường được trình bày ở phần sau.

1. Giới thiệu

Việc nhu cầu về băng thông trên giao diện và giảm số lượng pin, là một quá trình

chuyển đổi từ đường truyền CMOS cổ điển sang giao diện Serial tốc độ cao. Đặc biệt

cho các kết nối truyền dữ liệu qua những cấu trúc phức tạp như điện thoại di động, đòi

hỏi một giao diện nhỏ gọn và linh hoạt. Đối với các thiết bị di động, tiêu thụ điện năng

là vấn đề vô cùng quan trọng, cần phải được ứng dụng những giải pháp mới hơn là sử

dụng những tiêu chuẩn hiện tại. Bên cạnh giá trị kỹ thuật, một chuẩn giao diện mới

trong lĩnh vực này giúp làm giảm nhu cầu đa dạng về giao diện, kích thích khả năng

tương thích IC của nhiều hãng khác nhau và cho phép tiếp cận hệ thống dưới dạng

module. Những thành phần xây dựng cho sự phát triển này được định nghĩa theo

chuẩn công nghệ lớp vật lý [1].

Tài liệu này bắt đầu từ việc phân tích các dạng tính hiệu, băng thông, công suất,

kết cấu IO, và sự lựa chọn triển khai (Sections 1-4). Kết quả theo kết cấu IO là điểm

khởi đầu nhằm giới thiệu một giải pháp hoàn chỉnh cho lớp vật lý bao gồm cả giao

thức về tín hiệu (Sections 5-8). Kết quả đo lường và kết luận được trình bày tại Mục 9

và 10 bên dưới.

Trang 2/18

Giải pháp giao diện Serial hoàn toàn tối ưu phù hợp cho ứng dụng như camera,

màn hình, và các thiết bị cầm tay di động khác với nhu cầu về băng thông thay đổi từ

IC đến IC (chip to chip) và từ bảng mạch đến bảng mạch (board to board).

2. Cơ chế Quasi - tĩnh so với tín hiệu đường truyền

Nhiều năm qua, tín hiệu bất tận rail-to-rail trên CMOS đã và đang là công nghệ

chiếm ưu thế trên giao diện cho ứng dụng di động vì điện năng tiêu thụ tĩnh bằng 0 và

sự đơn giản trong phần cứng. Tuy nhiên dựa trên giả thuyết Quasi-tĩnh [2], việc không

mất thời gian quảng bá tín hiệu thì không thể đáp ứng được nữa theo yêu cầu của băng

thông với số lượng dây dẫn hợp lý.

Hơn nữa, với CMOS IO các đường dòng điện hồi tiếp không phải luôn luôn gần

với tín hiệu ngõ đơn kết thúc mà có thể tạo ra vòng lặp đáng kể. Nó có thể tạo ra các

vấn đề về nhiễu từ EMI đặc biệt là các dòng điện tăng đột biến liên quan đến các tín

hiệu CMOS (xem hình số 1).

Khi thời gian quảng bá tín hiệu tương đương với độ lớn (1/5 hoặc lớn hơn) thời

gian truyền tải tín hiệu (chú ý, không phải thời gian bit (bit time)), các đường liên kết

trung gian cho truyền tín hiệu phải được xem như là đường truyền dẫn và những

đường này phải được kết cuối nhằm đảm bào tính toàn vẹn của tín hiệu. Vì thế, việc

các đường dẫn có thể được thực hiện từ yêu cầu tốc độ cao và/hoặc khoảng cách xa

hơn. Đối với tín hiệu giới hạn ở tỉ lệ rất thấp, giới hạn cho giả thuyết quasi-tĩnh được

mô tả sơ lược như [3]: Tốc độ[Gbps]xkhoảng cách[cm]=2 (Speed[Gbps] x

Distance[cm] = 2). Ví dụ: một đường link serial > 100Mb/s với chiều dài >20cm, kết

cuối là nhu cầu ít nhất nếu không cần thiết. Tuy nhiên, việc kết cuối đường truyền

tiêuthụ điện năng tĩnh. Điện năng tiêu thụ có thể giảm nhờ dao động tín hiệu thấp hơn.

Tín hiệu tức thời (vi phân) cho phép một dao động rất nhỏ, nhờ phát hiện dễ dàng giá

trị tức thời zero-crossings trong khi nó cũng làm giảm kích cỡ vật lý cho vòng lặp

dòng điện tạo thuận lợi cho việc giảm nhiễu EMI.

3. Công suất

Trong các mạch CMOS không kết cuối thông thường, chi phí năng lượng là “trả

theo bit” (pay per bit) (thật ra là theo truyền tải – actually per transition), được xác

định bằng việc nạp và xả từ đường kết nối liên kết và thiết bị được kết nối. CMOS

điện thế thấp (LVCMOS) IO có năng lượng rất hiệu quả cho link ngắn, nhưng năng

lượng sử dụng tỉ lệ thuận với khoảng cách. Hơn nữa tốc độ đạt được tỉ lệ nghịch với

khoảng cách, vì vậy giải pháp này trở nên không thích hợp cho giao diện băng thông

rộng vì nó đòi hỏi tính song song cao.

Trang 3/18

Nhằm mục đích so sánh hiệu quả công suất có thể xem xét giá trị: Năng lượng/Bit

bằng với Tỉ lệ Công Suất/Tốc độ: pJ/bit=mW/Gbps. (Energy/Bit metric =

Power/Speed ratio: pJ/bit=mW/Gbps)

Đối với đường truyền tốc độ cao được kết cuối, một thành phần phụ của công suất

tiêu thụ được cố định dựa trên điểm cuối của đường dây và mạch biến thiên toàn phần,

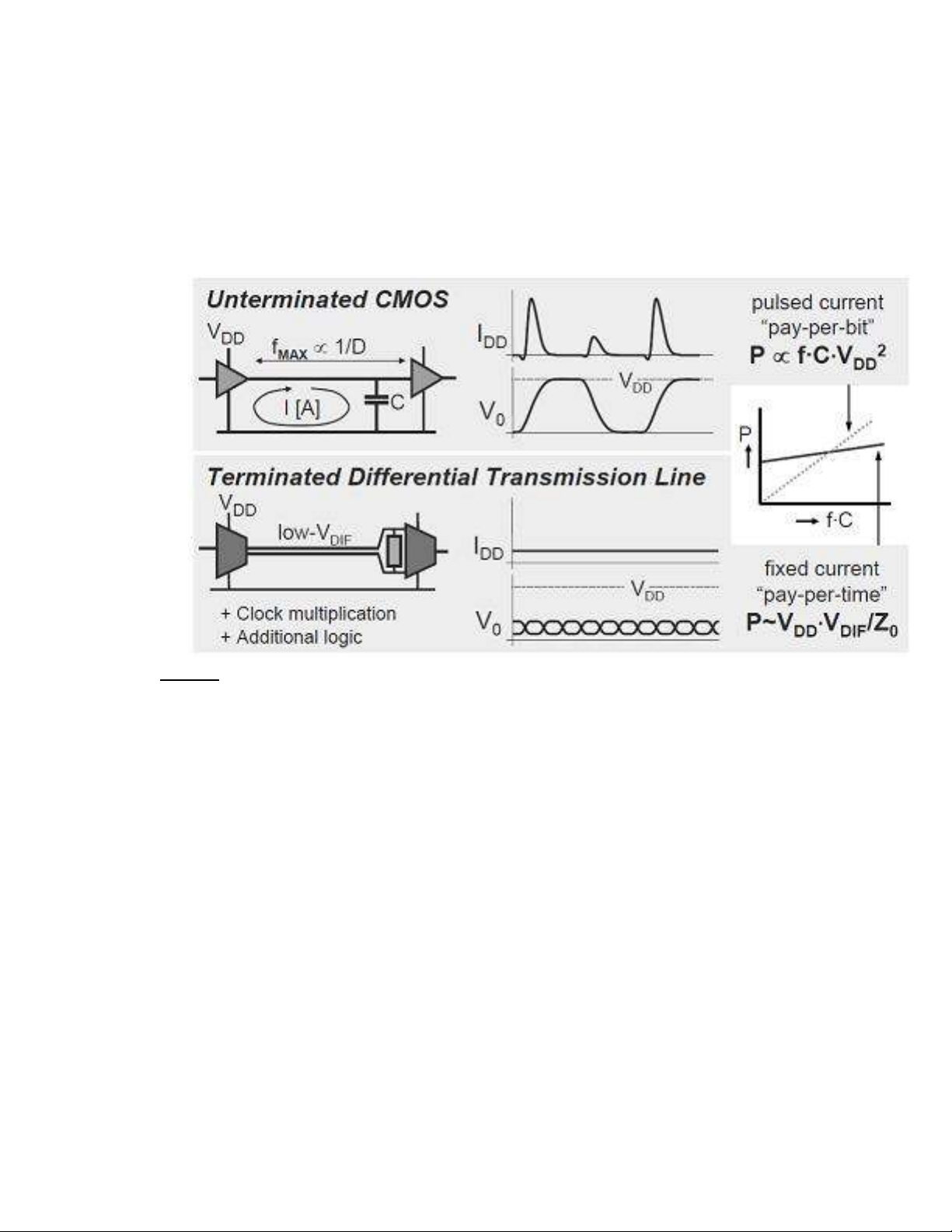

vì thế hao phí năng lượng được tính trên “theo thời gian” (pay-per-time). Hình số 1

mô tả 2 trường hợp này:

Hình 1: So sánh giữa tín hiệu CMOS không kết cuối và truyền dẫn thay đổi tốc độ cao

Để đạt hiệu quả công suất cho các link kết cuối (vi phân), năng lượng cố định này

có thể được khai thác tối ưu bằng cách truyền tải tối đa số lượng bit theo thời gian khi

vận hành. Điều này có nghĩa là tối ưu hóa băng thông có thể có được trong dữ liệu tốc

độ cao bộc phát và kết thúc đường truyền trong khoảng thời gian còn lại thể hiện

nguyên lý truyền tải dạng gói. Khoảng thời gian mào đầu bổ sung cho việc khởi động

và dừng đường truyền cũng ảnh hưởng đến toàn bộ hiệu quả năng, do đó điều quan

trọng là khoảng thời gian này cần phải rất ngắn, đặc biệt là trong trường hợp nếu nhiều

gói rất nhỏ thường xuyên phải trao đổi. Việc gom nhóm dữ liệu truyền có thể giảm

thời gian và số lượng mào đầu và cải thiện hiệu quả công suất.

4. Công nghệ giao diện IO tốc độ cao

Cơ cấu IO của nhiều giao diện tốc độ cao bao gồm một hoặc nhiều cặp vi phân

điều khiển dòng điện. Tuy nhiên, điều này không phải là tối ưu đối với công suất tiêu

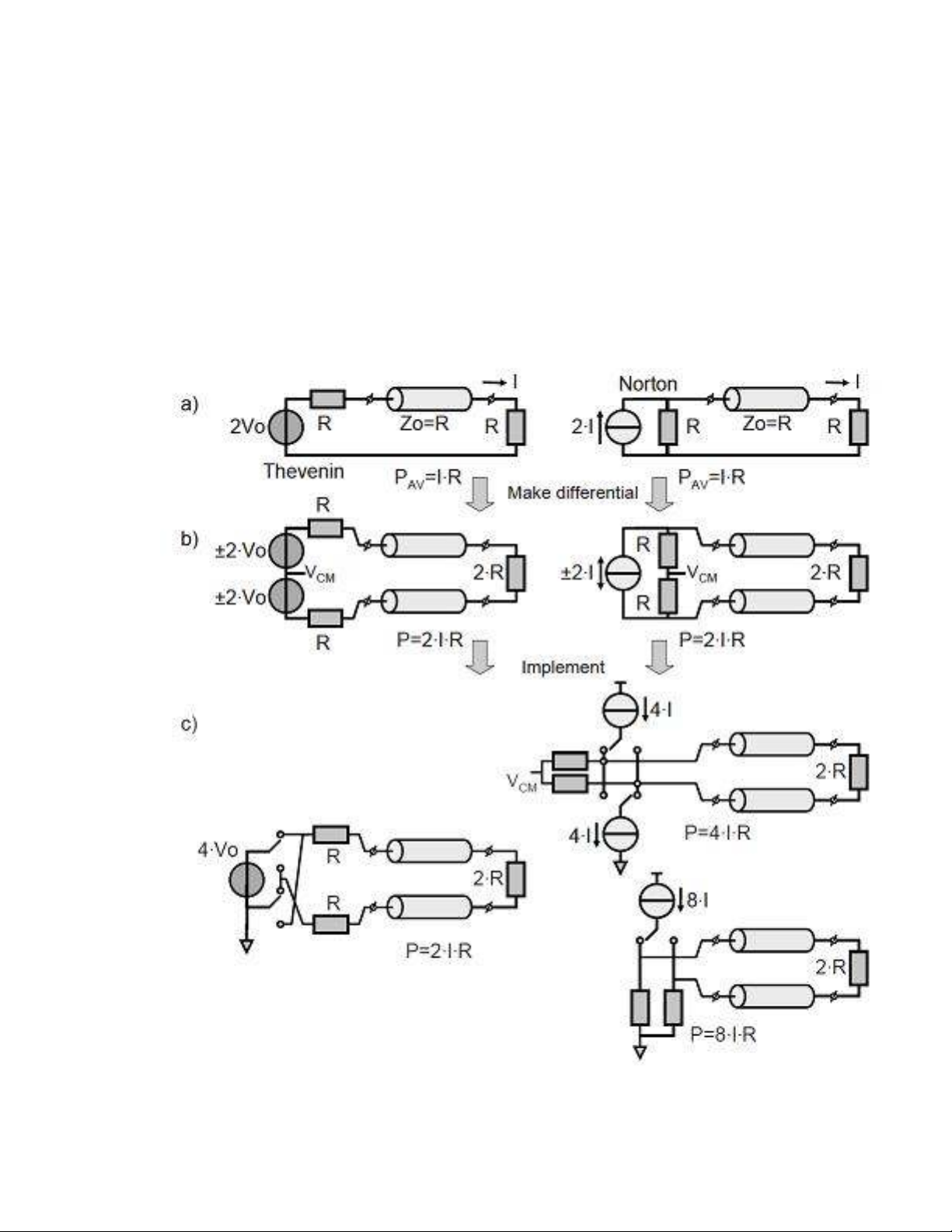

thụ và quá trình mở rộng quy mô. Điều này có thể dễ dàng chứng minh bắt đầu từ mạh

tương đương ngõ đơn Thevenin và Norton cho điều khiển dòng như được trình bày

Trang 4/18

trong hình 2a (bên trên). Hai mạch theo định nghĩa cho thấy những tính năng giống

nhau trong các chân đầu ra, nhưng điều quan trọng là nhận thấy một số khác biệt, ngay

cả khi cả hai trường hợp được ngắt một cách phù hợp:

Trong mạch tương đương Thevenin, nguồn điện áp với giao động kép 2.Vo

(=2.I.R), trong khi chỉ có 1 dòng I chạy qua các nguồn kết nối nối tiếp và các trở

kháng kết cuối ở đầu xa.

Trong mạch tương đương Norton, có nguồn dòng 2.I điều khiển áp, nhưng thực tế

không đạt được. Dòng này được chia bởi nguồn song song được kết nối và điện trở

cuối, tạo nên I.R (=Vo), tại nút điện áp cao nhất.

Trang 5/18

Hình 2: Giao tiếp IO chuyển mạch điện áp (bên trái) so sánh với giao tiếp IO chuyển

mạch dòng (bên phải): a) các mạch tương đương một ngõ Thevenin và Norton, b) Các

mạch tương đương riêng rẽ, c) Cấu trúc giao tiếp IO chuyển mạch điện áp so sánh với

giao tiếp IO chuyển mạch dòng; loại chuyển mạch dòng có bù và loại ngõ đơn.

Hình 2b (giữa) cho thấy mạch vi phân tương đương Thevenin va Norton bởi vì

trong giai đoạn tính toán sau cùng cần phải tính giá trị tức thời.

Hình 2c cho thấy sơ lược về cách triển khai. Triển khai theo dạng Thevenin thì đơn

giản hơn, đấy là một cầu nối điện thế với các chuổi điện trở tại các điểm cuối thích

hợp [4,5]. Nếu 4.Vo = 4.I.R không trực tiếp sẵn sàng, nó có thể được tính từ nguồn

cung cấp với bộ chỉnh lưu (giả sử rằng 4.I.R < VDD, luôn luôn đúng trong tình trạng

thực tế).

Triển khai dựa trên kết quả của mạch tương đương Norton thường cho thấy tính vi

phân trên các cặp trình điều khiển. Để đạt hiệu quả về công suất, cấu trúc điều khiển

bổ sung với cả hai nguồn chính và phụ (ẩn - sink) vi phân đặt lệch pha là cần thiết, bởi

vì trong trường hợp đó toàn bộ dòng điện sẽ được tối ưu hóa để tạo ra một dao động

đơn. Kết cấu điều khiển này đã phổ biến với các chuẩn [6,7,8]. Tuy nhiên, nó lại hoạt

động theo dạng thức kiểu chung (common-mode level) một hướng cấp nguồn điện áp,

làm tăng yêu cầu điện áp cung cấp cần thiết cho cả hai mạch phát và mạch thu. Điều

này gây khó khăn cho kết cấu (hoặc không thể) trong việc triển khai CMOS cao cấp

dựa trên sự hạn chế của nguồn điện cung cấp.

Vì thế, trong các chuẩn khác, chế độ common-mode đã và đang được chọn trong

cả hai mức thấp hoặc cao bằng cách ngắt một trong hai nguồn cung cấp [9,10,11].

Điều này có nghĩa rằng thiết lập một chuyển mạch dòng, dòng điện có thể được dẫn

với một hướng duy nhất: kéo hoặc đẩy (nguồn hoặc cấp), dựa tùy theo điểm cuối là

VSS hay VDD.

Theo cách triển khai tổng quát, điện năng tiêu thụ của tất cả các giải pháp có thể

được so sánh. Giả sử rằng 2.I.R phù hợp với cung cấp và các mạch được thiết lập sử

dụng cùng một nguồn cung cấp, điều này có nghĩa rằng (theo Norton) mạch chuyển

mạch dòng (switch-current) tiêu thụ 2 lần công suất nguồn, bởi vì nó mất gấp đôi dòng

điện từ nguồn so với việc thực hiện chuyển mạch áp (switch-voltage).

Trong trường hợp sử dụng bộ điều khiển chuyển mạch dòng kéo hoặc đẩy, hiệu

quả sử dụng nguồn giảm theo hệ số 2. Để điều khiển được, bộ điều khiển bằng chuyển

mạch dòng yêu cầu nguồn cung cấp 1.8V hoặc cao hơn, trong khi điều khiển chuyển

mạch áp chỉ cần vài trăm mV đã có thể xử lý, điện áp này cò thể được tạo ra bằng bộ

biến đổi DC-DC, giải pháp chuyển đổi điện thế trở nên thuận lợi hơn. Qua sự so sánh

này, điều khiển chuyển mạch áp hiệu quả và vượt trội hơn.

Phân tích trên cho thấy với các ứng dụng di động, một chuyển mạch điện thế ngày

càng trở nên thu hút hơn. Nó tiết kiệm ít nhất 4 lần công suất so với điều khiển chuyển

mạch dòng vi phân một phía, thậm chí có khả năng tăng lên 10 lần hoặc hơn nữa. Hơn

![Hệ thống quản lý cửa hàng bán thức ăn nhanh: Bài tập lớn [chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251112/nguyenhuan6724@gmail.com/135x160/54361762936114.jpg)

![Bộ câu hỏi trắc nghiệm Nhập môn Công nghệ phần mềm [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251111/nguyenhoangkhang07207@gmail.com/135x160/20831762916734.jpg)