Chương 5:Công nghệ mạch tích hợp

22

Chương 5

CÔNG NGHỆ MẠCH TÍCH HỢP

5.1. Các bước thiết kế IC

Hình 5.1 Các bước thiết kế tạo IC

Ý tưởng

Thiết kế kiến trúc

Thiết kế Logic

Thiết kế vật lý

Sản xuất

Chip mới

Chương 5:Công nghệ mạch tích hợp

23

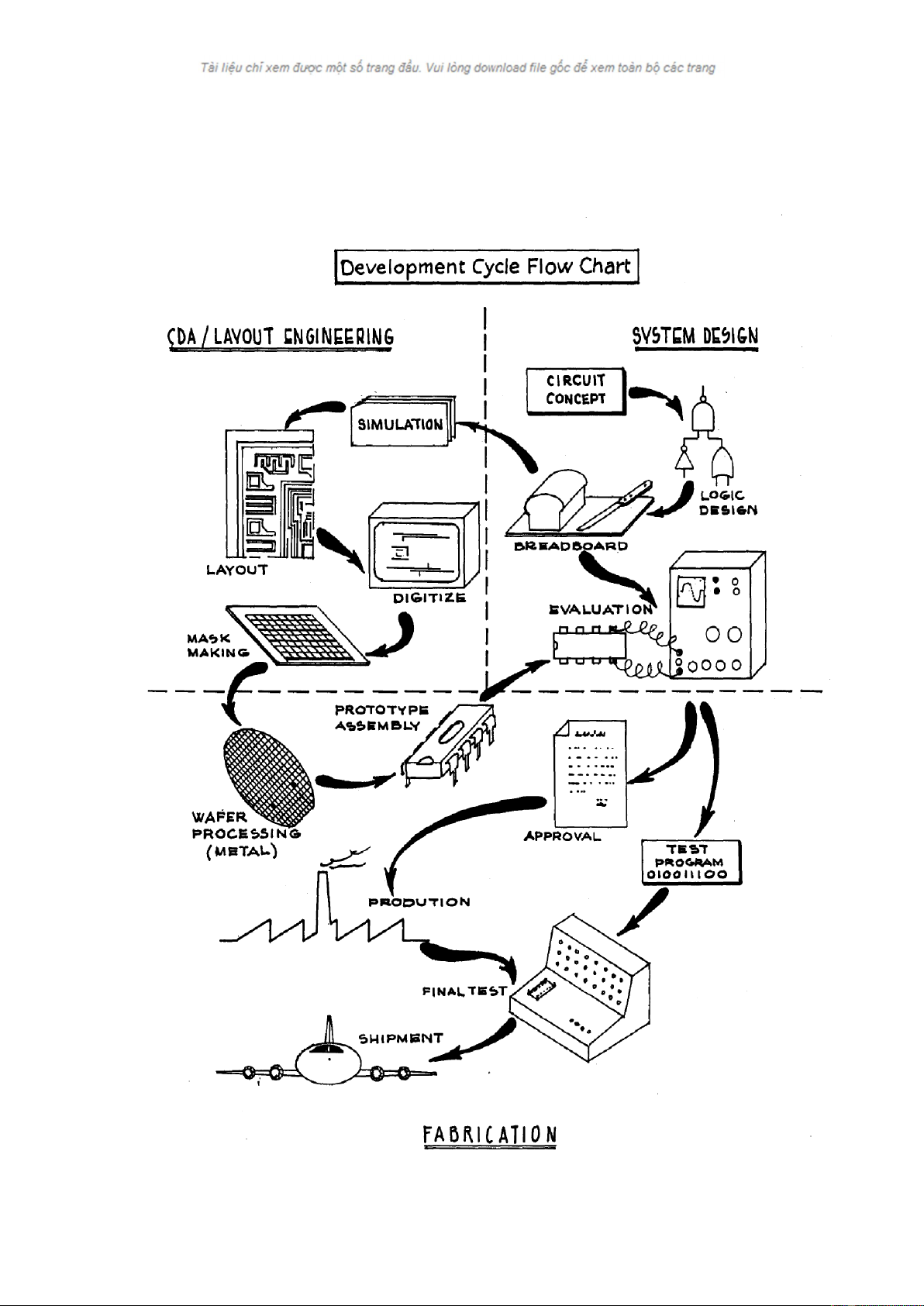

5.2. Các bước chế tạo IC

Chương 5:Công nghệ mạch tích hợp

24

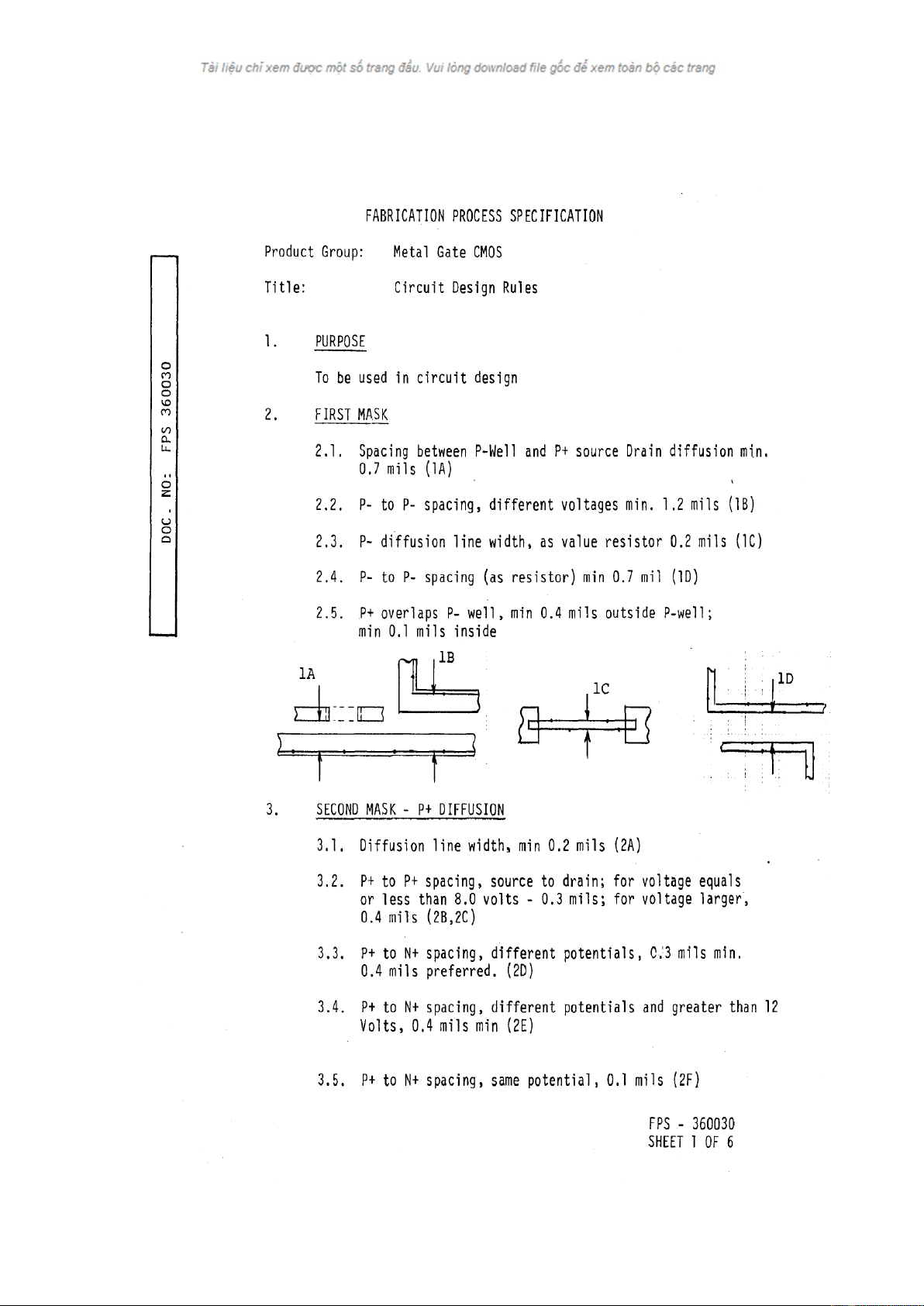

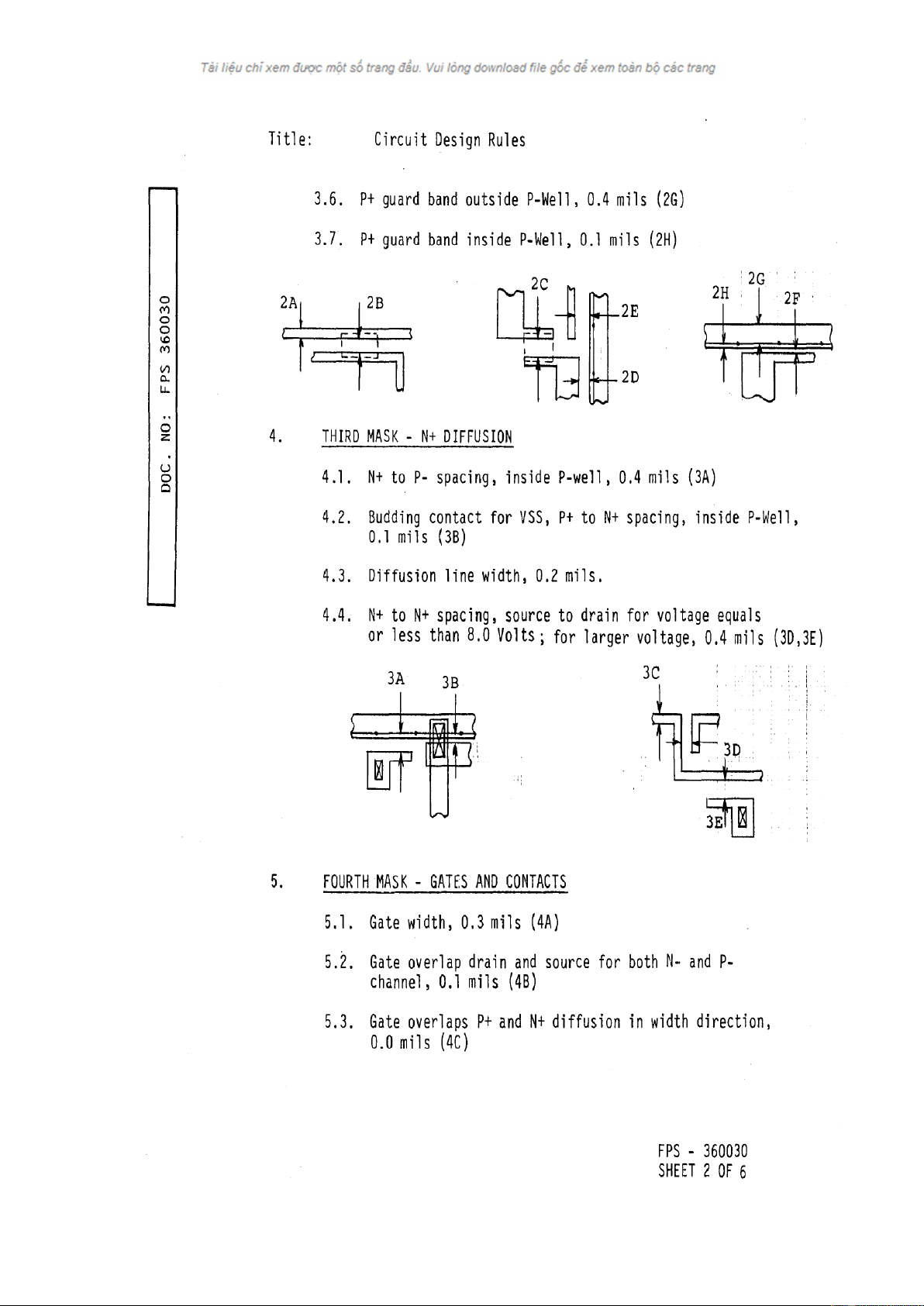

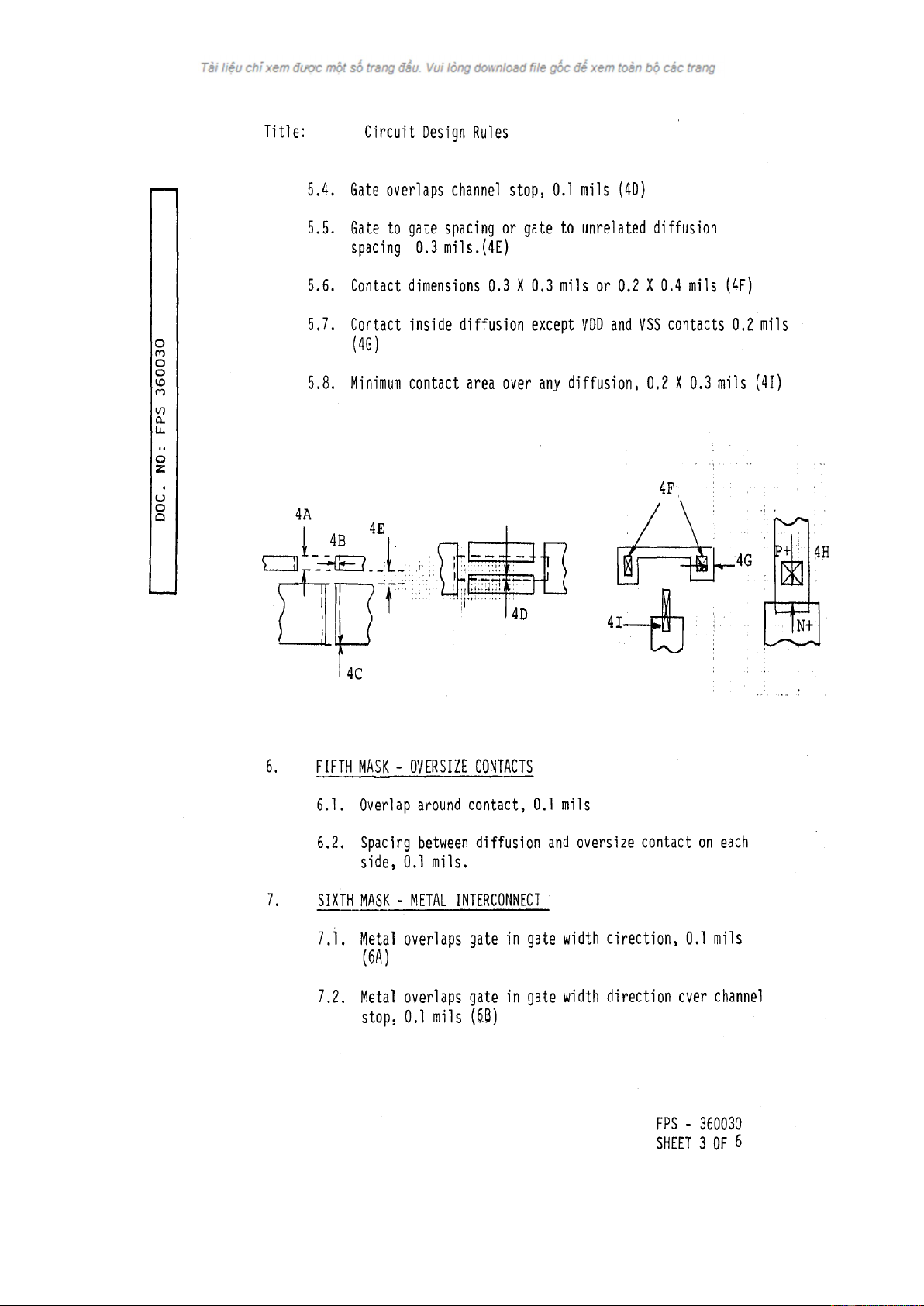

5.3. Quy tắc layout vi mạch

Chương 5:Công nghệ mạch tích hợp

25

Chương 5:Công nghệ mạch tích hợp

26

![Giáo trình CAD và ứng dụng (Phần thực hành): [Hướng dẫn chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260305/hoatulip2026/135x160/80431773135924.jpg)