416

bit địa chỉ từ 5 cho Fk0

~và 6 cho Fk1

~và Fk2

~. Cho các hệ số cố định, có thể dùng

bộ nhớ chỉ đọc (ROM) hoặc bộ nhớ lập trình có khả năng xoá được

(EPROM).

Sơ đồ thực hiện của các khối cho trong hình 16.2. Mạch điện hoạt động như

sau:

1. Đầu vào cho các EPROM là các bit của giá trị đầu vào hiện tại và 8 giá trị

đầu vào trước và tám giá trị giá trị đầu ra rút ra từ mạch điện hình 16.1.

2. Các bit này dùng như địa chỉ đầu vào của ba EPROM của mạch điện hình

16.2.

3. Các giá trị đầu ra từ mỗi EPROM là một giá trị L-bit biểu diễn cho Fk0

~,

Fk1

~hoặc Fk2

~.

4. Nếu L là số các bit biểu diễn dữ liệu vào / ra, thì tại điểm bắt đầu của mỗi

chu kỳ xung nhịp L các phần tử tích luỹ từ ACC1 đến ACC3 được xoá.

5. Fk0

~, Fk1

~, và Fk2

~ là giá trị cho k = L.

Chú ý là

00

~

,0

~

1

2

1,0

~

1

2

01

~

1

2

~)...)2.(2...(2),( FFFFmny KK

I

(16.14)

và tương tự cho yII(n,m) và yIII(n,m).

6. Fk0

~, Fk1

~ và Fk2

~được cộng (cộng phần bù hai) với ACC1, ACC2, và ACC3.

7. ACC1, ACC2, và ACC3 được dịch phải 1 bit (một dịch phần bù hai).

8. Các bước 5 và 6 được lặp lại với k = L - 1, L - 2, ..., 1.

9. Tiếp theo, F00

~, F10

~ và F20

~được đọc từ các EPROM và được trừ với ACC1,

ACC2, và ACC3.

10. Các giá trị chứa trong ACC1, ACC2, và ACC3 bây giờ được cộng bit với

bit qua một thanh ghi dịch vào song song ra nối tiếp (PISO) để thành

y(n,m).

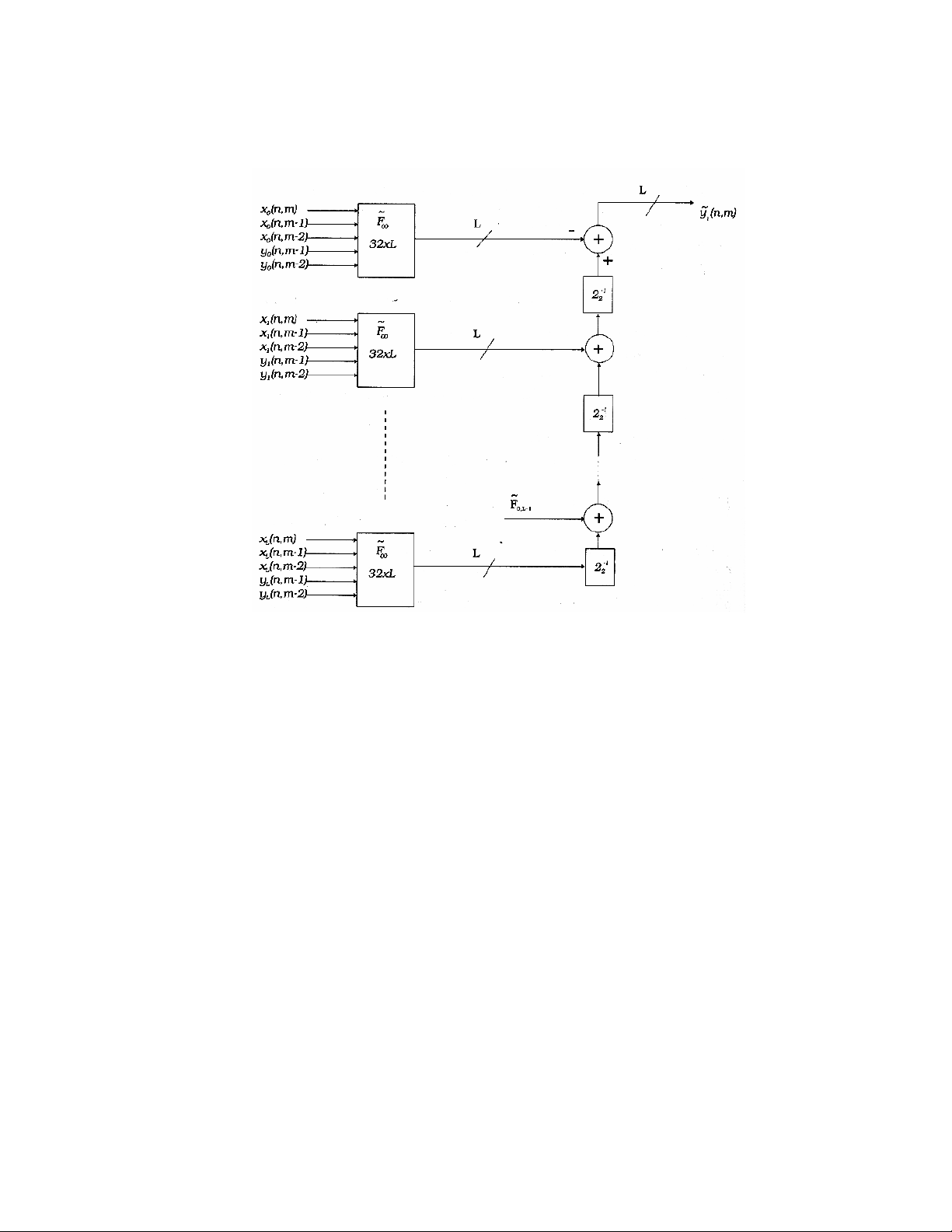

Dạng cấu trúc trong sơ đồ hình 16.1 và 16.2 biểu diễn một dạng đơn giản

của chức năng bộ lọc IIR 2 2, 2-D. Cấu trúc yêu cầu L + 1 chu kỳ xung nhịp

để tạo ra một tín hiệu đầu ra. Chu kỳ xung nhịp được điều khiển bởi thời gian

xử lý cho EPROM, thời gian trễ cho các phần tử cộng và trừ, thời gian trễ cho

các thanh ghi dịch, ... Các yếu tố này có thể giới hạn tốc độ ra thấp hơn tốc độ

video. Vì vậy, các bộ bộ chức năng tốc độ cao có khả năng xử lý đồng thời cho

tất cả các bit đầu vào và đầu ra được đề cập đến ở phần dưới đây.

16.2.3 Xử lý đồng thời

Các thao tác đồng thời có khả năng xử lý song song cho (L+1) đầu vào và

đầu ra tại một thời điểm. Điều này có thể thực hiện dễ dàng bằng cách thay 12

417

thanh ghi dịch (SR1-SR12), là các thanh ghi kiểu vào nối tiếp ra nối tiếp

(SISO) bằng các thanh ghi dịch kiểu vào song song ra song song (PIPO), và

các dây trễ bằng kiểu vào song song ra song song. L + 1 bit dữ liệu vào ra có

thể xử lý đồng thời dùng các phần tử thực hiện dạng song song. Một phần tử

chức năng song song cho y n m

I

~( , ) được cho trong hình 16.3. Các phần tử chức

năng cho y n m

II

~( , ) và y n m

III

~( , ) được phát triển một cách tương tự. Chú ý là

tần số xung nhịp được điều khiển bằng khoảng thời gian trễ lớn nhất, dẫn L bit

đến đầu ra. Tất cả các cấu trúc này quá tốn kém cho thực hiện, và tất cả có thể

là không thực tiễn. Vì vậy, một cấu trúc chức năng khác, mà chúng ta đề cập

đến ở phần cuối, sẽ yêu cầu ít phần cứng hơn và cho ta một tốc độ đáp ứng

nhanh hơn.

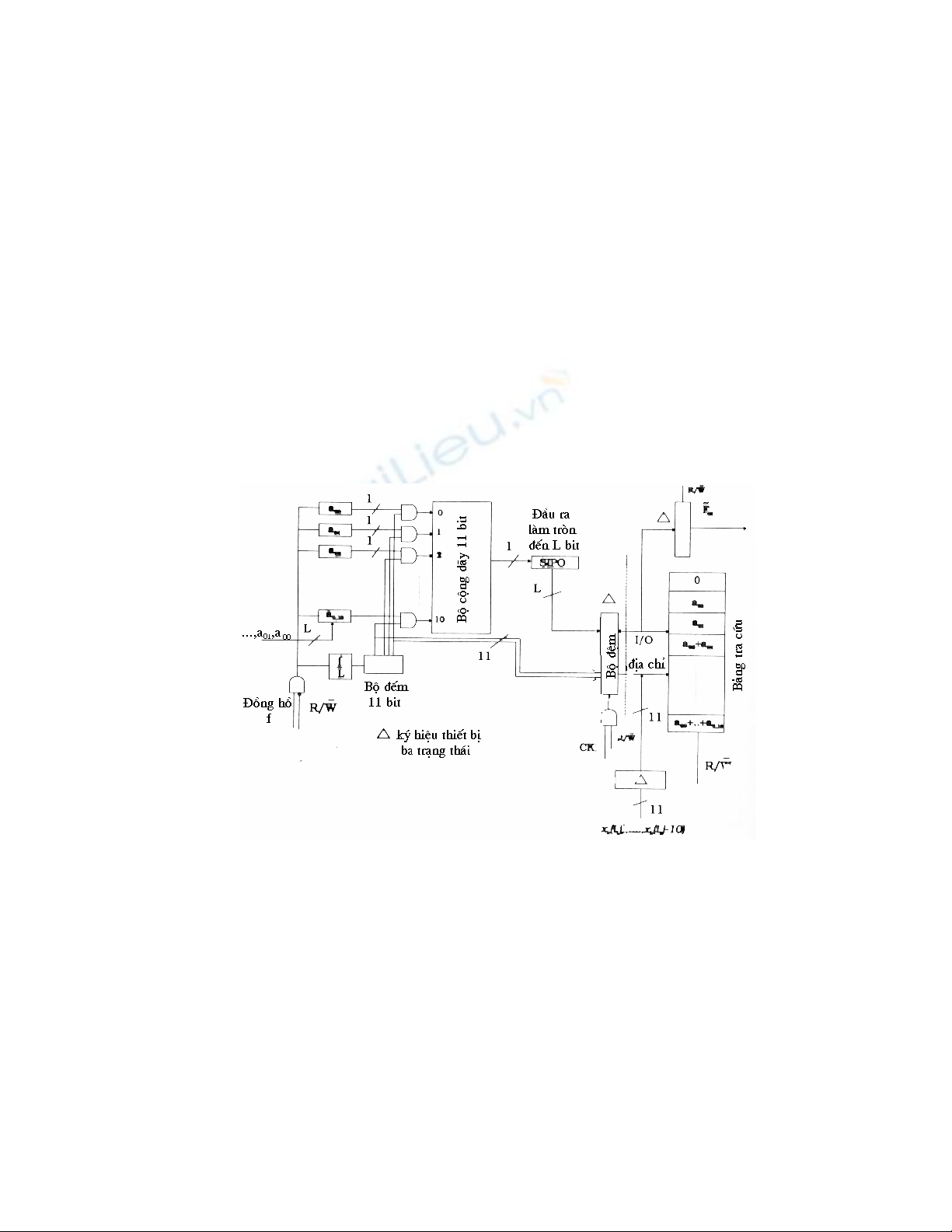

Hình 16.3 Cấu trúc song song cho ),(

~mnyI.

Thực hiện bộ lọc FIR. Một hàm truyền đạt của bộ lọc FIR 2-D được cho

bởi

N

i

N

j

ji

ij zzazzH

0 0 2121 ),( (16.15)

Cho bộ lọc có kích thước 10 10 mối quan hệ giữa đầu vào và đầu ra được

cho bởi

418

10

0

10

0

),(),(

i j ij jminxamny (16.16)

mà có thể viết thành

10

0

),(),(

iimnymny (16.17)

Ở đây

10

0

),(),(

jiji jminxamny (16.18)

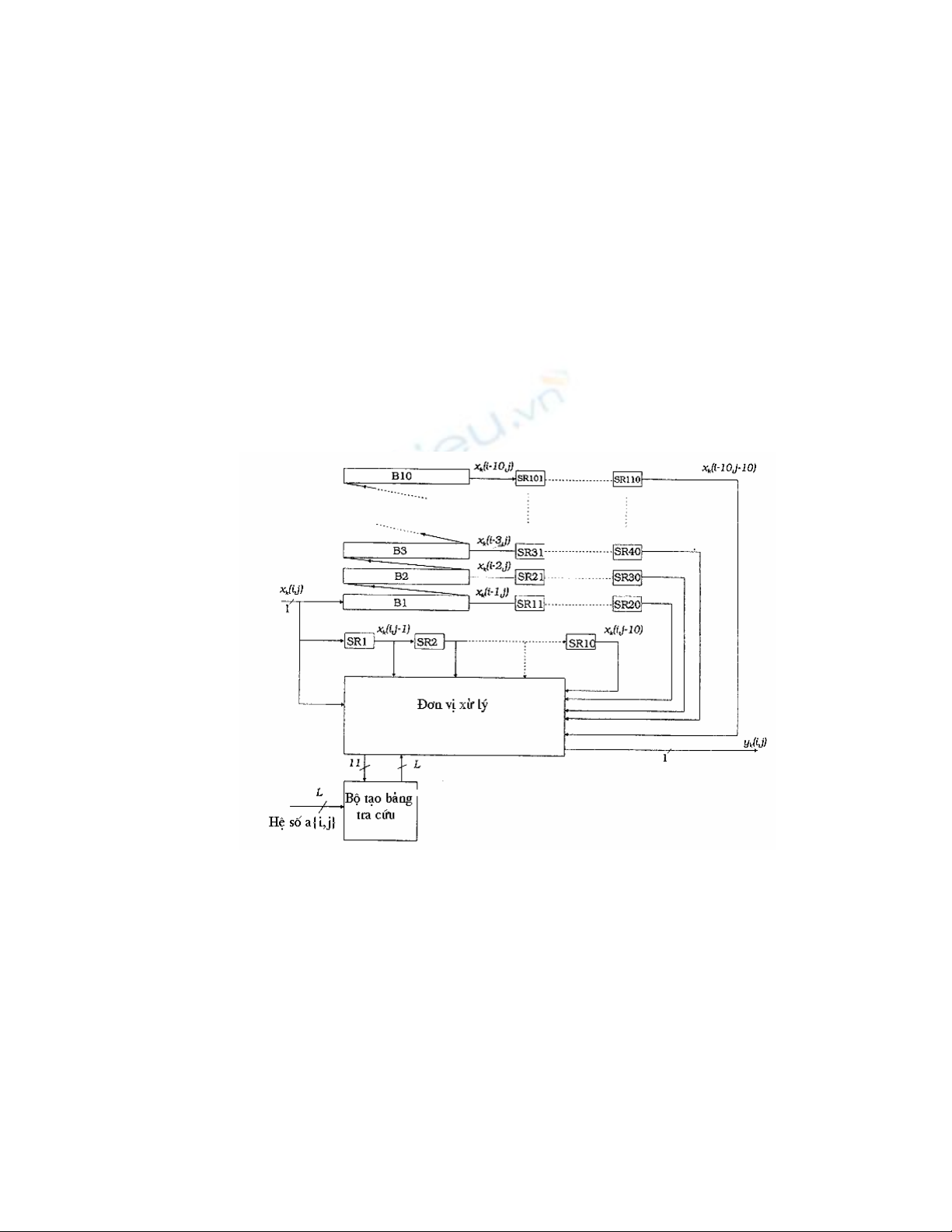

Thực hiện của bộ lọc bậc 10 được giới thiệu trong hình 16.4. Hoạt động của

bộ lọc này giống như hoạt động của bộ lọc IIR. 11 bảng tra cứu trong khối xử

lý giới thiệu trong hình 16.5 có kích 2048 L bit. Trong hình 16.4 có cả mạch

điện của các khối trong bảng tra cứu. Mạch điện cho tổng quát cho bảng tra

cứu được giới thiệu trong hình 16.6, và hoạt động của nó được trình bày ở

phần tiếp theo.

Hình 16.4 Bộ lọc 2-D kích thước 10.

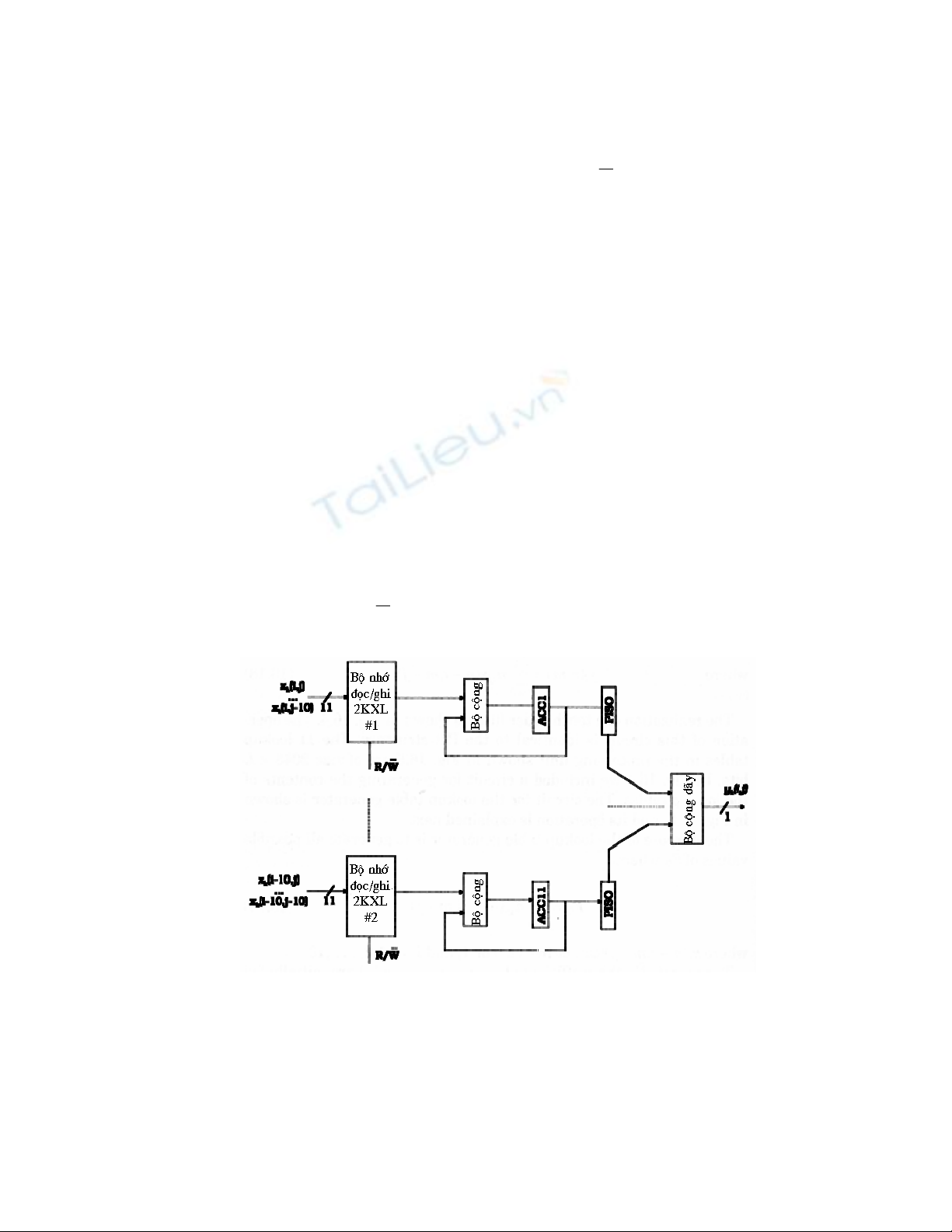

Chức năng tạo bảng tra cứu là tạo ra tất cả các giá trị có thể của Fik

~

10

0

~~ ),(

jk

ijik jminxaF (16.19)

ở đây xk(n-i,m-j) có thể là 0 hoặc 1, và i = 0, 1, 2, ..., 10.

419

Để tạo Fk0

~các hệ số {a00, a01, a02, ..., a0,10} được nạp ban đầu vào 11 thanh

ghi L bit, bộ đếm 11 bit được xoá sạch, và dòng

R

W

/

trong bảng nhớ tra cứu

được xoá về 0 (viết). Bộ đếm 11 bit, được đánh địa chỉ 2k L R/W bộ nhớ

(bảng tra cứu) và 11 cổng AND, được tăng tốc độ f/L, ở đây f là tần số xung

nhịp. Các thanh ghi chứa các hệ số { a00, a01, a02, ..., a0,10} được dịch ra nối

tiếp tại tốc độ f bit/sec.

Mạch điện này hoạt động như sau:

1. Khi bộ đếm tăng lên 1 nó đánh địa chỉ trong bảng tra cứu. a00 chỉ là hệ

số mà cho phép đưa qua mảng cổng AND vào bộ cộng 11 bit nối tiếp, và

qua thanh ghi SIPO được đặt trên đường vào/ra của bộ nhớ R/W, và

chứa trong bộ nhớ thứ hai.

2. Bộ đếm tiếp theo được tăng lên 2 (000 ...10 trong hệ nhị phân), và được

đánh địa chỉ trong vùng nhớ thứ 3 trong bảng tra cứu, và tương tự như

bước trên a01 được chứa vào vùng thứ ba.

3. Bộ đếm được tăng lên 3 (000...11 trong hệ nhị phân). a00 và a01 bị lấy ra

khỏi bộ cộng 11 bit, được cộng và chứa vào thanh ghi dịch SIPO để

chứa vào vùng thứ tư của bộ nhớ R/W.

4. Tiếp tục cho đến khi bộ đếm trở về 0, là vào lúc này bảng tra cứu sẽ

chứa tất cả các tổ hợp của Fk0

~.

5. Tiếp theo dây

R

W

/

được đặt bằng 1 nên Fk0

~ có thể đọc từ bộ nhớ R/W.

Hình 16.5 Đơn vị xử lý cho bộ lọc FIR của hình 16.4

420

Bài tập 16.1 Phát triển một chương trình C cho phép tạo ra các phần tử

của bảng tra cứu cho các hệ số của một bộ lọc IIR hoặc là FIR.

Bài tập 16.2

1. Dùng chương trình phát triển trong cuốn sách thiết kế một bộ lọc 2 x2

xấp xỉ bộ lọc thông cao tuần hoàn đối xứng có điểm cắt tần số là 1 rad/sec.

Dùng đặc tuyến của hàm Butterword bậc 1.

2. Cắt bớt các hệ số thành 11 bit, và in đáp ứng biên độ và đáp ứng pha.

So sánh với bộ lọc chưa bị sửa đổi.

3. Tạo ra bảng tra cứu cho kiến trúc nối tiếp và cung cấp một ví dụ cho

hoạt động của mạch điện.

Bài tập 16.3 Thiết kế một sơ đồ mạch điện tạo ra bảng tra cứu cho một

bộ lọc IIR 2 2.

Hình 16.6 Bộ tạo bảng tra cứu cho bộ nhớ R/W

Kiến trúc chúng ta nghiên cứu được phát triển ban đầu bởi Peled và Liu cho

trường hợp 1 chiều, và được mở rộng ra hai chiều bởi tác giả. Một cấu trúc

tương tự nhưng kém đơn giản được phát triển bởi Jaggernauth và một số người

khác cho thực hiện bộ lọc IIR 2 2 và được thực hiện bằng phần cứng. Giá

của phần cứng này là trên $2000, và thiết kế này không có khả năng cho tốc độ

video thời gian thực.