452

điện vào trong điện trở R0, điện áp trong dây 0 sẽ bằng 0, và nó thay thế cho

a0. Các mạch điện khác sẽ chuyển các giá trị của ai đến đầu ra của chúng. Nếu,

nói một cách khác, a0 không bằng maxi, thì đầu ra của các bộ vi phân sẽ không

bằng không. Các mạch điện tuyệt đối sẽ tạo ra một giá trị có thể để mở các

chuyển mạch sw01 và sw02. a0 bây giờ sẽ theo dây 0, và giá trị cực đại, maxi,

sẽ bị chuyển tới mạch điện con tiếp theo. Chú ý rằng R0 = R1 = … = R8.

Chú ý rất nhiều phần tử trong mạch điện bao gồm các khối của hình 16.39

được biết, nó rất dễ cho bài tập xây dựng mạch điện cho lọc trung vị. Chú ý

rằng trong hình 16.39 các mạch điện 2 đến 5 có cùng một thiết kế. Cấu trúc

này hoàn toàn là một cấu trúc pipeline. Rõ ràng thiết kế này có thể dùng cho

xử lý video thời gian thực.

Bài tập 16.8 Đưa ra một mô phỏng SPICE trên các mạch của hình 16.41 và

16.42. Cho các khuếch đại thuật toán dùng các tham số của một kiểu video mà

thường được tìm thấy trong sổ tay cung cấp bởi nhà sản xuất.

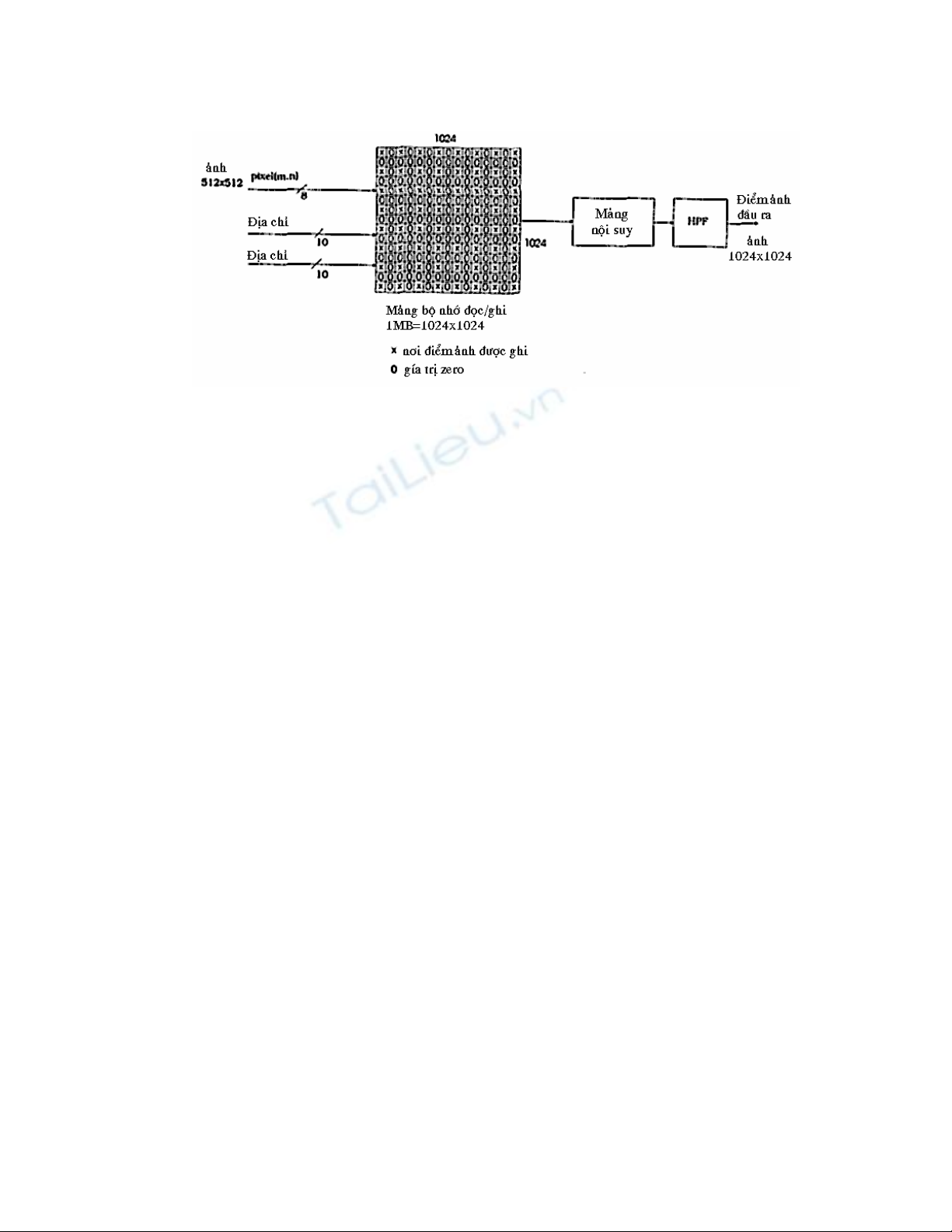

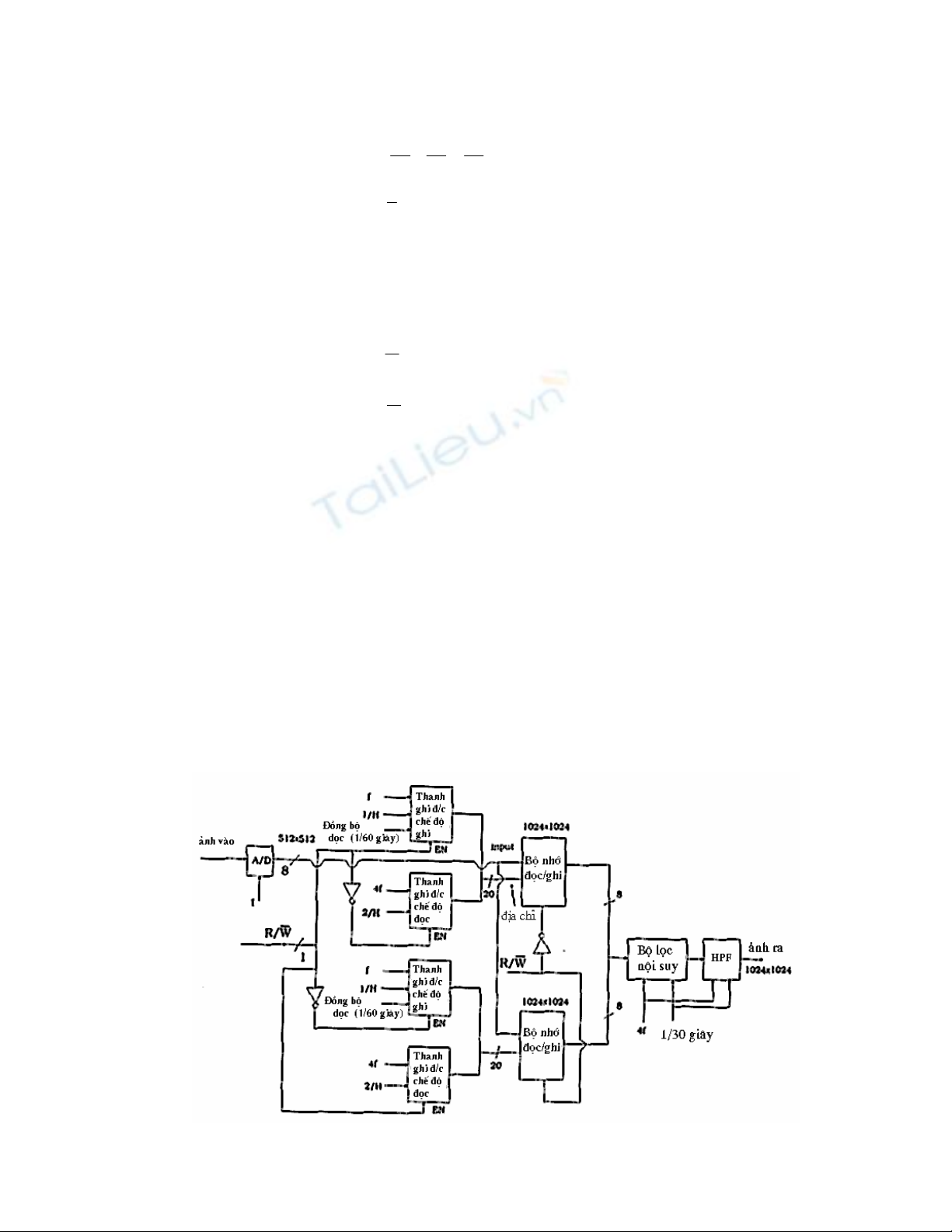

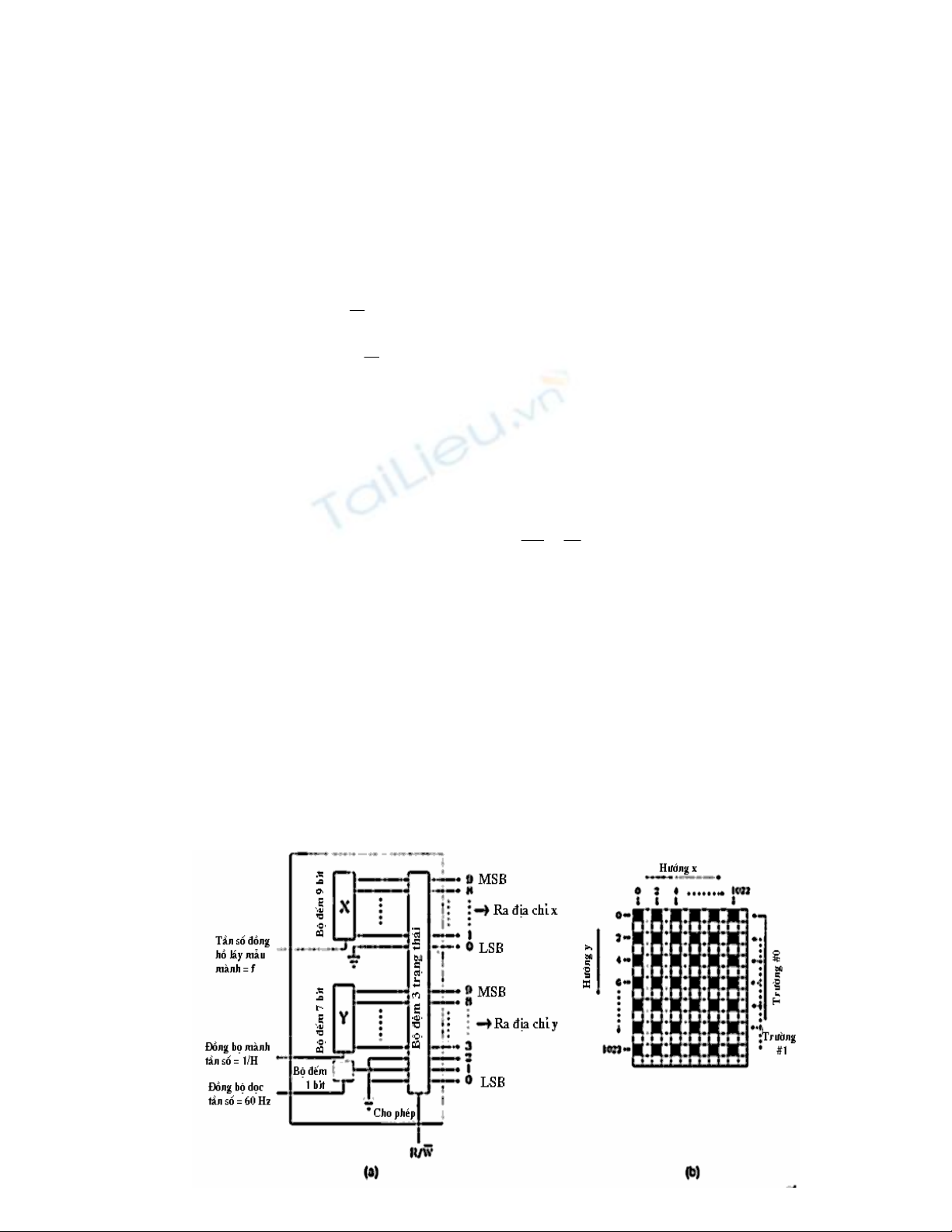

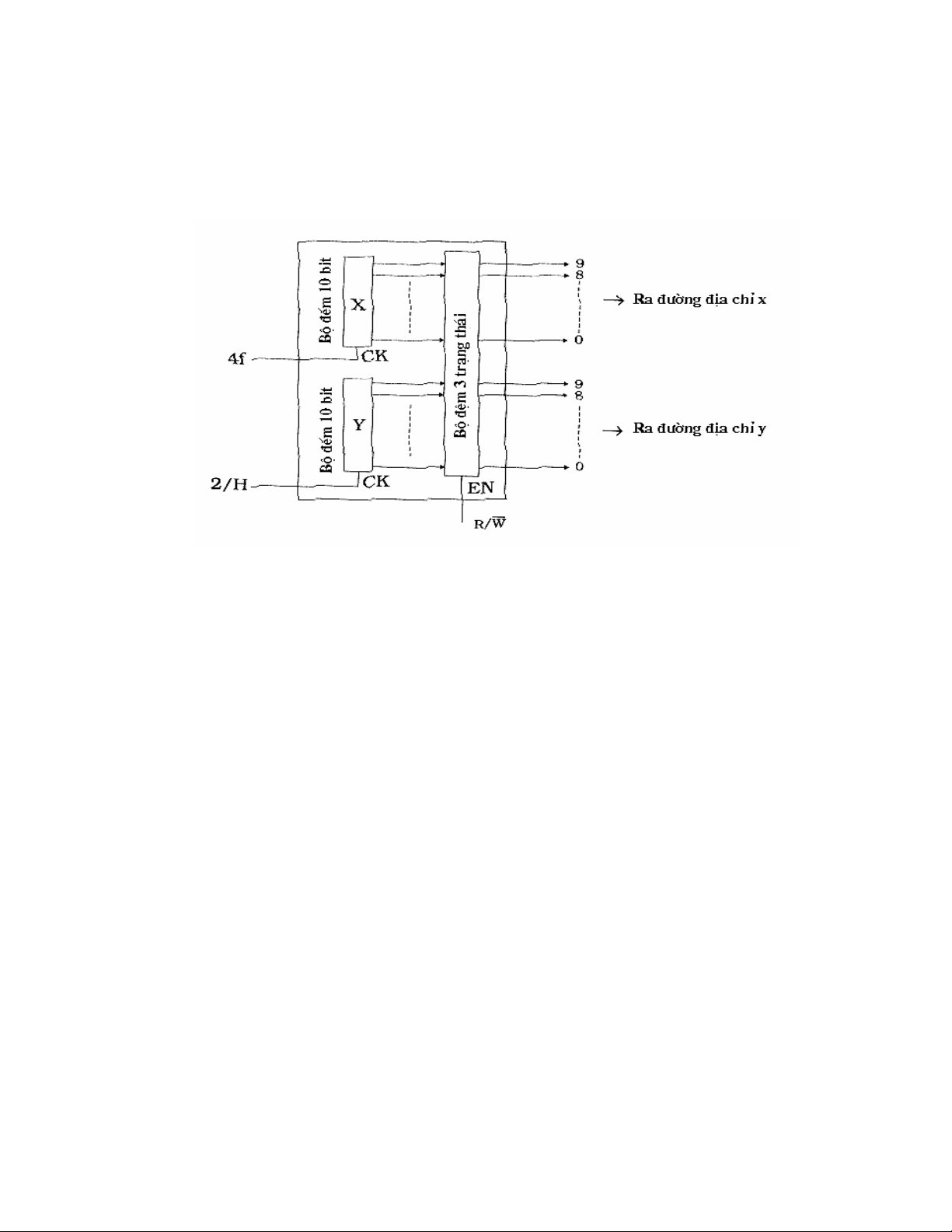

16.10 Nhân đôi số dòng quét trong máy thu TV trong EDTV thời

gian thực

Lọc 2-D thời gian thực làm độ nổi các chi tiết như trong hệ thống truyền

hình EDTV đề cập trong chương 14. Khái niệm này đòi hỏi một số dòng nhân

gấp đôi số dòng tại máy thu so với các tiêu chuẩn truyền hình thông thường.

Nó sẽ cho ta các TV các các ảnh chất lượng cao hơn mà không cần thiết chi

phí để chuyển sang hệ truyền hình HDTV. Các chuẩn HDTV có rất nhiều vấn

đề, một trong số đó là khả năng tương thích với các hệ truyền hình trước. Các

vấn đề khác của HDTV đã được đề cập trong chương 14. Nếu chúng ta giữ lại

các tiêu chuẩn truyền hình hiện nay và thiết kế các TV như HDTV, chúng ta sẽ

có được chất lượng ảnh truyền hình như trong HDTV mà không cần thay đổi

hệ truyền hình.