Bài 6 : Mạch Khuếch Đại Dùng Transistor Trường (FET

BÀI 6 : MẠCH KHUẾCH ĐẠI DÙNG

TRANSISTOR TRƯỜNG (FET)

MỤC ĐÍCH THÍ NGHIỆM

Giúp sinh viên bằng thực nghiệm khảo sát các vấn đề chính sau đây :

Phần bắt buộc :

1. Vấn đề phân cực DC : Tìm hiểu nguyên tắc khuếch đại của transistor trường (FET), sơ đồ

mắc kiểu source chung và đo hệ số khuếch đại của transistor trường

2. Khảo sát mạch khuếch đại AC của transistor trường (FET), sơ đồ mắc kiểu source chung:

Xác định Av, Khảo sát đáp ứng tần số của mạch khuếch đại, vai trò của tổng trở vào Zin….

3. Khảo sát mạch khuếch đại AC sử dụng transistor MOSFET trong các sơ đồ nối kiểu Source

chung.

4. Khảo sát mạch đóng mở dùng MOSFET.

THIẾT BỊ SỬ DỤNG

1. Bộ thí nghiệm ATS-11 và Module thí nghiệm AM-107.

2. Dao động ký, đồng hồ đo DVM và dây nối.

PHẦN I : CƠ SỞ LÝ THUYẾT

Phần này nhằm tóm lược những vấn đề lý thuyết thật cần thiết phục vụ cho bài thí

nghiệm và các câu hỏi chuẩn bị để sinh viên phải đọc kỹ và trả lời trước ở nhà.

I.1. TỔNG QUAN

Transistor gồm 2 loại: BJT và FET.

- BJT là phần tử được điều khiển bằng dòng điện (iC ∈ iB ), có tổng số trở ngõ vào nhỏ

nên có tiếng ồn thường lớn và bất lợi ở các mạch khuếch đại dùng nguồn tín hiệu có

tổng trở ra lớn.

- FET là phần tử được điều khiển bằng áp (iD ∈ vGS), có tổng trở ngõ vào lớn (

≈

100M)

nên có tiếng ồn thấp (ivào

≈

0), thích hợp các tầng khuếch đại tín hiệu nhỏ.

Các ưu điểm của FET:

- Fet ổn định hơn BJT.

- Có kích thước nhỏ hơn BJT nên khả năng thích hợp cao hơn. Nên FET ngày càng được

sử dụng rộng rãi.

Có nhiều loại FET đóng vai trò quan trọng trong kỹ thuật hiện đại trong đó có hai loại cơ

bản sau:

- Loại nối : JFET (Junction Field Effect Transistor) :

- Loại có cực cửa cách ly: MOSFET (Metal-Oxitde-Semiconductor Field Effect

Transistor). Khi nói FET ý chỉ loại JFET.

Bài 6 : Mạch Khuếch Đại Dùng Transistor Trường (FET

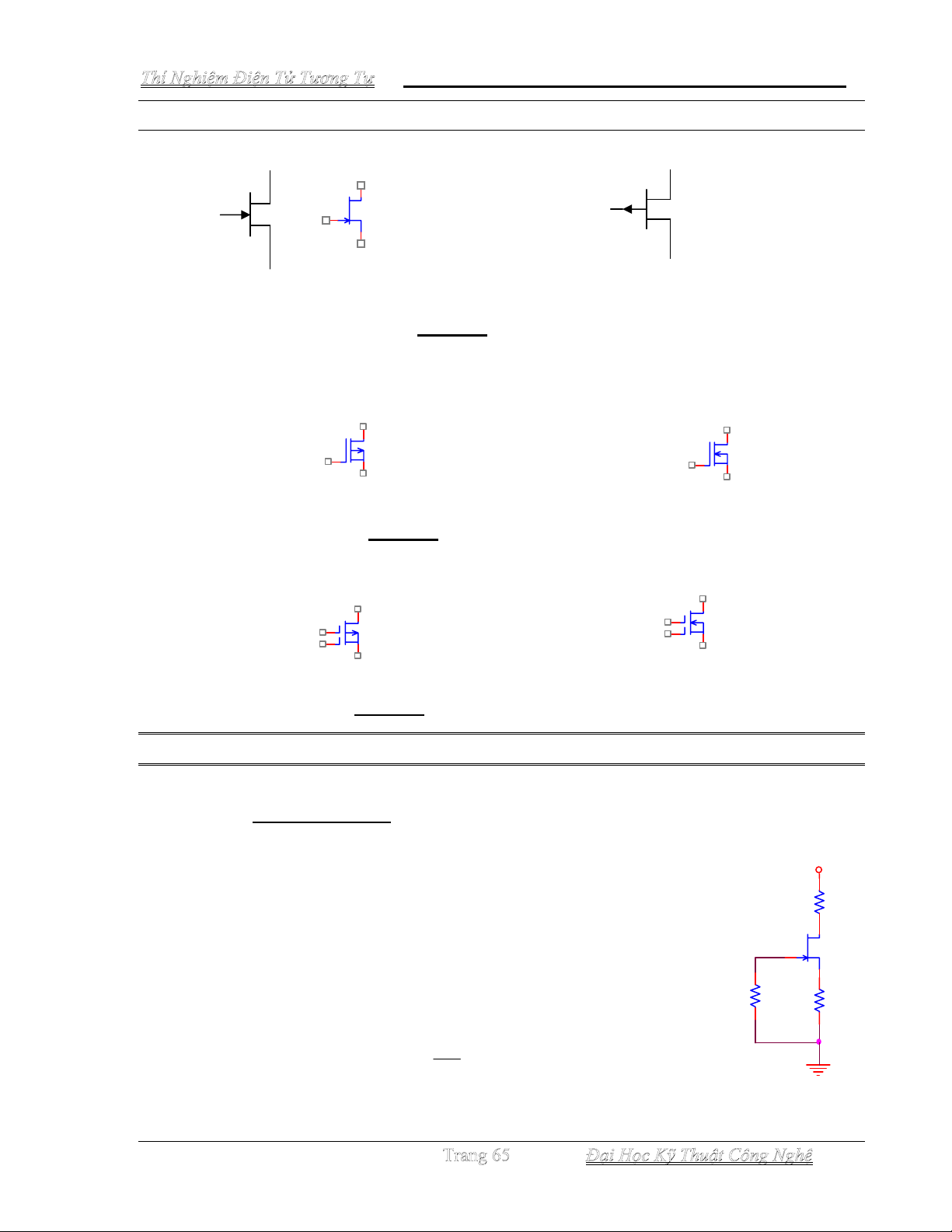

I.2. PHÂN LOẠI

1. Loại nối ( JFET: Junction Fet):

2. Loại có cửa cách điện MOSSFET ( Metal- Oxide-Semiconductor Fet) : gồm 2 loại

- MOSFET kênh có sẵn

- MOSFET kênh gián đoạn:

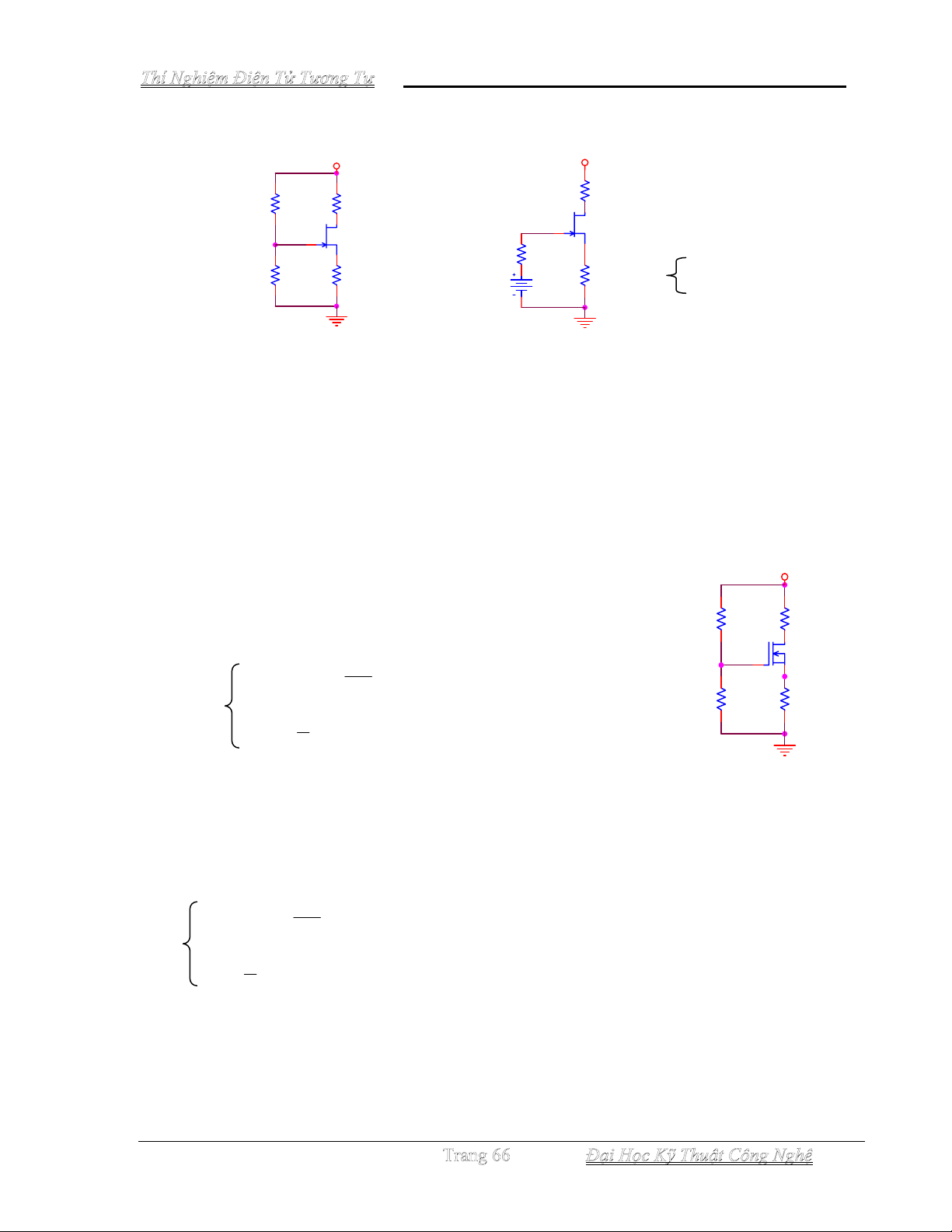

I.3. PHÂN CỰC DC

I.3.1 PHÂN CỰC FET:

a. Phân cực tự động: Trong thực tế, để tránh dùng 2 nguồn điện thế bất tiện, người

ta dùng kiểu phân cực tự động (self- bias) do điện trở R

s trong mạch cực

nguồn tạo ra.

Thật vậy, nối G xuống mass 0v qua điện trở lớn RG = 100K → 1M,

thêm Rs ta có mạch sau:

VGS = VG - VS = - ID Rs (1) (VG = 0 do G nối mass)

⇒ VGS = - Rs ID : gọi là PT đường tự động phân cực cho Fet N

và công thức Shockley : ID = IDSS(1- 2

)

p

GS

V

V (2)

Từ (1) và (2) ta suy ra: IDQ (0 < IDQ < IDSS) và VGS (VP < VGS < 0)

G

S

D

FET N

G

S

D

FET P

JFET kênh P

D

G

S

JFET kênh N

G

D

S

Hình 5-2: Ký hiệu MOSFET kênh có sẵn

Hình 5-1: Ký hiệu JFET

MOSFET kênh có sẵn loại PMOSFET kênh có sẵn loại N

MOSFET kênh gián đoạn loại N MOSFET kênh gián đoạn loại P

Hình 5-3: Ký hiệu MOSFET kênh có sẵn

FET N

RG RS

VDD

0

RD

Bài 6 : Mạch Khuếch Đại Dùng Transistor Trường (FET

RS

VGG

V DD

RGG

FET N

RD

R1

R2

RS

RD

IG-FET N

V DD

2

)(

2

γ

VV

k

IGSD −=

2

)(

2

γ

VV

k

IGSD −=

PT ngõ ra VDD = ID (Rs + RD) + VDS => VDSQ = VDD - IDQ (Rs + RD)

b. Phân cực kiểu cầu phân áp:

Ù

Cách xác định Q:

Ta có : VGS = VGG –RS.ID (1)

I

D = IDSS (1-VGS/VP)2 (2)

Từ (1) và (2) => IDQ

Phương trình ngõ ra : VDD =VDS + ID(RS + RD) (3)

=> VDSQ

I.3.2 PHÂN CỰC MOSFET:

a. Phân cực kiểu cầu phân áp:

Ta có: RG = R1//R2 , VGG = VDD.R1/(R1+R2)

Với VGS = VGG – RS ID (1)

ID = IDSS (1- 2

)

p

GS

V

V (Kênh có sẵn)

VDD = VDS + ID (RS + RD) (3)

Từ (1), (2) => VGSQ, IDQ

Từ (3) => VDSQ

b. Phân cực kiểu hồi tiếp:

Ta có: VGS = VDS (1)

ID = IDSS (1- 2

)

p

GS

V

V (Kênh có sẵn)

VDD = VDS + ID (RS + RD) (3)

Từ (1), (2) (3) => VGSQ; IDQ ; VDSQ

R1

FET N

RS

R2 RD

V DD

Với:

RG = R1//R2

VGG = (VDD. R1) /(R1+R2)

(

2

)

(Kênh gián đoạn)

(2)

(Kênh gián đoạn)

Bài 6 : Mạch Khuếch Đại Dùng Transistor Trường (FET

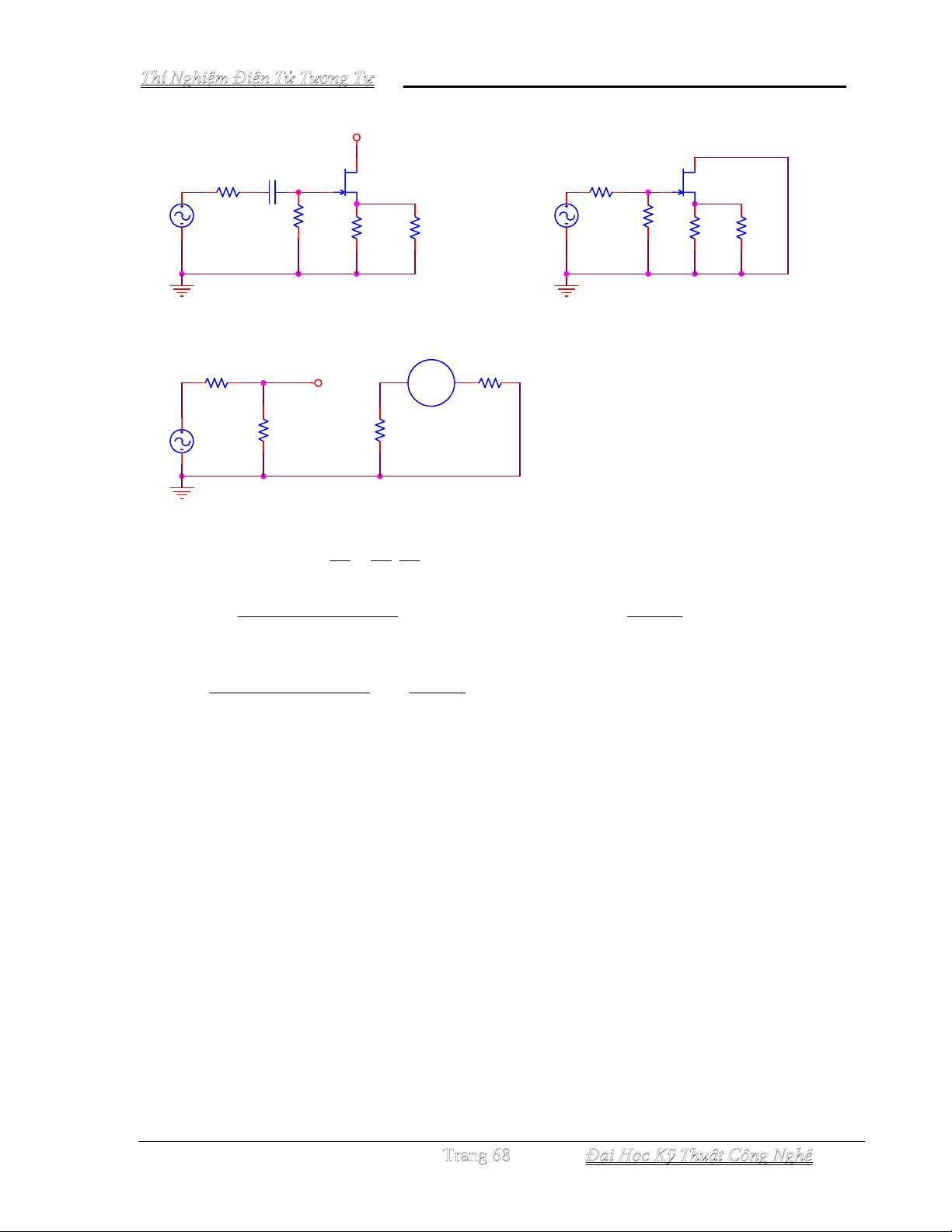

I.3. KHUẾCH ĐẠI AC

I.3.1. MẠCH NGUỒN CHUNG (SOURCE) :

ri :được thêm vào để kiểm soát dòng điện ngõ vào từ nguồn v1.

RL : biểu diễn tải được nhìn bởi bộ khuếch đại.

Rg, Rd, Rs : cung cấp phân cực DC để FET hoạt động.

Hệ số khuếch đại :

i

gs

gs

V

i

L

vv

v

vv

v

AL.==

với: )(

//

//

gs

dsLD

LD

Lv

rRR

RR

v

μ

−

+

= và i

iG

G

gs v

rR

R

v.

+

=

=> riR

R

rRR

RR

A

G

G

dsLD

LD

v++

−= .

//

//

μ

Tổng trở vào : Zi = RG

Tổng trở ra : Dds

o

o

oRr

i

v

Z//==

Zi

Zo

VL

Mạch tương đương AC Mạch khuếch đại dùng FET mắc CS

VDD

Vi

ri ri

s

+

Co

R

D

RL

D

RL

Vi

+

Cs

R

+

Ci

R

G

FET N

R

FET N

R

G

+-

Mạch tương đương tín hiệu nhỏ

rds

Vi

G

S

-

D

VL

RR

+

Vgs

RL

D

U.Vgs

G

ri

Bài 6 : Mạch Khuếch Đại Dùng Transistor Trường (FET

I.3.2. MẠCH MÁNG CHUNG (DRAIN) :

G

S

ri

R

Vi

R

VDD

FET N

Vi

FET N

R

G

RLRRL

L

+

Ci

V

L

V

ri

D

D

U.Vg

Vi

G

Vg

G

+

(Rs//RL)( u+1)

rds

L

V

R

S

ri

Hệ số khuếch đại :

i

g

g

V

i

L

vv

v

vv

v

AL.==

với: )(

)1)(//(

)1)(//(

g

dsLS

LS

Lv

rRR

RR

v

μ

μ

μ

++

+

= và i

iG

G

gv

rR

R

v.

+

=

=> )).((

)1)(//(

)1)(//(

riR

R

rRR

RR

A

G

G

dsLS

LS

v+++

+

=

μ

μ

μ

Mạch khuếch đại dùng FET mắc CD Mạch tương đương AC

Mạch tương đương tín hiệu nhỏ

+ -

![Tài liệu kỹ thuật số: Tổng hợp [Mô tả/Hướng dẫn/Kinh nghiệm...]](https://cdn.tailieu.vn/images/document/thumbnail/2016/20160711/myanh1605/135x160/2006821314.jpg)

![VirtualDJ Pro/Home v7.0.5: Tải PC [Phiên bản tốt nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130821/skinny_1/135x160/5311377078444.jpg)

![E-Learning và Adobe Present: Giới thiệu chung [Bài 1]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130721/mrphuocpro/135x160/3301374365825.jpg)