Nghiên cứu về tối ưu hóa khả năng tương thích

điện từ của thiết kế bảng mạch in tốc độ cao

Tóm tắt-Trong bài viết này trình bày ba phương pháp tối ưu hóa thiết kế nối đất được

sử dụng để giải quyết vấn đề EMI trên PCB trộn với tín hiệu analog và kỹ thuật số. Một mô

hình được xây dựng để kiểm tra bề mặt hiện tại, trường E, trường H và S-thông số của các

bảng mạch để xem xét ảnh hưởng của các phương pháp tránh vấn đề EMI và SI. Sau đó, thí

nghiệm mô phỏng trên một sản phẩm thực sự được thực hiện để hiển thị các cải thiện sau khi

áp dụng những phương pháp đó.

Từ khóa -high_speed PCB layout; EMC; EMI; spilt ground; SI

I. GIỚI THIỆU

Xu hướng gần đây trong việc sử dụng của các gia đình logic tốc độ cao mạch điện tử

nâng cao EMI (can thiệp điện từ) vấn đề của một sản phẩm PCB. Các tần số cao có thể gây

nhiễu sóng một cách dễ dàng trong một thiết kế không thích hợp chẳng hạn như chuông,

nhiễu xuyên âm, phản xạ và bức xạ. Nếu được bỏ qua, nhiễu có thể ảnh hưởng nghiêm trọng

đến hiệu suất hệ thống. Trong thiết kế PCB, các nhà thiết kế luôn luôn cho rằng mặt phẳng đất

không có gì. Nhưng có lẽ họ không biết rằng vấn đề EMI của PCB có thể là sản phẩm do lỗi

của thiết kế nối mặt phẳng đất.

Bài viết này được tổ chức như sau: Trong phần II, ba yêu cầu để giảm EMI từ in bảng

mạch với thiết kế tiếp đất. Trong phần III, bằng cách sử dụng các công cụ mô phỏng để làm

cho lý thuyết vào ví dụ cụ thể mô phỏng cho phép độc giả trực quan hơn sự hiểu biết về sự

đúng đắn của lý thuyết. Trong phần IV thí nghiệm được thực hiện trong một sản phẩm thực để

thể hiện được cải thiện do thông qua ba kỹ thuật. Cuối cùng, tạo ra một kết luận về thiết kế

nối mặt phẳng đất trong sản phẩm PCB để tránh các vấn đề EMI.

II. BA YÊU CẦU CỦA THIẾT KẾ GROUND

A. Lớp tín hiệu cần phải chặt chẽ với mặt phẳng đất

Trong các vấn đề toàn vẹn tín hiệu, chúng ta thường gọi là "Mặt phẳng đất" như đường trở

lại. Trong tần số cao, điện cảm của đường dẫn tín hiệu và đường dẫn trở lại giảm thiểu, điều

này có nghĩa rằng, miễn là các trường hợp cho phép, trả lại đường dẫn sẽ cố gắng để gần với

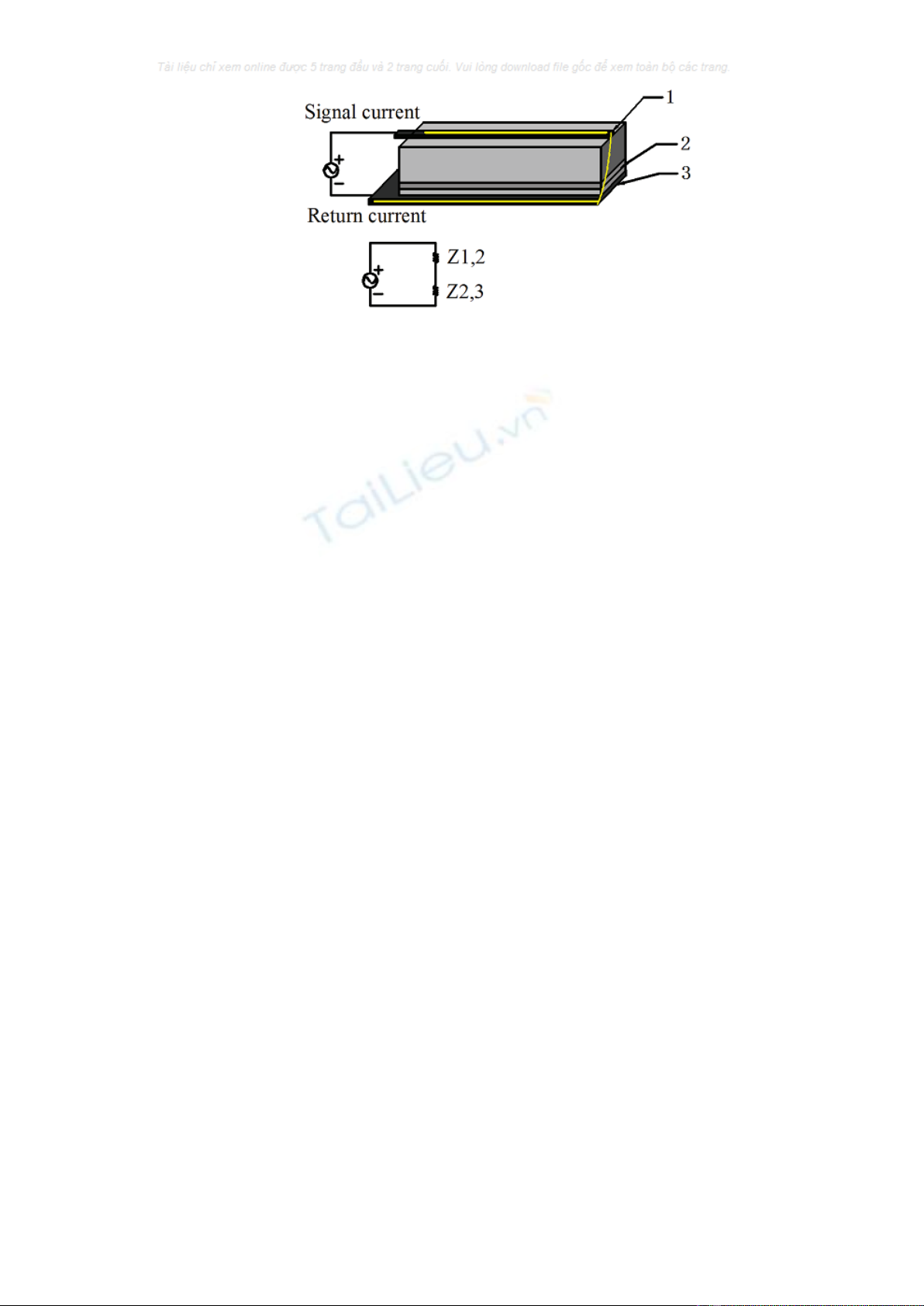

đường tín hiệu. Hình 1 Khi hiển thị, có một dòng tín hiệu trên một PCB, và đường trở lại là

nằm ở đường thứ ba. Tại thời điểm này trở kháng của tín hiệu giữa hai lớp trung bình, trở

kháng tương đương Z1,2 và Z2,3[1], Vì vậy, trở kháng các tín hiệu là:

Zdriver = Z1,2+ Z2,3

Hình 1. Mô hình vật lý của đường tín hiệu và mạch tương đương

Vì vậy, nhỏ hơn trở kháng của hai lớp, hoặc càng thấp, hoặc giá trị Zdriver càng thấp, trở kháng

của tín hiệu nhiều cách tiếp cận để Z2,1.

Do đó, chúng ta có thể kết luận rằng giảm trở kháng giữa các lớp liền kề nhất cách thức quan

trọng để giảm thiểu độ dày của mặt phẳng giữa các phương tiện truyền. Hoặc chúng ta phải

làm cho đường trở lại gần các tín hiệu.

B. Tín hiệu khác nhau thiết lập lên đất khác nhau

Bản chất khác nhau của mạch cần khác nhau tính chính xác của điện áp, trở lại con đường

khác nhau, tại cùng một thời gian, khả năng chịu đựng giới hạn nhiễu là không giống nhau.

Thông thường, tần số của mạch kỹ thuật số cao hơn nhiều, và mô phỏng độ nhạy của nhiễu

mạch là mạnh mẽ hơn, do đó phần kỹ thuật số và một phần tương tự nên được tách ra càng

nhiều càng tốt. Vì vậy, cả hai quay trở lại con đường sẽ lẫn nhau bị cô lập. Khi các bảng mạch

tồn tại như tính chất khác nhau của mạch và trộn với nhau, trong trường hợp đất được phân

vùng [2].

C. Viết qua các phân đoạn giải phóng mặt bằng là không thích hợp

Tín hiệu tương tự và tín hiệu kỹ thuật số cuối cùng sẽ đi trở lại đất, tuy nhiên, do tín hiệu kỹ

thuật số thay đổi tốc độ, do đó, sẽ có rất nhiều nhiễu tạo ra, nhưng các tín hiệu tương tự cần

một đất tham không nhiễu. Nếu không phân chia đất, nhưng trộn lẫn chúng với nhau, nhiễu

tín hiệu kỹ thuật số sẽ ảnh hưởng đến tín hiệu tương tự thông qua đất. Nhiều nhà thiết kế thừa

nhận rằng gần đây, khi họ thiết kế một PCB sản phẩm có tính đến các phân đất. Nhưng mà

không có quyền phân chia đất, vẫn còn có thể mang lại một số vấn đề EMI. Các điển hình

nhất vấn đề gây ra bởi các dòng tín hiệu trên phân khúc khe hở.

Viết qua các phân khúc giải phóng mặt bằng có thể gây ra những câu dưới đây:

Kết quả trở kháng đường dây gián đoạn;

Tạo nhiễu xuyên âm;

Có thể gây ra phản xạ tín hiệu;

Tăng khu vực vòng lặp hiện tại, các vòng lặp điện cảm, và làm cho dạng sóng đầu ra

dễ bị dao động;

Tăng bức xạ, và dễ bị tổn thương. tác động của không gian từ;

Hãy nối từ trường khác mạch một cách dễ dàng;

Tần số cao giảm điện áp của vòng lặp điện cảm thành phần của chế độ phổ biến bức

xạ, và thông qua một cáp bên ngoài sinh ra phổ biến chế độ bức xạ.

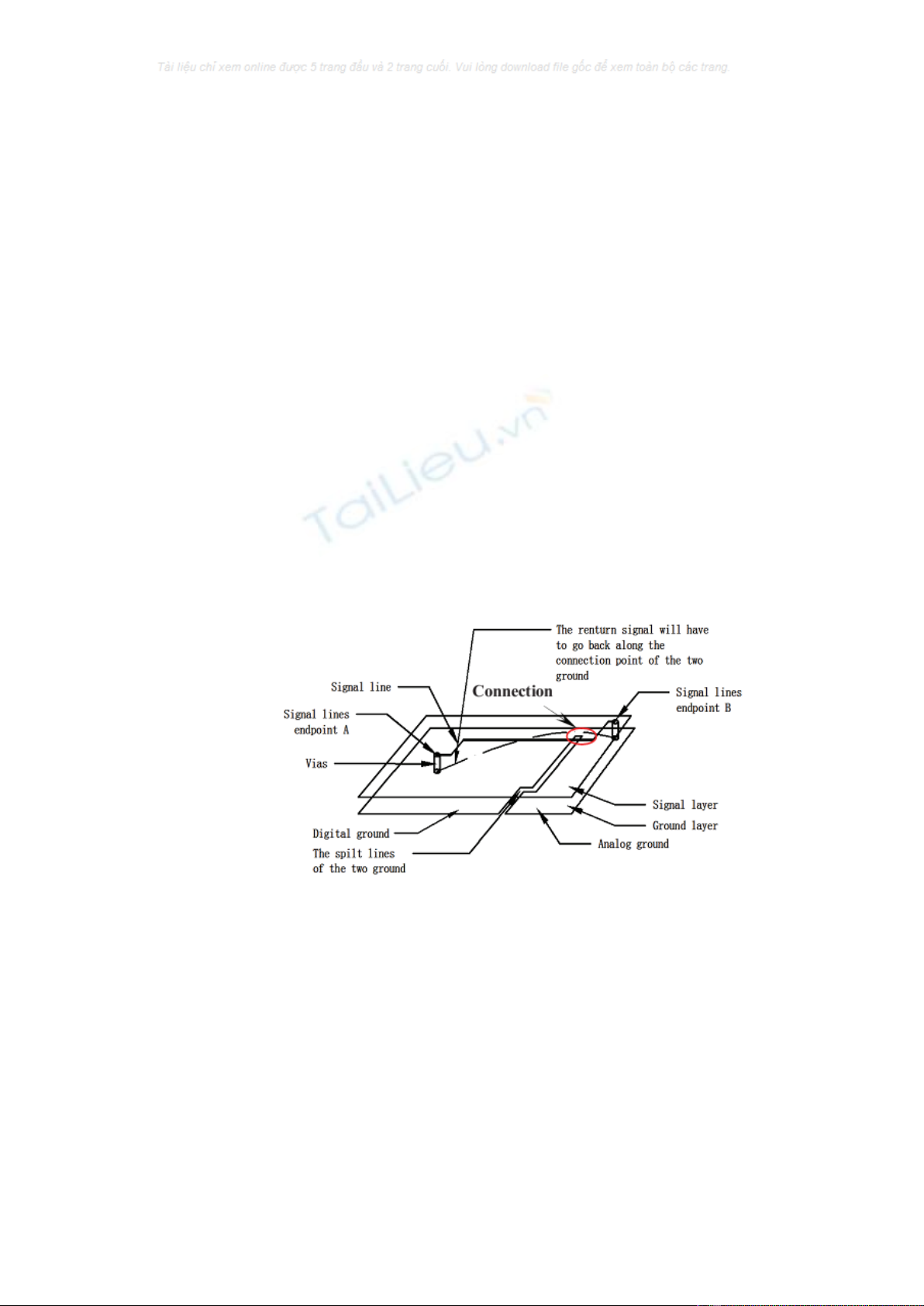

Khi chúng tôi thiết kế một mạch tín hiệu hỗn hợp, chúng tôi không thể cho phép tương tự mặt

phẳng đất và các sản phẩm kỹ thuật số mặt đất chồng chéo [1]. Nếu không, cả hai sẽ gây ra

tiếng ồn và can thiệp vì các khớp nối điện dung [3]. Như hình 2 hiển thị, nếu có một dòng trên

sự hình thành không thể thiếu, vì vậy, vấn đề là những gì? Nếu chúng ta sử dụng các phân

khúc phương pháp như hình dưới đây, giả sử chúng ta chia đất vào kỹ thuật số mặt đất

(DGND) và mặt đất tương tự (AGND), và giả sử rằng hai phần của liên kết đất cùng nhau tại

một điểm không chắc chắn, con đường trở lại tín hiệu hình dưới đây, không dưới đường tín

hiệu, nhưng quay trở lại một mình điểm kết nối và tạo thành một vòng lặp lớn.

Như chúng ta biết, dòng chảy qua các đa dẫn bề mặt sẽ sản xuất chế độ phổ biến EMI, kết quả

đầu ra hiện tại của dòng chảy các thành phần mạch vào tải trọng sẽ tạo ra sự khác biệt giữa

chế độ EMI [4].

Chế độ khác biệt giữa bức xạ được tính như [5]:

Trong công thức này:

Ip --- Hai lớp trở kháng

f --- Tần số hiện tại

Ls --- Khu vực vòng lặp

d --- Khoảng cách đo ăng-ten để cáp

Từ công thức trên, nó là bức xạ cường độ tỷ lệ thuận với khu vực vòng lặp, có nghĩa

là, lớn của con đường trở lại, lớn hơn của bức xạ. Từ phân tích, chúng ta có thể kết luận rằng

vì sự tín hiệu trên các phân khúc giải phóng mặt bằng dẫn đến tín hiệu hiện tại không thể

được trở về nguồn thông qua tối thiểu vòng lặp, và các năng lượng bức xạ điện từ bằng cách

chế độ khác biệt và vì tín hiệu hiện tại chảy ngược trở kháng trở nên rất lớn [6] [7]. Vì vậy,

tiếng ồn hiện tại trên mặt đất cũng có thể trở nên lớn và chế độ bức xạ phổ biến phát sinh từ

các điện áp khác biệt lớn trên mặt đất là cũng rất mạnh mẽ. Nếu có một số đường tín hiệu phải

trên hai loại đất, nhà thiết kế kết nối mặt đất với một điểm duy nhất theo tín hiệu, để làm cho

con đường trở lại ngắn nhất [8].

III. MODEL xác nhận

Để xác minh sự đúng đắn của lý thuyết, bài viết này sử dụng các phần mềm mô phỏng

để xác minh các điểm trên. Ở đây chúng tôi sử dụng SIwave và HFSS để mô phỏng.

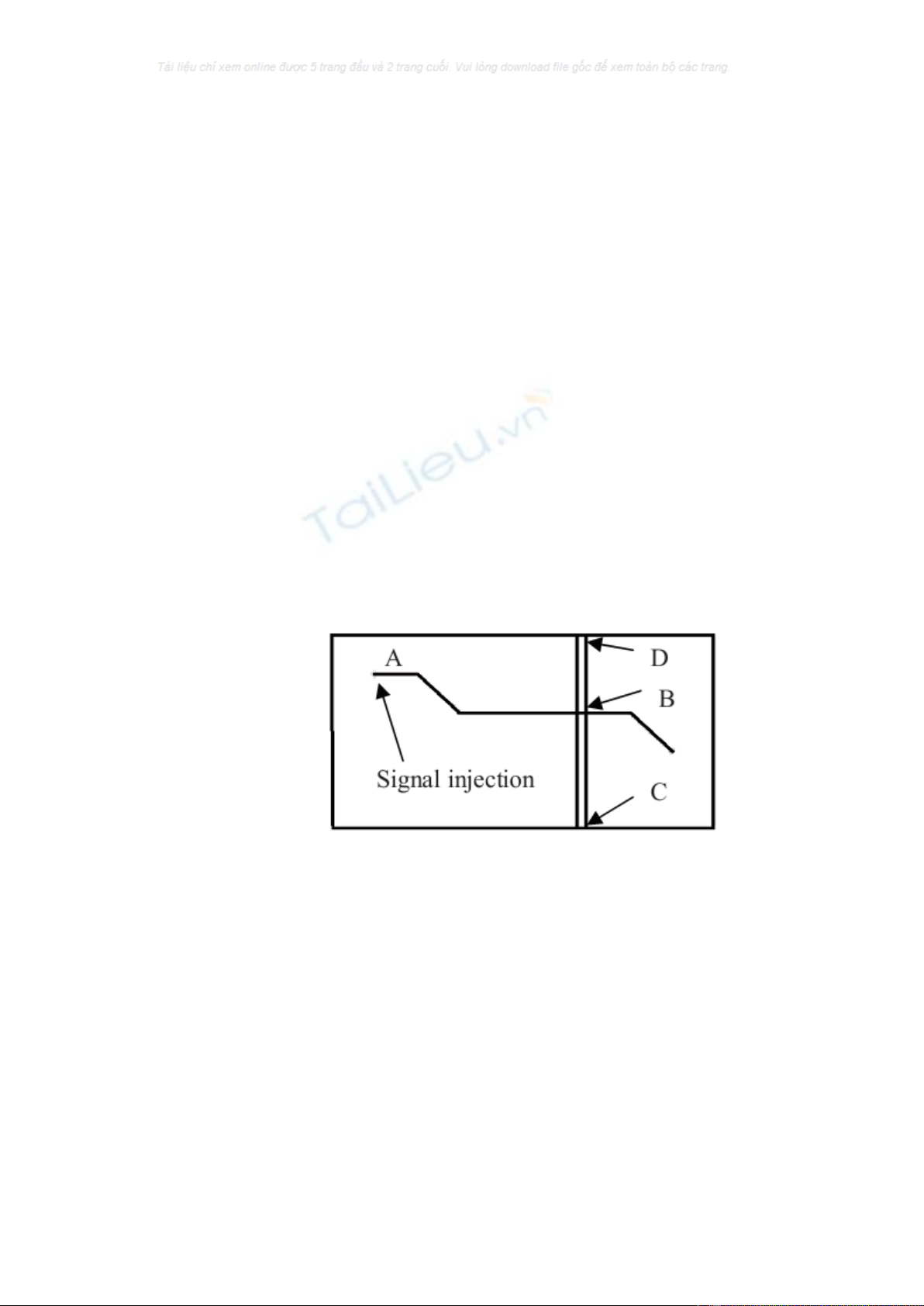

Bài viết này thiết lập một bảng mạch hai lớp PCB. Như thể hiện trong hình. 3, giả sử rằng có

một đường tín hiệu từ trên AGND DGND ở trên. Từ 0.135mm máy bay mặt đất và cung cấp

cho một dòng điện đến đường dây này tại điểm A và quan sát bề mặt hiện hành, phân phối

của cánh đồng gần E, H và cách ly trên toàn bộ hội đồng quản trị.

Bài viết này kết nối AGND và DGND ở vị trí khác nhau, như hình 3 cho thấy, B nằm ngay

bên dưới đường tín hiệu, C nằm ở dưới cùng của cạnh của phân khúc giải phóng mặt bằng, D

nằm ở trên một phần của các cạnh của phân khúc giải phóng mặt bằng. Phân tích hiện tại bề

mặt, các lĩnh vực gần S_ các thông số về ba điều kiện.

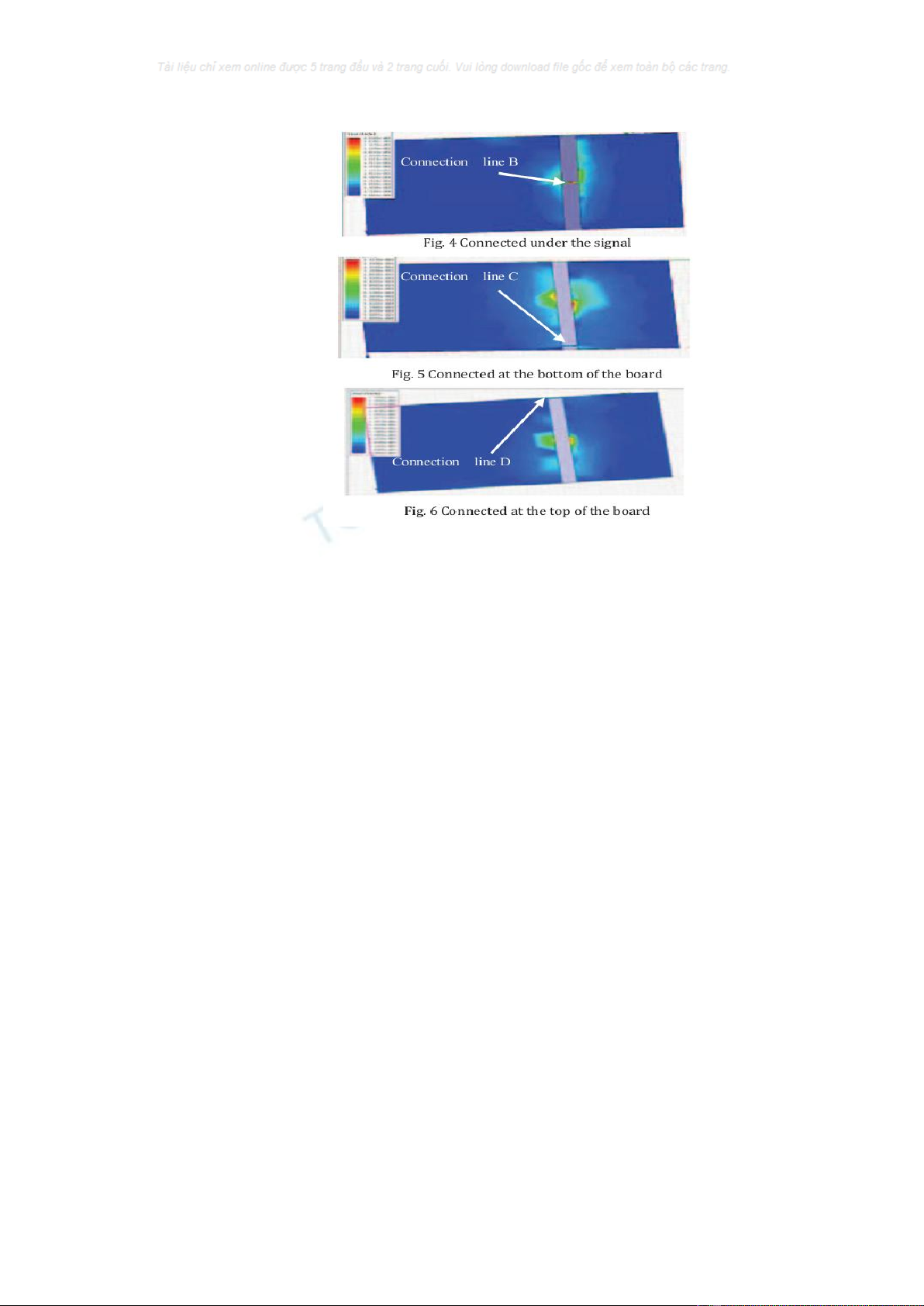

A. Bề mặt hiện tại

Chúng tôi phân tích bề mặt hiện tại trong HFSS, Hình 4, Fig.5 và Fig.6 là kết quả mô

phỏng về hiện tại bề mặt của kết nối của B, C, và D. các số liệu so sánh như sau:

Tương phản có thể được tìm thấy, bề mặt hiện tại phân phối về C và D là lớn hơn so

với B. Trên kết nối đường dây, C và D cũng sản xuất bề mặt lớn hơn không phân phối. Nhưng

chúng ta có thể biết từ Hình 4 mà khi điểm nằm ở B, bề mặt hiện tại phân phối là tập trung,

chủ yếu dưới đường tín hiệu, vì vậy bức xạ nhỏ hơn khác hai.

B. Gần trường

Bài viết này sử dụng SIwave để có được cánh đồng gần kết quả phân tích lĩnh vực điện từ,

bởi vì mối quan hệ phức tạp về điện trường và từ trường gần trường. E và H không xác định

mối quan hệ. Vì vậy, chúng tôi mô phỏng nhau.