N i dungộ:

Gi i thi u h vi đi u khi n 8051ớ ệ ọ ề ể

Các chân tín hi uệ

C u trúc port xu t nh p ấ ấ ậ

T ch c b nhổ ứ ộ ớ

T ng quan v h 8051ổ ề ọ

MCS-51 là m t h vi đi u khi n do Intel phát tri n và s n ộ ọ ề ể ể ả

xu t đ u tiên vào năm 1980ấ ầ

M t s nhà s n xu t đ c phép cung c p các IC t ng thích ộ ố ả ấ ượ ấ ươ

v i các s n ph m MCS-51 c a Intel là Siemens, ớ ả ẩ ủ

Fujitsu,Philips,Atmel…

H MCS-51 g m nhi u vi đi u khi n khác nhau, b vi đi u ọ ồ ề ề ể ộ ề

khi n đ u tiên là 8051 có 4KB ROM, 128 Byte RAM và 8031, ể ầ

không có ROM n i, ph i s d ng b nh ngoàiộ ả ử ụ ộ ớ

Trong đó 8051 là đ i di n tiêu bi u cho h vi đi u khi n ạ ệ ể ọ ề ể

MCS-51

Đ c tr ng c a chip 8051ặ ư ủ

4 KB EPROM bên trong

128 Byte RAM n iộ

4 Port xu t /nh p I/O 8 bitấ ậ

M ch giao ti p n i ti pạ ế ố ế

64 KB không gian nh mã ngoàiớ

64 KB không gian nh d li u ngoàiớ ữ ệ

X lý Boolean (ho t đ ng trên bit đ n).ử ạ ộ ơ

210 v trí nh có th đ nh v bitị ớ ể ị ị

4µs cho ho t đ ng nhân ho c chiaạ ộ ặ

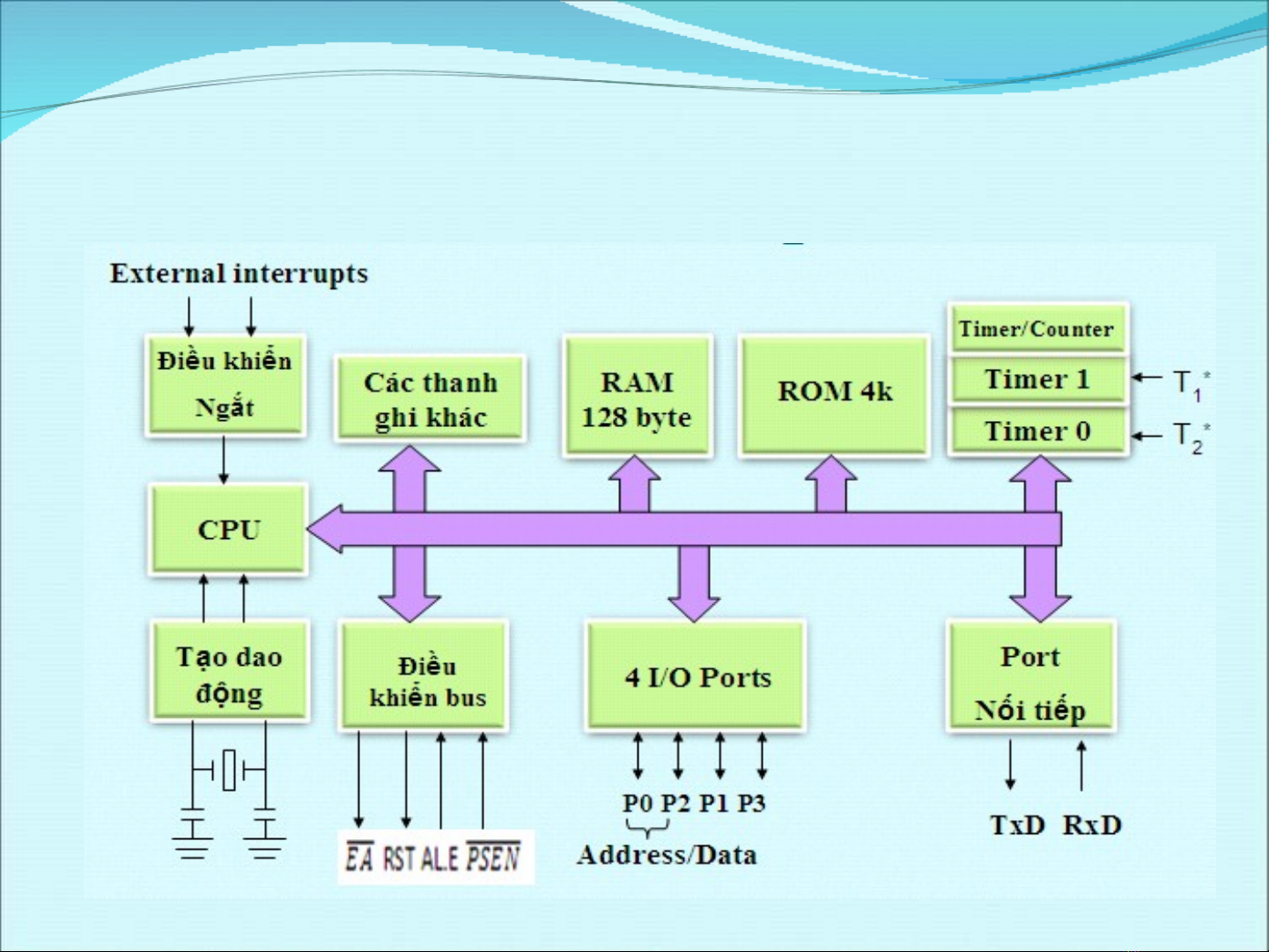

S đ kh i c a chip 8051ơ ồ ố ủ