DANH SÁCH BÀI TẬP CHƯƠNG

CHƯƠNG I: CÔNG NGHỆ ASIC VÀ FPGA

1. Phát biểu của định luật Moore.

2. Mạch tích hợp là gì, các lớp của một vi mạch được sắp xếp và chế tạo như thế nào

3. Các cấp độ tích hợp của mạch tích hợp và của chúng, các loại đóng vỏ.

4. Phân biệt TTL và CMOS.

5. ASIC là gì, phân loại ASIC theo mức độ chuyên dùng

6. Đặc điểm của Gate Arrays và Standard cells

7. Cấu trúc của PLA, sự khác biệt giữa PAL và PLA

8. Cấu trúc chung của FPGA, sự khác biệt giữa FPGA và CPLD

9. Có thể tự thiết kế một CPU trên FPGA được không? Vì sao?

10. Tại sao gọi lập trình FPGA là lập trình phần cứng.

CHƯƠNG II:

HỌ XILINX SPARTAN-3E FPGA

1. Đặc điểm của các họ Spartan-3E FPGA

2. Kiến trúc chung của Xilinx Spartan-3E FPGA

3. Cấu trúc của một ô logic

4. Các tài nguyên trong mảnh SLICEM và SLICEL

5. Cấu trúc của LUT

6. Cấu hình các LUT như RAM phân tán như thế nào

7. Đặc điểm của bảng phát triển Spartan-3E FPGA

8. Đặc điểm của chip Xilinx XC3S1600E-4FGG484 FPGA

9. Bộ Kit phát triển Spartan-3E gồm những gì

10. Sơ đồ khối và các chức năng của bộ xử lý mềm MicroBlaze 32-bit

CHƯƠNG III: NGÔN NGỮ MÔ TẢ PHẦN CỨNG VHDL

1.

Xác định tính kích thước (scalar, 1D, 2D, hoặc 1Dx1D) của các tín hiệu đã cho. Hãy viết ví

dụ số cho từng tín hiệu.

2.

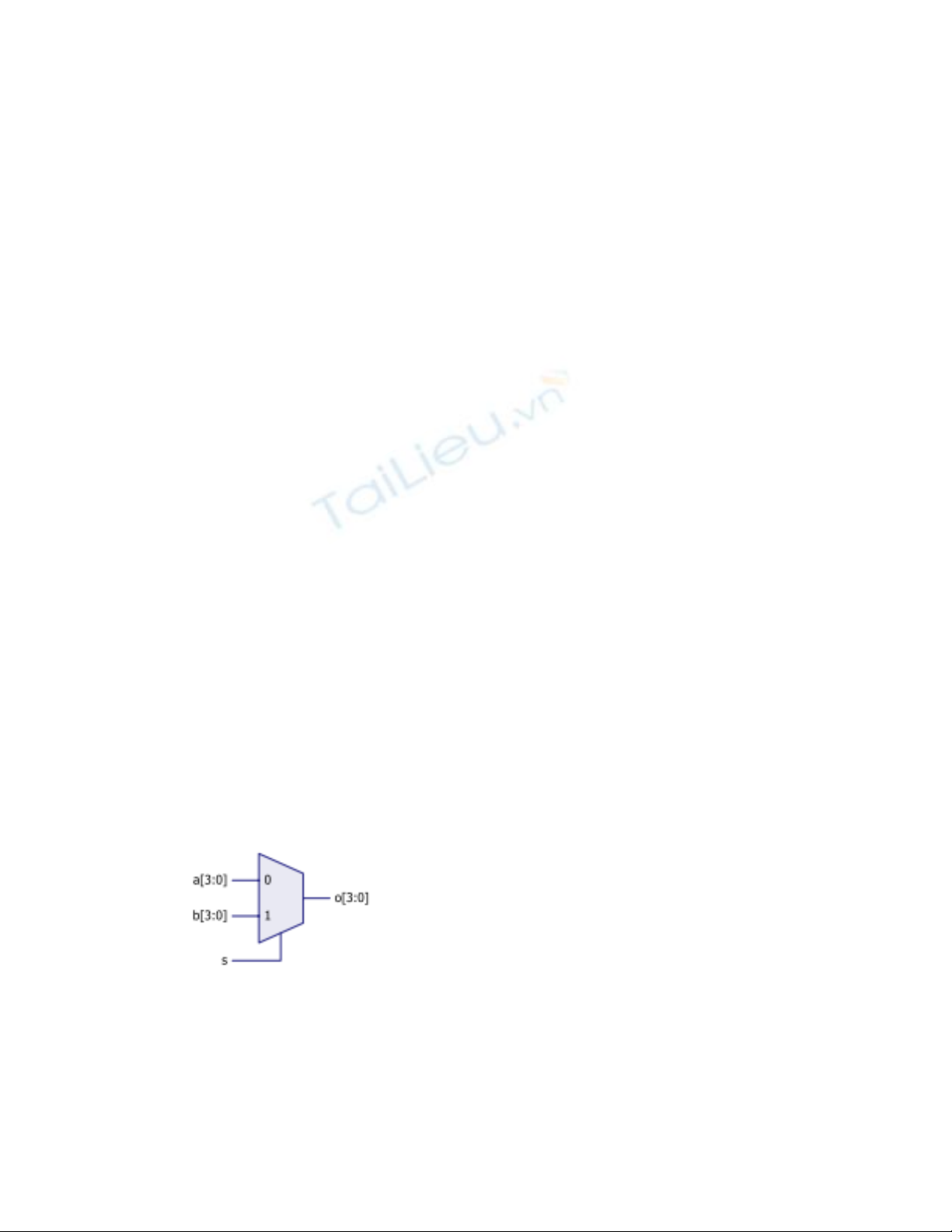

Cho bộ dồn kênh ở hình 3.120 dưới đây

Hãy điền vào những chỗ trống của mã VHDL sau đây:

LIBRARY ……..;

USE ……………..all;

ENTITY mux IS

PORT (a, b : in ………….…. (3 downto 0);

s : in …………………….…..;

o : in ………….…..(3 downto 0));

END ….;

ARCHITECTURE behavior OF mux IS

BEGIN

o <= a WHEN s = ‘0’ ELSE b;

END behavior;

3.

Cho bộ cổng nửa (Half adder) ở hình 3.121 sau đây:

Hãy điền vào những chỗ trống của mã VHDL sau đây:

LIBRARY ……..;

USE ……………..all;

ENTITY half_adder IS

PORT (a : in …………. ;

b : in ……….…..;

s : out ……..…..;

co : out ………....);

END ………….;

ARCHITECTURE rtl OF ……….. IS

BEGIN

s <= a xor b; co <= a and b;

END rtl;

4.

Cho bộ cộng đầy đủ (full adder) ở hình 3.122. Hãy điền vào những chỗ trống của mã VHDL

sau đây cho phương án song song: tất cả các câu lệnh được xử lý song song, thứ tự các câu lệnh không

theo qui tắc, chỉ sử dụng một lệnh phép gán tín hiệu. Phương án tuần tự: tất cả các câu lệnh được xử lý

tuần tự, danh sách nhạy (a, b, ci), được dùng một số câu lệnh gán biến, thứ tự các câu lệnh có liên quan,

các biến được cập nhật ngay, các tín hiệu được cập nhật ở kết thúc PROCESS. Hiền vào những chỗ trống

ở mã VHDL của bộ cộng.

LIBRARY ……..;

USE ……………..all;

ENTITY full_adder IS

PORT (…. : in …………. ;

…. : out ……..……).;

END ………….;

--------Phương án song song-------------------

ARCHITECTURE behavior_par OF …….…….. IS

…………… s1, s2, c1, c2 :…………………..;

BEGIN -- behavior

--Half adder 1

s1 <= …………; c1 <= …….………..;

--Half adder 2

s2 <=………….; c2 <=………..………;

END …………….;

-------Phương án tuần tự-------------------------

ARCHITECTURE behavior_seq OF …….…….. IS

………….. s_tmp, c_tmp :………………..;

BEGIN -- bổ xung process

--Half adder 1

s_tmp := …………; c_tmp :.…………..;

--Half adder 2

c_tmp := c_tmp or (s_tmp and ci);

s_tmp :=s_tmp xor ci;

--drive signals

s <= s_tmp; co <= c_tmp;

END ………….;

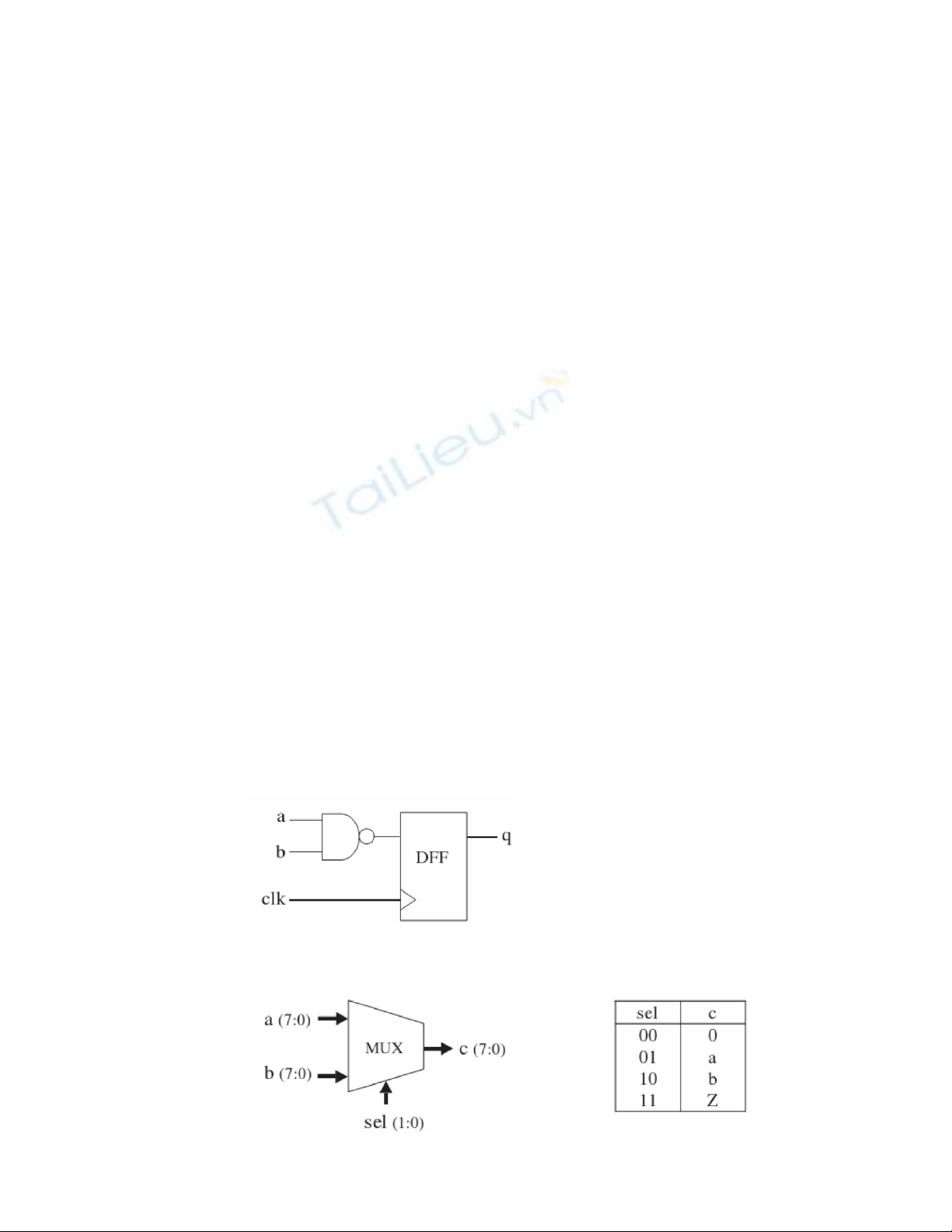

5. Thiết kế mạch sau:

6. Thiết kế mạch sau:

7. Thiết kế mạch sau:

8. Thiết kế mạch sau:

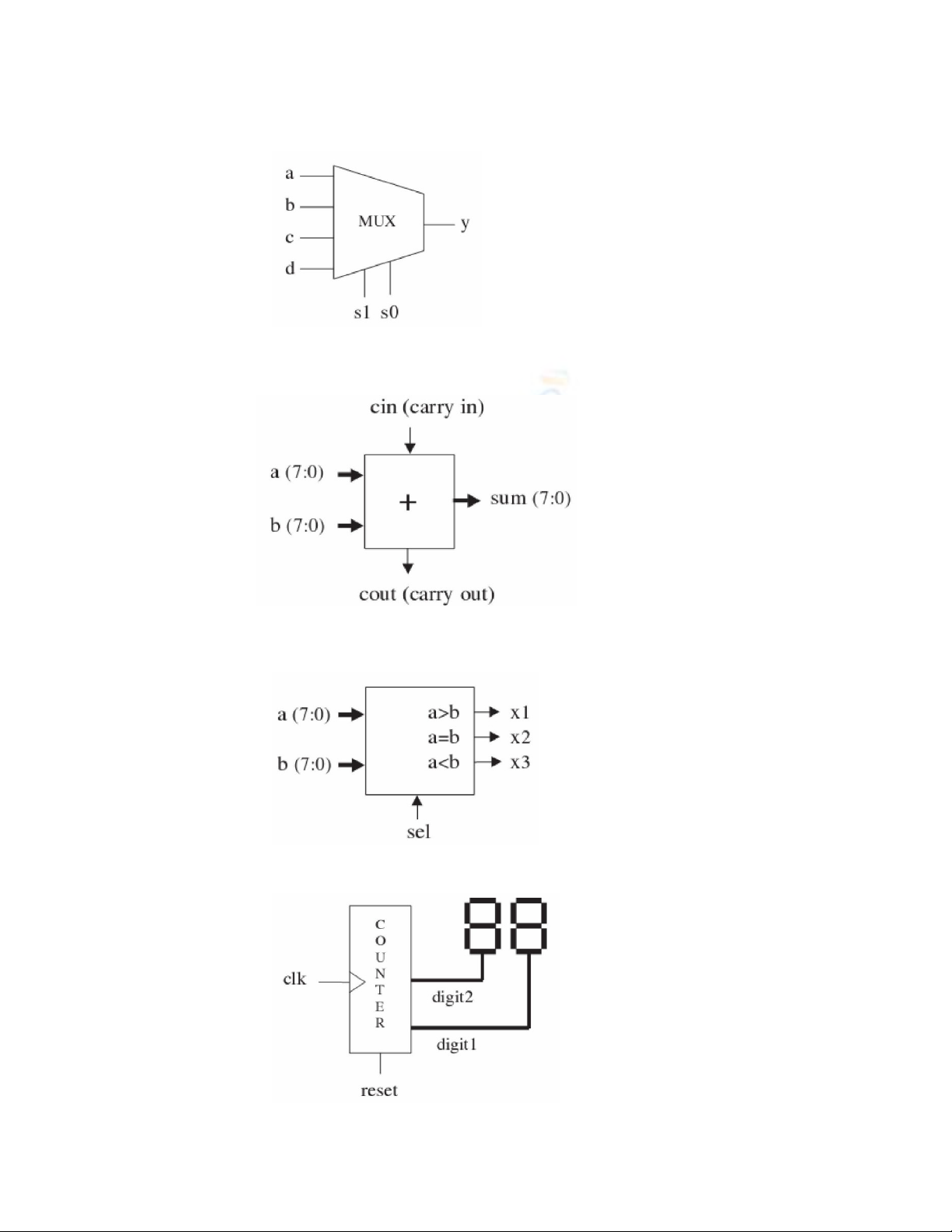

9. Thiết kế mạch sau:

10. Thiết kế mạch sau:

CHƯƠNG IV: LẬP TRÌNH FPGA VỚI BẢNG PHÁT TRIỂN SPARTAN-3E

1. Thiết kế mạch cộng BCD và hiển thị LED bảy đoạn:

a) Thiết kế mạch chuyển đổi nhị phân 4 bit sang BCD (2 digit, nhưng chỉ cần 5 bit).

b) Thiết kế mạch chuyển đổi nhị phân 8 bit sang BCD (2 digit).

c) Thiết kế mạch cộng song song 2 số BCD (1 digit).

d) Sử dụng các thiết kế ở a. và b. để làm các component cho mạch cộng 2 số BCD 2

digit, kết quả ra là 2 digit 1/2 (2 digit rưỡi).

e) Thiết kế mạch hiển thị BCD ra bảy đoạn.

f) Ráp lại các phần c) và d) thành 1 mạch hoàn chỉnh để cộng 2 số nhị phân vào và ho

ra kết quả BCD.

2. Thiết kế bộ đếm Johnson 4 bit:

a) Viết mã VHDL cho JK flifpflop kích cạnh lên.

b) Dùng a. để thiết kế mạch đếm Johnson 4 bit.

c) Viết trực tiếp không sử dụng a)

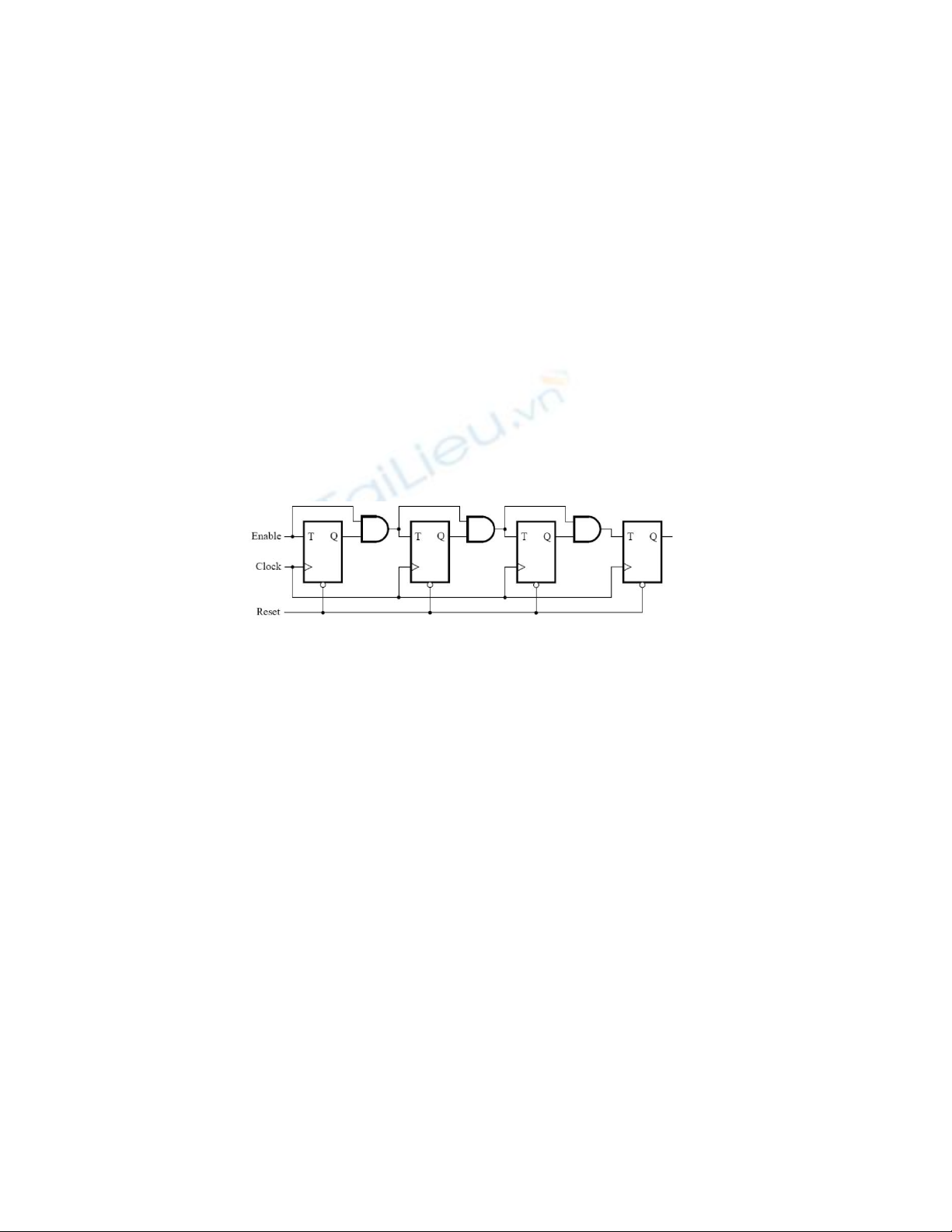

3. Cho trước mạch đếm sau:

a) Hãy tìm chuỗi đếm của mạch đếm này.

b) Viết mã VHDL cho mạch trên.

c) Dùng b. để thiết kế mạch đếm 16 bit có chức năng tương tự như mạch đếm 4 bit.

d) Có thể viết tổng quát thành mạch đếm N bit theo chức năng tương tự của a? Nếu

được hãy viết mã VHDL cho nó.

4.

Thiết kế mạch điều khiển đèn 8 LED đơn với yêu cầu như sau: điểm sáng chạy từ phái

sang trái và từ trái sang phải theo xung clock và có 1 chân cho phép E tích cực mức 0.

5.

Thiết kế mạch có chức năng giống IC4017.

6.

Thiết kế mạch có chức năng giống IC4017 nhưng gồm có 20 ngõ ra.

7.

Thiết kế mạch đếm nhị phân 4 bit – đếm lên, đếm xuống dượcđiều khiển bằng tín hiệu

UD ( UD = 0 thì đếm lên, UD = 1 thì đếm xuống ), có một tín hiệu CLK, một tín hiệu

CLR, có thêm chức năng đặt trước số đếm như IC 74193.

8.

Thiết kế mạch đếm BCD từ 000 đến 999 – đếm lên, đếm xuống dượcđiều khiển bằng

tín hiệu UD ( UD = 0 thì đếm lên, UD = 1 thì đếm xuống ), có một tín hiệu CLK, một

tín hiệu CLR, có giải mã hiển thị ra 3 LED 7 đoạn – dùng quét.

9.

Mô tả mạch có 3 nút nhấn A, B, C: Khi nhấn nút A thì mạch tạo ra 5 xung rồi ngừng,

khi nhấn nút B thì mạch tạo ra 10 xung rồi ngừng, khi nhấn nút C thì mạch tạo ra 15

xung rồi ngừng. Cho xung clock ngõ vào có tần số bằng 1Hz.

10.

Thiết kế mạch có 8 ngõ ra và ccs ngõ vào gồm: 1 clk, 1 clr, 1 ngõ vào S: S = 0 thì mạch