VHDL-BTOT-trang 1/11

HBK Tp HCM

Khoa in-T

BMT

Bài tp ôn VHDL

1. Tìm dng ti thiu hóa theo SOP ca

a. f(x

1

, x

2

, x

3

) = Σm (3, 4, 6, 7)

b. f(x

1

, x

2

, x

3

) = Σm (1, 3, 4, 6, 7)

Kim tra li kt qu tính tay bng cách nhp các hàm trên cha rút gn

thông qua biu din bng chân tr trong MAX+plus II bng Waveform

Editor và compile nó. Ta c c kt qu rút gn trong file .rpt .

2. Tìm dng ti thiu hóa theo POS ca

c. f(x

1

, x

2

, x

3

) = Π M(0, 2, 5)

d. f(x

1

, x

2

, x

3

) = Π M(0, 1, 5, 7)

Kim tra li kt qu tính tay bng cách nhp các hàm trên cha rút gn

thông qua biu din bng chân tr trong MAX+plus II bng Waveform

Editor và compile nó. Ta c c kt qu rút gn trong file .rpt .

3. Cho các bin vào X=x

1

x

0

và Y=y

1

y

0

, ra ca h t hp là hàm f c

nh ngha f(X,Y) = 1 nu X khác Y; f(X,Y)=0 nu X=Y. Tìm dng ti

thiu ca f theo SOP.

4. Dùng Graphic Editor v mch thc hin các hàm sau

a. f

1

= x

2

x

3

x

4

+ x

1

x

2

x

4

+ x

1

x

2

x

3

+ x

1

x

2

x

3

b. f

2

= x

2

x

4

+ x

1

x

2

+ x

2

x

3

Hãy s dng mô phng chc nng/hàm chng t rng f

1

= f

2

.

5. Tơng t 4. vi các hàm sau

a. f

1

= (x

1

+ x

2

+ x

4

) ( x

2

+ x

3

+ x

4

) (x

1

+ x

3

+ x

4

) (x

1

+ x

3

+ x

4

)

b. f

2

= (x

2

+ x

4

) (x

3

+ x

4

) (x

1

+ x

4

)

Hãy s dng mô phng chc nng/hàm chng t rng f

1

= f

2

.

6. Dùng Text Editor vit bng VHDL các hàm:

7. a) Xét các phát biu gán sau

f1 <= ((x1 AND x3) OR (NOT x1 AND NOT x3)) AND ((x2 AND

x4) OR

(NOT x2 AND NOT x4));

f2 <=(x1 AND x2 AND x3 AND NOT x4) OR

(NOT x1 AND NOT x2 AND x3 AND x4) OR

(x1 AND NOT x2 AND NOT x3 AND x4) OR

(NOT x1 AND x2 AND x3 AND NOT x4);

a. Vit mã VHDL y cho các hàm f1, f2 trên.

b. S dng mô phng chng t rng f1 = f2.

VHDL-BTOT-trang 2/11

b) Trong các danh hiu sau hãy tìm ra các danh hiu hp l và không

hp l. Vi các danh hiu không hp l, hãy gii thích ti saovi cách

vit ó không hp l?

Addr32bit 32bit_addr CaRryOut? Time_Co out reset_

_rst CaRryOut out1 reset& 74HC00_102 and

c) on mã sau có các li. Hãy tìm ra và gii thích?

Library ieee -- line 1

USE ieee_std_logic_1164.all -- line 2

-- line 3

ENTITY encoder42 IS -- line 4

PORT IS (w : IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- line 5

y : OUT STD_LOGIC_VECTOR(1 DOWNTO 0); -- line 6

z : OUT STD_LOGIC); -- line 7

END encoder; -- line 8

-- line 9

ARCHITECTURE Behavior OF encoder42 IS -- line 10

BEGIN -- line 11

y <= "11" WHEN w(3) = '1' ELSE; -- line 12

"10" WHEN w(2) = '1' ELSE; -- line 13

"01" WHEN w(1) = '1' ELSE; -- line 14

"00"; -- line 15

z <='0' WHEN w = "0000" ELSE '1'; -- line 16

END Behavior; -- line 17

d) Hãy cho bit nhng lnh nào sau ây có cú pháp và ng ngha úng

mô t cho hàm f = x’y + xy’

a. f <= ( x AND NOT y ) OR ( NOT x AND y ) ;

b. f <= ( NOT x AND NOT y ) OR x ;

c. f <= NOT x AND y OR x AND NOT y ;

d. f <= ( NOT x OR y ) AND NOT y ;

e. f <= (NOT x AND y) OR (x AND NOT y) ;

8. Tìm ti thiu hóa dng SOP và POS cho các hàm sau:

f(x

1

, x

2

, x

3

) = Σm (1, 2, 3, 5)

f(x

1

, x

2

, x

3

) = Σm (1, 4, 7) + d(2,5)

f(x

1

, x

2

, x

3

, x

4

) = Π M(0, 1, 2, 4, 5, 7, 8, 9, 10, 12, 14, 15)

f(x

1

, x

2

, x

3

, x

4

) = Σm(0, 2, 8, 9, 10, 15) + d(1, 3, 6, 7)

Hãy kim tra li kt qu bng cách s dng nhp thit k bng bng

chân tr (qua Waveform Editor)

9. M t hàm logic 4 bin có giá tr ra là 1 nu 3 trong 4 bin vào là 1.

Thit k và cài !t hàm này bng: sơ " mch; bng chân tr; và VHDL.

VHDL-BTOT-trang 3/11

10. Thit k mch nhân 2 s nh phân 2 bit: Z = A x B, vi A=A

1

A

0

,

B=B

1

B

0

và Z=Z

3

Z

2

Z

1

Z

0

. Thit k và cài !t bng 1 trong 3 cách design

entry.

11. So sánh 2 s A (2 bit: A

1

A

0

), B (2 bit: B

1

B

0

); h có 3 ngõ ra f1=1 nu

A=B, f2=1 nu A < B và f3=1 nu A>B.

12. Tơng t câu trên cho A và B #u là d liu 4 bit.

13. Mch to parity ch$n cho d liu vào 4 bit.

14. Tơng t câu trên cho d liu là 8 bit.

15. Thit k mch thc hin x

2

+x+1 vi x=x

2

x

1

x

0

.

16. Thc hin hàm f hot ng theo bng sau:

Mch nhn m t s X (4 bit: x

3

x

2

x

1

x

0

) có 4 ngõ ra nh sau:

•

f1 = 1 nu X chia ht cho 2

•

f2 = 1 nu X chia ht cho 3

•

f3 = 1 nu X chia ht cho 4

•

f4 = 1 nu X chia ht cho 5

17.

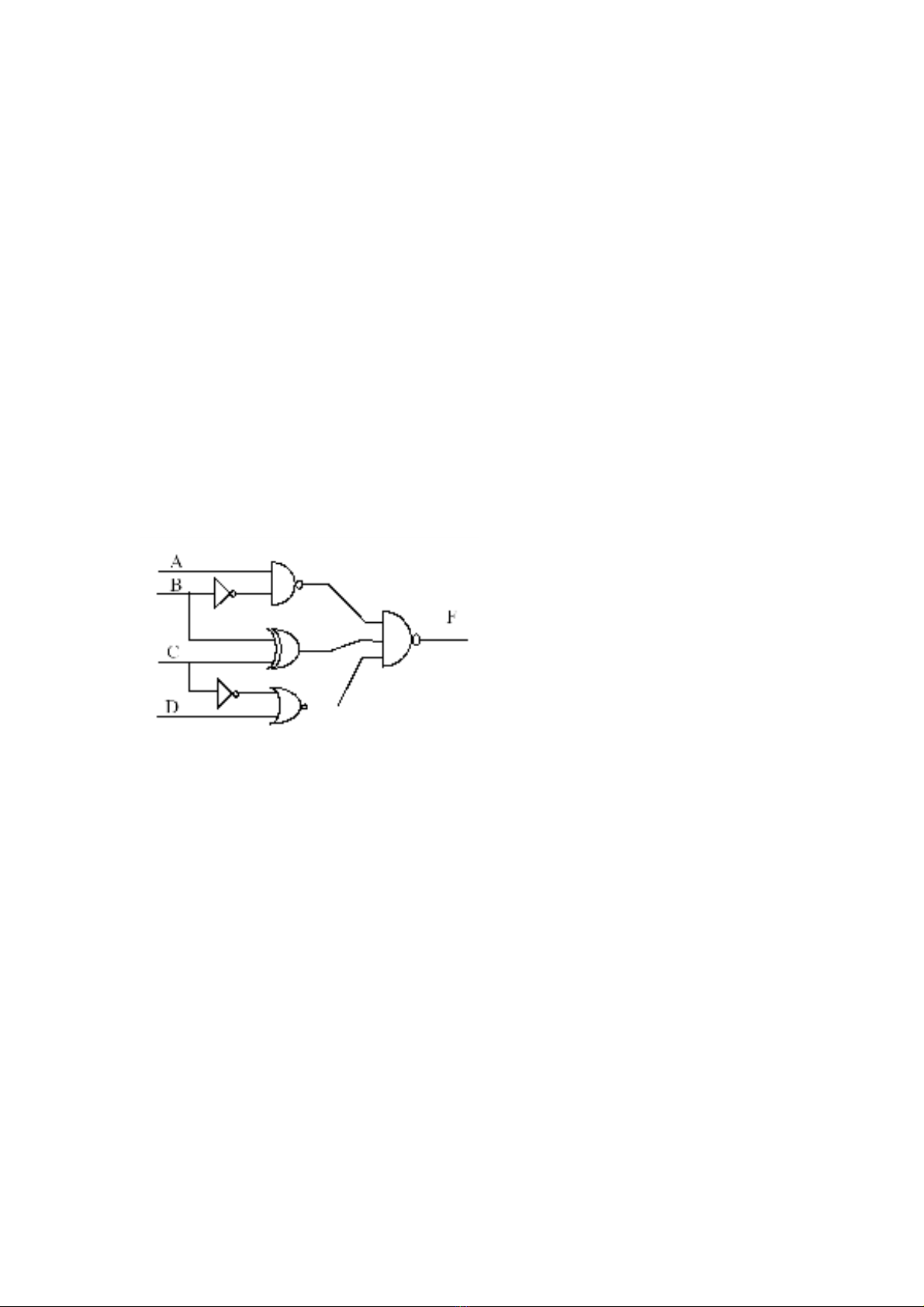

Cho mch sau:

a) Hãy tìm biu thc ti thiu cho F(A,B,C,D) dng SOP.

b) Vit chơng trình VHDL cài !t hàm trên.

c) Thêm m t tín hiu clk ch% cho ngõ ra F thay i khi có cnh lên

clk, còn khi clk trng thái khác thì ngõ ra F gi tr c& v'a trc ó.

18. Di ây là m t chơng trình VHDL mô t b m lên 4 bit ơn gin

LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

USE ieee.std_logic_unsigned.all ;

IS upcount ENTITY

PORT ( Clock : IN STD_LOGIC ;

Q : BUFFER STD_LOGIC_VECTOR(1 DOWNTO 0) ) ;

END upcount ;

ARCHITECTURE Behavior OF upcount IS

BEGIN

PROCESS ( Clock )

BEGIN

IF (Clock’EVENT AND Clock = ‘1’) THEN

VHDL-BTOT-trang 4/11

Q <= Q + ‘1’ ;

END IF ;

END PROCESS;

END Behavior ;

a) Da vào chơng trình trên hãy phát trin b m lên BCD (có 2 s mã

[digit] BCD là B

1

B

0

(ngha là m t' 00 n 99, B

1

và B

0

là 2 s 4 bit).

Gi s b m BCD làm vic theo cnh lên Clk và có thêm ngõ vào Reset

b(t "ng b vi Clk (ngha là b(t c khi nào Reset=1 thì các ngõ ra là 0)

b) Gi s B

1

và B

0

c a vào m t mch khác mà s cho ngõ ra G tr là

1 khi B

1

B

0

trong tm t' 00 n 90 và có tr s là b i s ca 9. Hãy cài !t

mch trên.

19. Thit k m t b m lên/xung 4 bit có 5 ngõ vào i#u khin là Up,

Down, Clear, Load và Enable (trong ó ch% có Clear và Enable hot ng

không "ng b vi Clk) có tác dng nh sau:

•

Enable =1 thì ngõ ra Data_out=giá tr 4 bit cha trong b m;

còn ngc li khi Enable =0 thì ngõ ra Data_out=”ZZZZ”; .

•

Load = 1 thì b m thc hin tác v np song song t' giá tr 4

bit Data_in vào b m cnh lên ca xung nhp Clk.

•

Clear = 1 thì xóa b m v# 0.

•

Up = 1 khi có cnh lên Clk thì làm b m tng thêm 1.

•

Down = 1 khi có cnh lên Clk thì làm b m gim i 1.

Nh vy b m hot ng bình th)ng khi Load=0 và Clear=0.

20. Mã VHDL ca 1 thit b là

1 entity test is

2 port (in1 : in bit_vector (2 downto 0);

3 out1 : out bit_vector (3 downto 0));

4 end test;

5 architecture test_arch of test is

6 begin

7 out1(0)<=in1(1);

8 out1(1)<=in1(2);

9 out1(2)<=in1(0) and in1(1);

10 out1(3)<=’1’;

11 end test_arch ;

Tên ca entity và thân architecture là gì? V sơ " mch.

21. V mch ca mã VHDL cho phía sau. Sa mã cho out1 có kiu

d liu là std_logic. Có th b tín hiu connect1 c không? Gii

thích.

1 entity nandgate is

2 port (

3 in1: in bit;

4 in2: in bit;

5 out1: out bit;

6 );

VHDL-BTOT-trang 5/11

7 end nandgate;

8 architecture nandgate_arch of nandgate is

9 signal connect1 : bit;

10 begin

11 connect1 <= in1 and in2;

12 out1 <= not connect1;

13 end nandgate_arch;

22. Các tín hiu a, b, c c gán nh sau:

a<= “01”; b<= “11”; c<= “10”;

Tìm d1 khi nó c gán: d1<= (a nand b) nand c;

Tìm d2 khi nó c gán: d2<= a nand (b nand c);

23. Cho trc bng chân tr ca cng xnor:

2 port (in1, in2 : in std_logic;

3 out1 : out std_logic);0

4 end test9;

Cài !t cng này bng:

a) Các phát biu when-else

b) Các phát biu with-select-when

c) Các phát biu case-when

d) Các phát biu if-then-else

24. Ta mun thit k mch phát hin có 3 ngõ vào là 1 trong 4 ngõ vào (D

3

,D

2

,D

1

và

D

0

) ca h, khi ó ngõ ra Y =1. Vit phơng trình ca Y. Cài !t mch bng các

lnh có th s dng c? Có bao nhiêu cách?

25. Thit k mch chuyn i mã BCD8421 sang mã quá 3 (excess-3) vi các cách

sau:

a. Vit trc tip entity cho mch này dùng các lnh "ng th)i.

b. Vit trc tip entity cho mch này dùng các lnh tun t.

c. Dùng hàm (function).

d. Dùng th tc (procedure).

26. Vit khai báo cho c(u trúc sau, gi s các tín hiu trong mã là port:

architecture write_entity of exercise2 is

begin

mapper: process (addr) begin

shadow_ram_sel <= ‘0’;

sram_sel <= ‘0’;

if addr >= x”0100” and addr < x”4000” then

shadow_ram_sel <= ‘1’;

elsif addr >= x”8000” and addr < x”C000” then

sram_sel <= ‘1’;

end if;

promsel <= ‘0’;

if eme_mapped = ‘0’ and bootup then

prom_sel <= ‘1’;

end if;

end process mapper;

mem_mapped <= shadow_ram_sel or sram_sel;