CH NG 1: C U TRÚC CHUNG C A MÁY TÍNHƯƠ Ấ Ủ

CH NG 1: C U TRÚC CHUNG C A MÁY TÍNHƯƠ Ấ Ủ

I. C U TRÚC MÔ PH NG CON NG I C A MÁY TÍNHẤ Ỏ ƯỜ Ủ

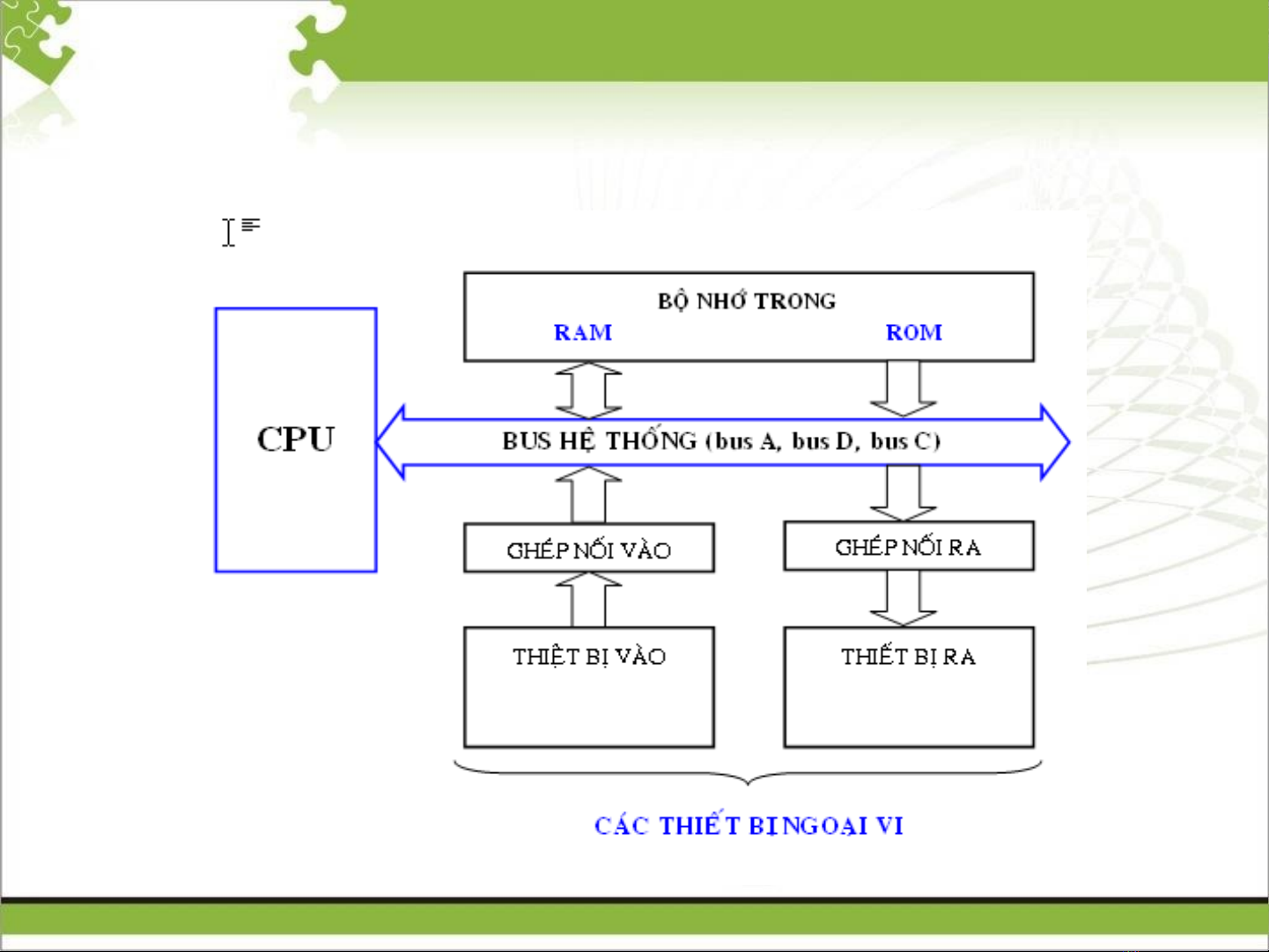

1. S đ c u trúc chungơ ồ ấ

2. Nguyên lý ho t đ ng chungạ ộ

Gi ng nh con ng i, máy tính có b não là b VXL. ố ư ườ ộ ộ

Trong b VXL có b đi u khi n (ộ ộ ề ể CU) và b tính toán s h c ộ ố ọ

logic (ALU).

Khác v i não ng i, b nh n m ngoài VXL, nh ng liên ớ ườ ộ ớ ằ ư

k t ch t ch v i VXL. ế ặ ẽ ớ

T ng đ ng v i các c quan ch p hành c a con ươ ươ ớ ơ ấ ủ

ng i, máy tính có các thi t b ngo i vi. Các thi t b này đ c ườ ế ị ạ ế ị ượ

n i v i VXL theo 3 nhóm dây song song dùng chung cho t t c ố ớ ấ ả

các thi t b g i là ế ị ọ Bus h th ngệ ố . Nh v y bus h th ng bao ư ậ ệ ố

g m ồ3 nhóm:

- Bus đ a ch (ị ỉ bus A) dùng đ truy n các thông tin đ a ể ề ị

chỉ

- Bus d li u (ữ ệ bus D) dùng đ trao đ i d li u ể ổ ữ ệ

- Bus đi u khi n (ề ể bus C) dùng đ truy n các tín hi u ể ề ệ

đi u khi n và các thông tin v tr ng thái thi t b . ề ể ề ạ ế ị

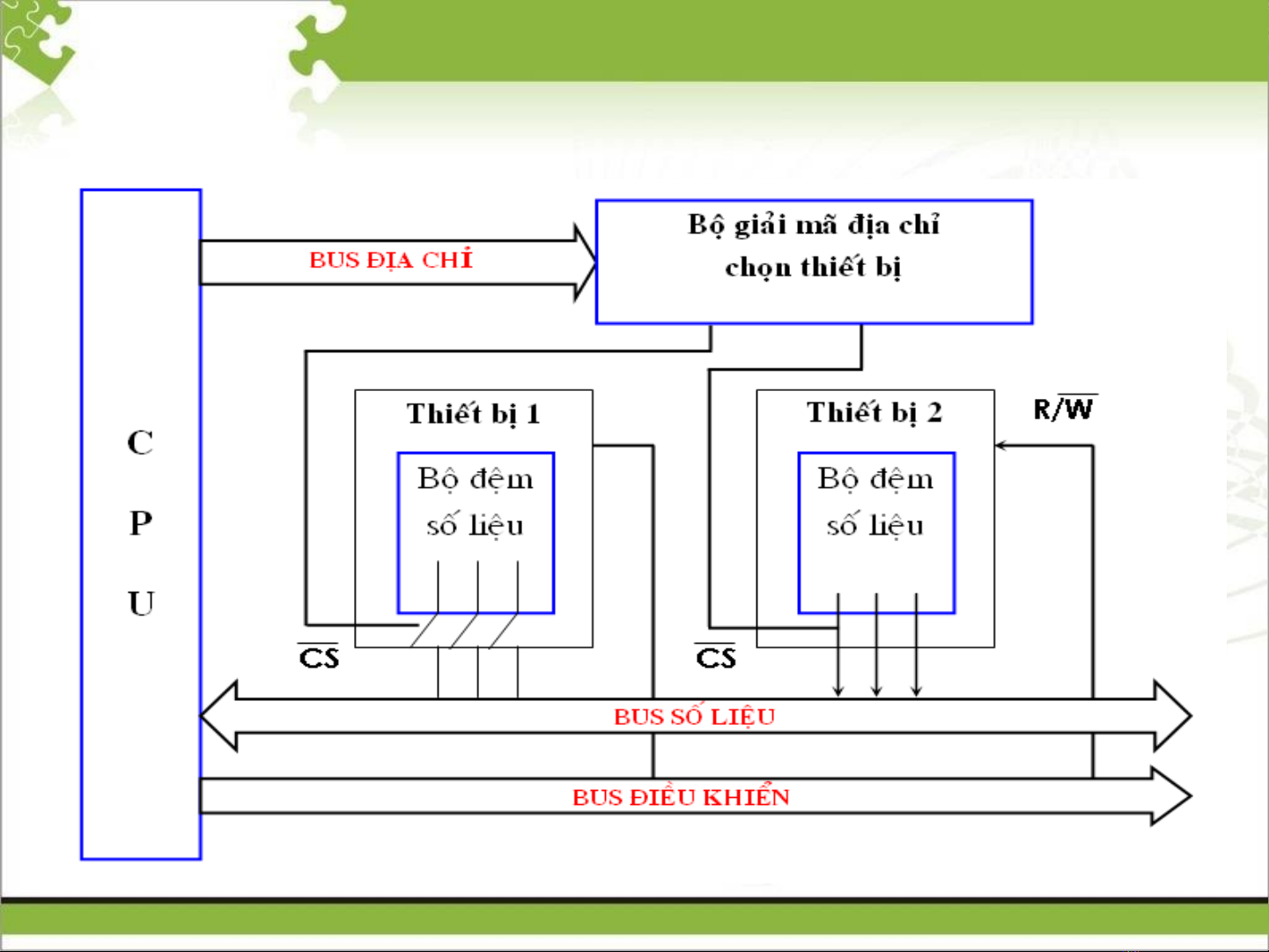

3. Quá trình làm vi c c a VXL v i các thi t b ngo i việ ủ ớ ế ị ạ

3. Quá trình làm vi c c a VXL v i các thi t b ngo i việ ủ ớ ế ị ạ

- B c 1ướ : VXL khi c n trao đ i thông tin v i thi t b ầ ổ ớ ế ị I/O nào thì s phát ẽ

đ a ch c a thi t b đó theo mã nh phân trên bus đ a ch . Gi s bus ị ỉ ủ ế ị ị ị ỉ ả ử

đ a ch có 8 dây, 8 dây đang truy n s nh phân ị ỉ ề ố ị 00000010, s nh ố ị

phân này có giá tr th p phân là ị ậ 2 và th p l c phân là ậ ụ 2h. Đi u đó có ề

nghĩa là VXL c n làm vi c v i thi t b ầ ệ ớ ế ị I/O có đ a ch là ị ỉ 2 (ho c ặ2h).

Khi đó b gi i mã đ a ch ,ộ ả ị ỉ có m i ở ỗ

thi t b ngo i vi s nh n đ c s nh ế ị ạ ẽ ậ ượ ố ị

phân nói trên t ừbus A và so sánh v i ớ

đ a ch c a mình. N u đúng thì b ị ỉ ủ ế ộ

gi i mã đ a ch s phát tín hi u đ ả ị ỉ ẽ ệ ể

m ởb đ m s li uộ ệ ố ệ – ph n n i gi a ầ ố ữ

thi t b s ế ị ố 2 và bus D, còn các b ộ

đ m d li u c a các thi t b khác s ệ ữ ệ ủ ế ị ẽ

đóng l i.ạ

- B c 2ướ : VXL trao đ i d li u v i thi t b s 2 qua ổ ữ ệ ớ ế ị ố bus

D. Còn trên bus C ch truy n tín hi u đ c/vi t (ỉ ề ệ ọ ế R/W) đ xác ể

đ nh chi u trao đ i d li u.ị ề ổ ữ ệ

* R/W = 1 : VXL đ c d li u t thi t b ngo i vi (ọ ữ ệ ừ ế ị ạ d li u ữ ệ

đ c truy n t thi t b ngo i vi v VXLượ ề ừ ế ị ạ ề ).

* R/W = 0 : VXL vi t d li u vào thi t b ngo i vi (ế ữ ệ ế ị ạ d li u ữ ệ

đ c truy n t VXL đ n thi t b ngo i viượ ề ừ ế ế ị ạ ).

T ng t nh v i thi t b ngo i vi, t i m i th i đi m ch ươ ự ư ớ ế ị ạ ạ ỗ ờ ể ỉ

có m t ô nh có đ a ch xác đ nh trên ộ ớ ị ỉ ị bus A đ c trao đ i d ượ ổ ữ

li u v i VXL. B nh g m nhi u ô nh , m i ô nh trong b nh ệ ớ ộ ớ ồ ề ớ ỗ ớ ộ ớ

đ c đ nh đ a ch tăng d n. Đ xác đ nh VXL t i th i đi m cho ượ ị ị ỉ ầ ể ị ạ ờ ể

tr c c n làm vi c v i thi t b ngo i vi hay ô nh , ng i ta s ướ ầ ệ ớ ế ị ạ ớ ườ ử

d ng thêm tín hi u ụ ệ IO/M thu c ộbus C.

* IO/M = 1 : VXL trao đ i d li u v i thi t b ngo i vi. ổ ữ ệ ớ ế ị ạ

* IO/M = 0 : VXL trao đ i d li u v i b nh . ổ ữ ệ ớ ộ ớ