Baøi giaûng Vi maïch

CH NG 8ƯƠ

THANH GHI

8.1 GI I THI UỚ Ệ

ph n tr c ta đã đ c bi t đ n các lo i FF. Chúng đ u có th l u trỞ ầ ướ ượ ế ế ạ ề ể ư ữ

(nh 1 bit) và ch khi có xung đ ng b thì bit đó m i truy n t i ngõ ra (đ o hayớ ỉ ồ ộ ớ ề ớ ả

không đ o). Bây gi n u ta m c nhi u FF n i ti p l i v i nhau thì s nh đ cả ờ ế ắ ề ố ế ạ ớ ẽ ớ ượ

nhi u bit. Các ngõ ra s ph n ho t đ ng theo xung nh p ck. Có th l y ngõ ra ề ẽ ầ ạ ộ ị ể ấ ở

t ng t ng FF (g i là các ngõ ra song song) hay t ng cu i (ngõ ra n i ti p). Nhừ ầ ọ ở ầ ố ố ế ư

v y m ch có th ghi l i d li u (nh ) và d ch chuy n nó (truy n) nên m ch đ cậ ạ ể ạ ữ ệ ớ ị ể ề ạ ượ

g i là ghi d ch. ọ ị

8.2 C U T O VÀ HO T Đ NGẤ Ạ Ạ Ộ

8.2.1 C u t oấ ạ

Ghi d ch có th đ c xây d ng t các FF khác nhau và cách m c cũng khácị ể ượ ự ừ ắ

nhau nh ng th ng dùng FF D, chúng đ c tích h p s n trong 1 IC g m nhi u FFư ườ ượ ợ ẵ ồ ề

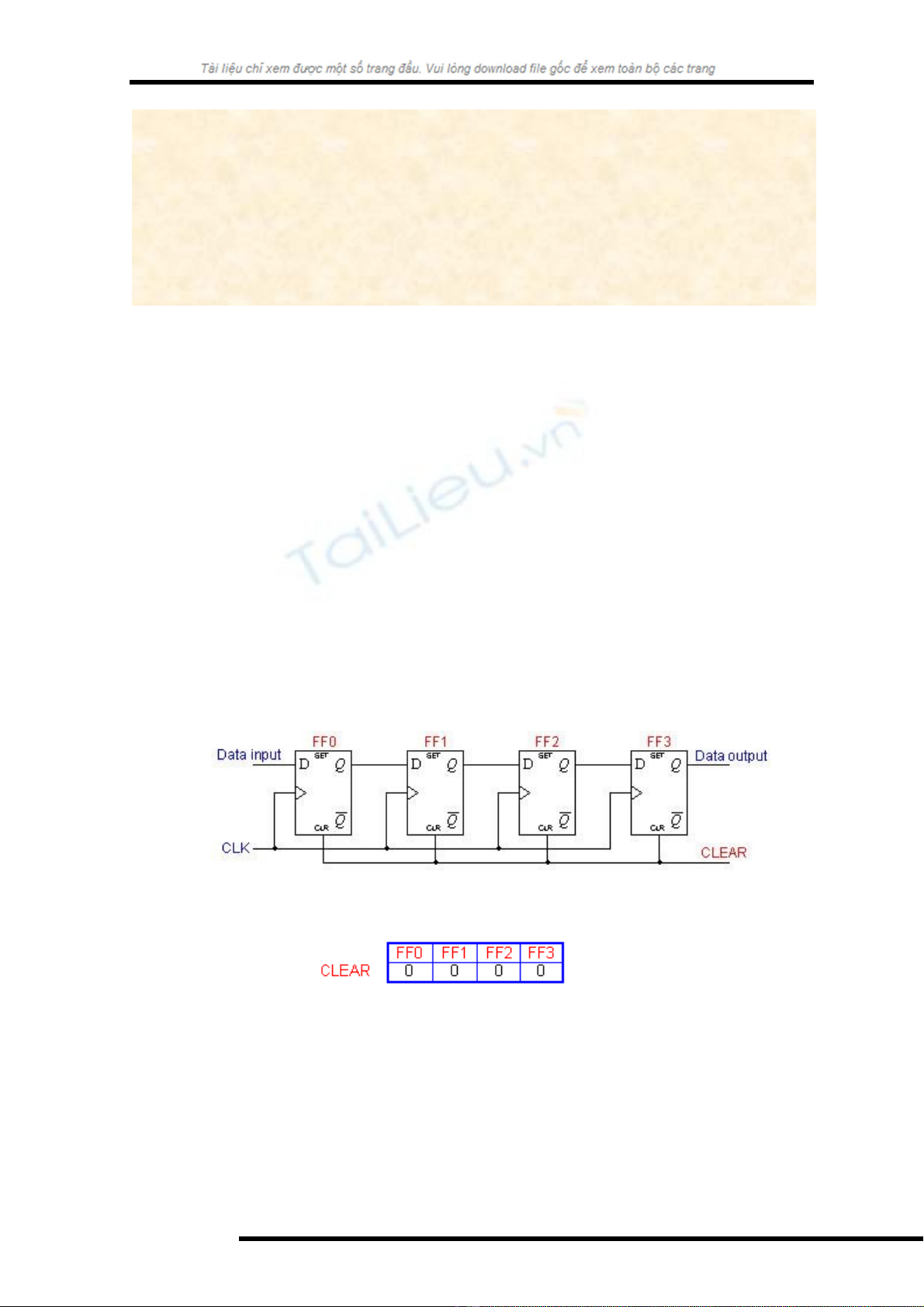

(t o nên ghi d ch n bit). Hãy xem c u t o c a 1 ghi d ch c b n 4 bit dùng FF D.ạ ị ấ ạ ủ ị ơ ả

Hình 8.1 Ghi d ch 4 bit c b nị ơ ả

8.2.2 Ho t đ ngạ ộ

Thanh ghi, tr c h t đ c xoá (áp xung CLEAR) đ đ t các ngõ ra v 0. Dướ ế ượ ể ặ ề ữ

li u c n d ch chuy n đ c đ a vào ngõ D c a t ng FF đ u tiên (FF0). m iệ ầ ị ể ượ ư ủ ầ ầ Ở ỗ

xung kích lên c a đ ng h ck, s có 1 bit đ c d ch chuy n t trái sang ph i, n iủ ồ ồ ẽ ượ ị ể ừ ả ố

ti p t t ng này qua t ng khác và đ a ra ngõ Q c a t ng sau cùng (FF3). Gi sế ừ ầ ầ ư ở ủ ầ ả ử

d li u đ a vào là 1001, sau 4 xung ck thì ta l y ra bit LSB, sau 7 xung ck ta l y raữ ệ ư ấ ấ

bit MSB.

Chöông 8: Thanh ghi

108

Baøi giaûng Vi maïch

N u ti p t c có xung ck và không đ a thêm d li u vào thì ngõ ra ch còn là 0ế ế ụ ư ữ ệ ỉ

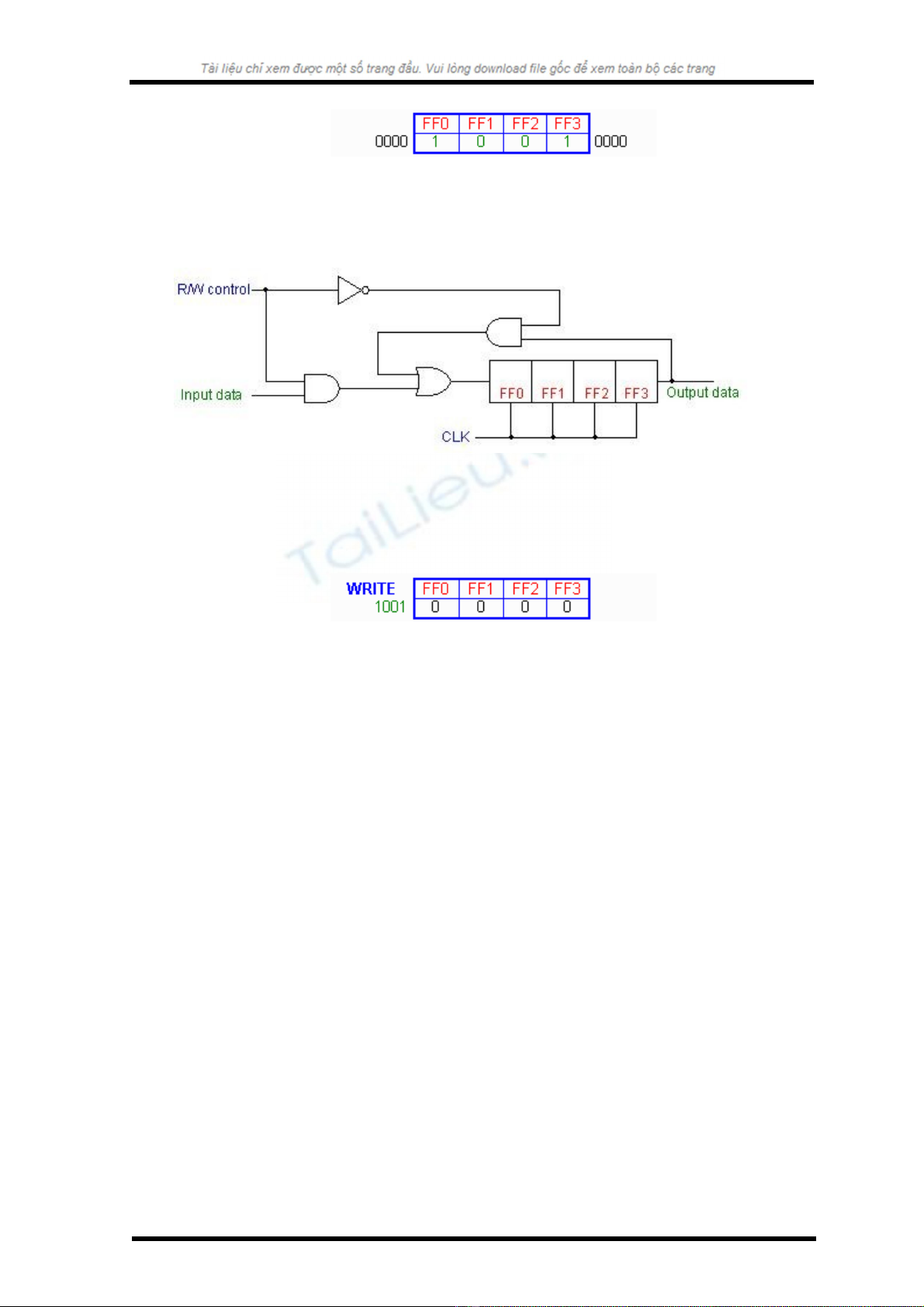

(các FF đã reset : đ t l i v 0 h t. Do đó ta ph i “h ng”ặ ạ ề ế ả ứ hay ghim d li u l i.ữ ệ ạ

M t cách làm là s d ng 2 c ng AND, 1 c ng OR và 1 c ng NOT nh hình d iộ ử ụ ổ ổ ổ ư ướ

đây.

Hình 8.2 Cho phép ch t d li u tr c khi d ch ra ngoàiố ữ ệ ướ ị

D li u đ c đ a vào thanh ghi khi đ ng đi u khi n R/W control m cữ ệ ượ ư ườ ề ể ở ứ

cao (Write). D li u ch đ c đ a ra ngoài khi đ ng đi u khi n m c th pữ ệ ỉ ượ ư ườ ề ể ở ứ ấ

(Read).

Có nhi u cách chia lo i thanh ghi d ch (SR).ề ạ ị

- Theo s t ng FF (s bit): SR có c u t o b i bao nhiêu FF m c n i ti p thìố ầ ố ấ ạ ở ắ ố ế

có b y nhiêu bit (ra song song). Ta có SR 4 bit, 5 bit, 8 bit, 16 bit …ấ

Có th có SR nhi u bit h n b ng cách m c nhi u SR v i nhau hay dùng côngể ề ơ ằ ắ ề ớ

ngh CMOS (các máy tính s d ng SR nhi u bit).ệ ử ụ ề

- Theo cách ghi d ch cóị

SISO vào n i ti p ra n i ti p.ố ế ố ế

SIPO vào n i ti p ra song song.ố ế

PISO vào song song ra n i ti p.ố ế

PIPO vào song song ra song song.

- Theo chi u d ch có SR trái, ph i, hay c 2 chi u.ề ị ả ả ề

- Theo m ch ra có lo i th ng và 3 tr ng thái.ạ ạ ườ ạ

Lo i vào n i ti p ra song song và ra n i ti p.ạ ố ế ố ế

Lo i v a kh o sát m c 1 thu c lo i ghi d ch vào n i ti p ra n i ti p. Đâyạ ừ ả ở ụ ộ ạ ị ố ế ố ế

cũng là c u trúc c a m ch ghi d ch vào n i ti p ra song song. D li u s đ c l yấ ủ ạ ị ố ế ữ ệ ẽ ượ ấ

ra 4 ngõ Q c a 4 t ng FF, vì chung nh p đ ng h nên d li u cũng đ c l y raở ủ ầ ị ồ ồ ữ ệ ượ ấ

cùng lúc.

Chöông 8: Thanh ghi

109

Baøi giaûng Vi maïch

Hình 8.3 M ch ghi d ch vào n i ti p ra song songạ ị ố ế

B ng sau cho th y làm nh th nào d li u đ c đ a t i ngõ ra 4 t ng FF:ả ấ ư ế ữ ệ ượ ư ớ ầ

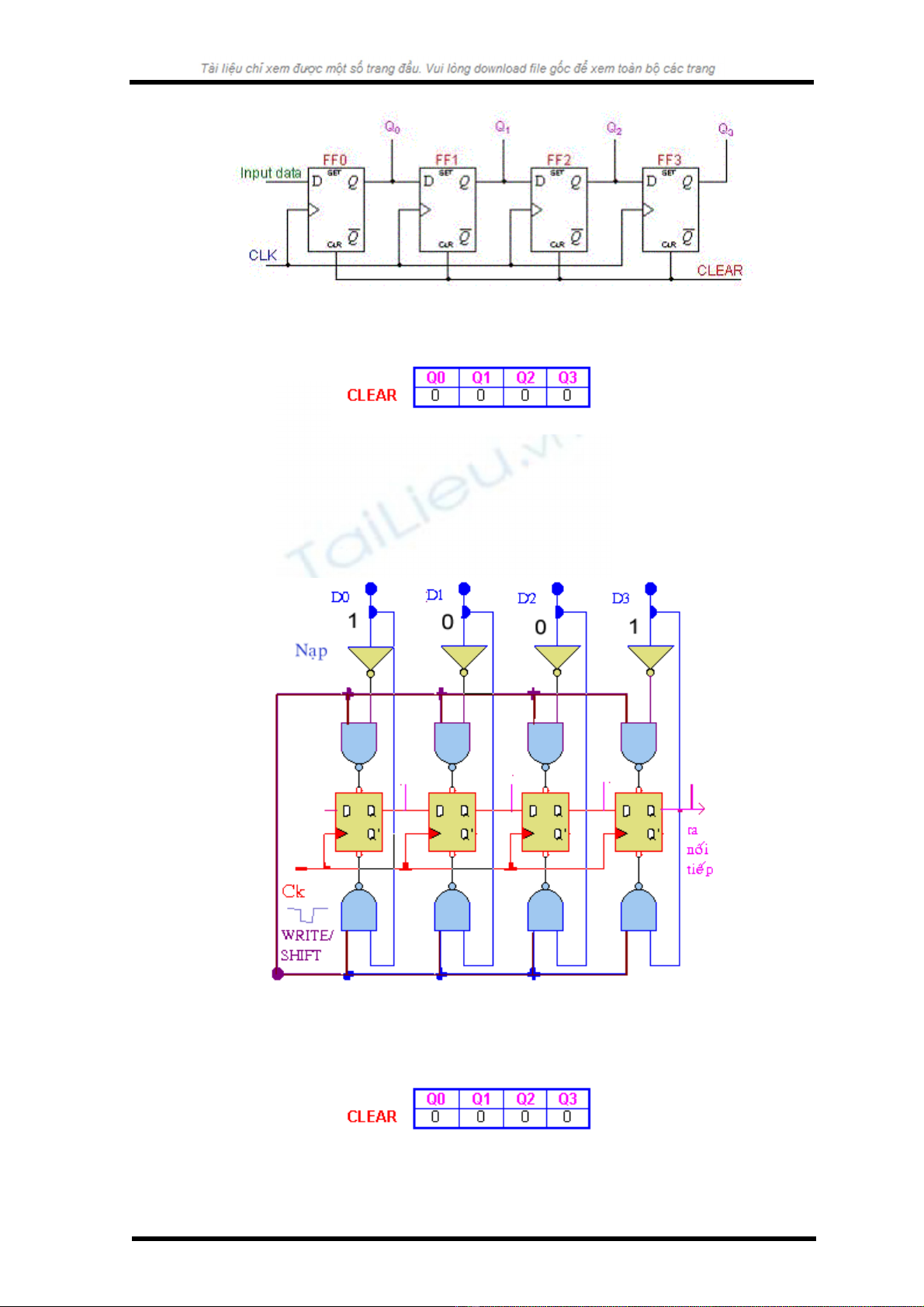

Lo i đ c n p song song (vào song song) ra n i ti p và song song.ạ ượ ạ ố ế

Bây gi mu n đ a d li u vào song song (còn g i là n p song song) ta có thờ ố ư ữ ệ ọ ạ ể

t n d ng ngõ vào không đ ng b Pr và Cl c a các FF đ n p d li u cùng m t lúcậ ụ ồ ộ ủ ể ạ ữ ệ ộ

vào các FF. Nh v y có th dùng thêm 2 c ng nand và m t c ng not cho m i t ng.ư ậ ể ổ ộ ổ ỗ ầ

M ch m c nh sau:ạ ắ ư

Hình 8.4 M ch ghi d ch n p song songạ ị ạ

M ch ho t đ ng bình th ng khi n p song song th p nh đã nói. Khi n pạ ạ ộ ườ ạ ở ấ ư ạ

song song WRITE = 1 cho phép n p.ạ

Chöông 8: Thanh ghi

110

Baøi giaûng Vi maïch

ABCD đ c đ a vào Pr và Cl đ t và xoá đ Q0 = A, Q1 = B, … Xung ck vàượ ư ặ ể

ngõ vào n i ti p không có tác d ng (vì s d ng ngõ không đ ng b Pr và Cl).ổ ế ụ ử ụ ồ ộ

M t cách khác không s d ng chân Pr và Cl đ c minh ho nh hình d iộ ử ụ ượ ạ ư ướ

đây.Các c ng nand đ c thêm vào đ n p các bit th p D1, D2, D3. Ngõổ ượ ể ạ ấ

WRITE/SHIFT dùng đ cho phép n p ( m c th p) và cho phép d ch ( m c cao).ể ạ ở ứ ấ ị ở ứ

D li u n p và d ch v n đ c th c hi n đ ng b nh các m ch tr c.ữ ệ ạ ị ẫ ượ ự ệ ồ ộ ư ạ ướ

Hình 8.5 M ch ghi d ch n p song song ra n i ti pạ ị ạ ố ế

V i m ch hình 8.5 ngõ ra d li u là n i ti p, ta cũng có th l y ra d li uớ ạ ữ ệ ố ế ể ấ ữ ệ

song song nh hình 8.6ư ở , C u trúc m ch không khác so v i trên. D li u đ cấ ạ ớ ở ữ ệ ượ

đ a vào cùng lúc và cũng l y ra cùng lúc (m ch nh là t ng đ m và ho t đ ng khiư ấ ạ ư ầ ệ ạ ộ

có xung ck tác đ ng lên.ộ

Hình 8.6 M ch ghi d ch vào song song ra song songạ ị

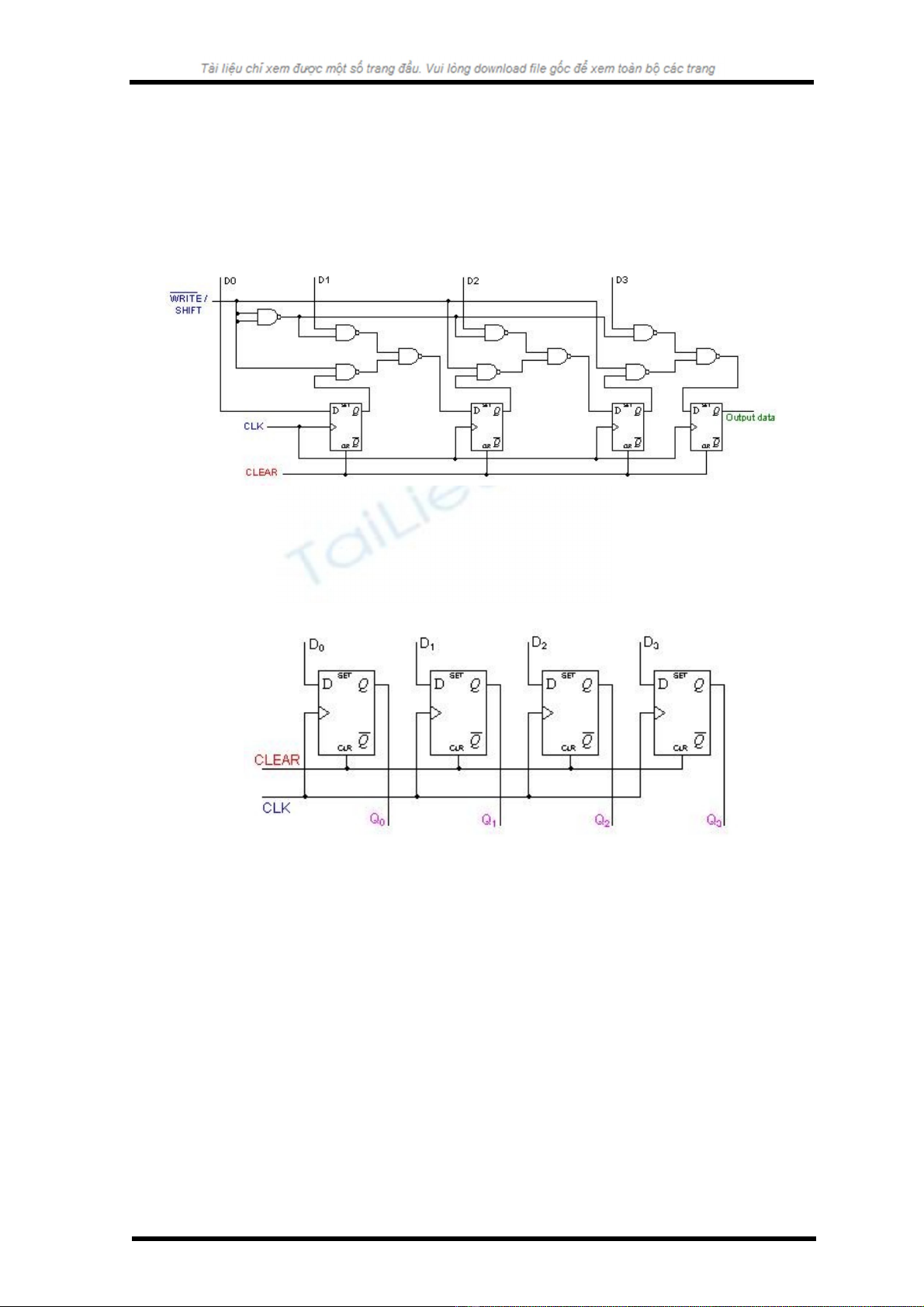

Ghi d ch 2 chi uị ề

Nh đã th y, các m ch ghi d ch nói nh ng ph n trên đ u đ a d li u raư ấ ạ ị ở ữ ầ ề ư ữ ệ

bên ph i nên chúng thu c lo i ghi d ch ph i. Đ có th d ch chuy n d li u ng cả ộ ạ ị ả ể ể ị ể ữ ệ ượ

tr l i (d ch trái)ở ạ ị ta ch vi c cho d li u vào ngõ D c a t ng cu i cùng, ngõ ra Qỉ ệ ữ ệ ủ ầ ố

đ c đ a t i t ng k ti p, … D li u l y ra t ng đ u.ượ ư ớ ầ ế ế ữ ệ ấ ở ầ ầ

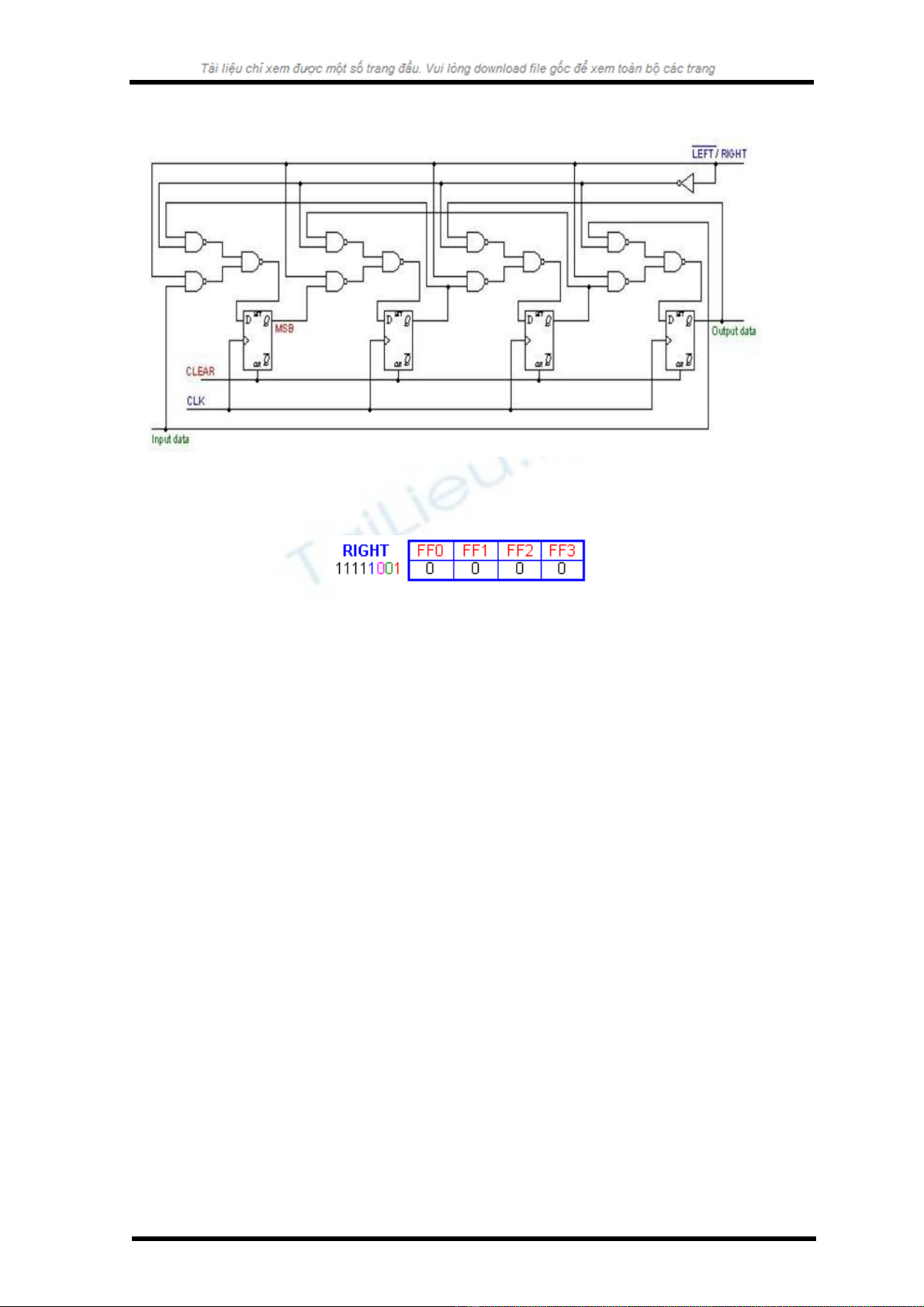

Đ d ch chuy n c 2 chi u, có th n i m ch nh hình d i đây:ể ị ể ả ề ể ố ạ ư ướ

Chöông 8: Thanh ghi

111

Baøi giaûng Vi maïch

Hình 8.7 M ch ghi d ch cho phép d ch chuy n c 2 chi uạ ị ị ể ả ề

V i m ch trên, các c ng NAND và đ ng ớ ạ ổ ườ cho phép d ch chuy n d li u tráiị ể ữ ệ

hay ph i. B ng d i đây minh ho cho m ch trên: d li u s d ch ph i 4 l n r iả ả ướ ạ ạ ữ ệ ẽ ị ả ầ ồ

d ch trái 4 l n. Đ ý là th t 4 bit ra b đ o ng c l i so v i chúng trên.ị ầ ể ứ ự ị ả ượ ạ ớ ở

Nh n th y r ng các ghi d ch mô t trên đ u dùng các FF r i, r i ph i thêmậ ấ ằ ị ả ở ề ờ ồ ả

nhi u c ng logic ph đ t o các lo i SR khác nhau. Trong th c t ghi d ch đ cề ổ ụ ể ạ ạ ự ế ị ượ

tích h p s n các FF và đã n i s n nhi u đ ng m ch bên trong, ng i s d ng chợ ẵ ố ẵ ề ườ ạ ườ ử ụ ỉ

còn ph i làm m t s đ ng n i bên ngoài đi u khi n các ngõ cho phép thôi. Cácả ộ ố ườ ố ề ể

SR cũng đ c tích h p s n các ch c năng nh v a có th d ch trái d ch ph i v aượ ợ ẵ ứ ư ừ ể ị ị ả ừ

vào n i ti p v a n p song song. đây là m t s ghi d ch hay đ c dùng:ố ế ừ ạ Ở ộ ố ị ượ

Li t kêệ

7494 : 4bit vào song song, n i ti p; ra n i ti pố ế ố ế

7495/LS95 : 4 bit, vào song song/n i ti p; ra song song; d ch chuy n tráiố ế ị ể

ph iả

7495/LS96 : 5 bit, vào n i ti p/song song; ra song song n i ti pố ế ố ế

74164/LS164 : 8 bit vào song song ra n i ti pố ế

74165/LS765 : 8 bit, vào song song/n i ti p; ra n i ti p b túcố ế ố ế ổ

74166/LS166 : 8 bit; vào song song/n i ti p; ra n i ti p; có th n p đ ngố ế ố ế ể ạ ồ

bộ

74194/LS194 : 4 bit vào song song/n i ti p; ra song song; n p đ ng bố ế ạ ồ ộ

d ch chuy n trái ph iị ể ả

74195/LS195 : 4 bit, vào song/n i ti p; ra song song; t ng đ u vào JKố ế ầ ầ ở

74295/LS295 : nh 74194/LS194 nh ng ra 3 tr ng tháiư ư ạ

74395/LS295 : 4 bit vào song song; ra song song 3 tr ng tháiạ

74LS671/672 : 4 bit có thêm ch tố

Chöông 8: Thanh ghi

112

![Cắt bằng hồ quang điện [Mới Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2014/20140331/hoangtuxuquang/135x160/7351396310863.jpg)

![MAX232: Mạch DUAL EIA 232 DRIVERS/RECEIVERS [Thông tin chi tiết]](https://cdn.tailieu.vn/images/document/thumbnail/2011/20110611/tanthanh2603/135x160/max232_501.jpg)

![Bài giảng công tắc tơ [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/93891778142285.jpg)

![Giáo trình Điện tử tương tự 1: Phần 1 [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260506/vispacex_27/135x160/69111778210056.jpg)