18

18

1/1/2007

1/1/2007 Đ

Đạ

ại h

i họ

ọc B

c Bá

ách khoa H

ch khoa Hà

àN

Nộ

ội

i

Ô

Ô xy

xy h

hó

óa

anhi

nhi

ệ

ệ

t

t(

(ti

tiế

ếp

p)

)

Ô

Ô xy

xy h

hó

óa

at

tạ

ạo

ol

lớ

ớp

pSiO

SiO2

2m

mỏ

ỏng

ng

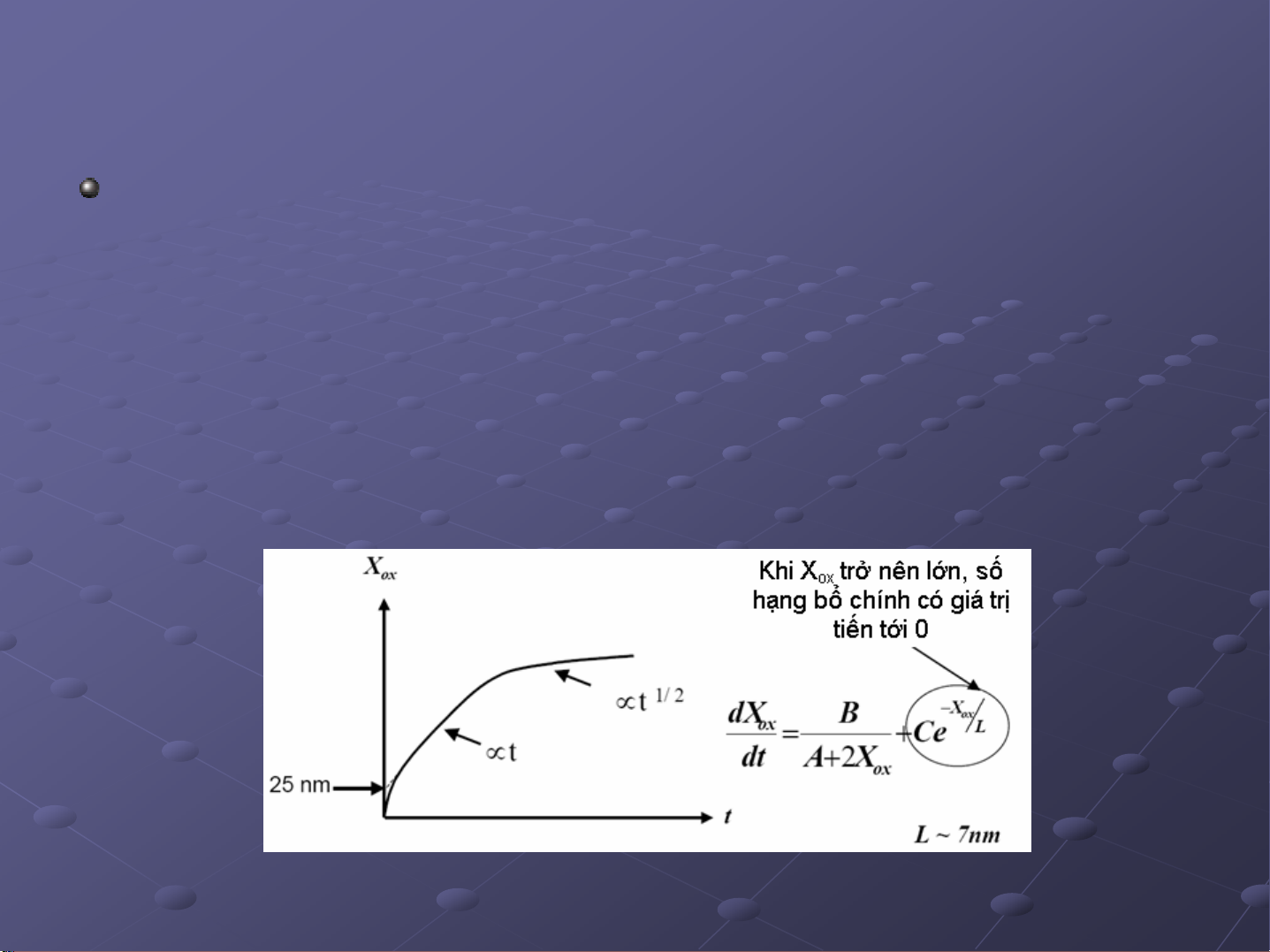

Mô

Mô h

hì

ình

nh Deal

Deal –

–Grove

Grove ph

phù

ùh

hợ

ợp

pr

rấ

ất

tt

tố

ốt

tv

vớ

ới

ik

kế

ết

tqu

quả

ảth

thự

ực

cnghi

nghiệ

ệm

m,

, tr

trừ

ừtrư

trườ

ờng

ng h

hợ

ợp

p

c

cá

ác

cl

lớ

ớp

pSiO

SiO2

2m

mỏ

ỏng

ng dư

dướ

ới

i20 nm

20 nm thu

thu đư

đượ

ợc

ctrong

trong ô

ô xy

xy h

hó

óa

akhô

khô v

vớ

ới

iO

O2

2.

.

V

Vì

ìv

vậ

ậy

y,

, trong

trong c

cá

ác

cl

lớ

ớp

pSiO

SiO2

2d

dà

ày

y,

, ngư

ngườ

ời

ita

ta thư

thườ

ờng

ng l

lấ

ấy

ygi

giá

átr

trị

ịl

lớ

ớp

pSiO

SiO2

2ban

ban đ

đầ

ầu

uX

Xi

i=

=

25 nm

25 nm khi

khi á

áp

pd

dụ

ụng

ng mô

mô h

hì

ình

nh Deal

Deal –

–Grove.

Grove.

C

Cá

ác

cl

lớ

ớp

pSiO

SiO2

2m

mỏ

ỏng

ng đư

đượ

ợc

cd

dù

ùng

ng trong

trong c

cá

ác

clinh

linh ki

kiệ

ện

ntunnel,

tunnel, c

cũ

ũng

ng như

nhưtrong

trong VLSI

VLSI –

–

ULSI

ULSI đi

điệ

ện

ná

áp

pngu

nguồ

ồn

nth

thấ

ấp

p.

.

Ngo

Ngoà

ài

ira

ra,

, c

cũ

ũng

ng c

cầ

ần

nk

kể

ểđ

đế

ến

nl

lớ

ớp

pSiO

SiO2

2t

tự

ựnhiên

nhiên v

vớ

ới

ichi

chiề

ều

ud

dà

ày

y~ 10

~ 10 –

–100

100 Å

Åthư

thườ

ờng

ng

ph

phá

át

ttri

triể

ển

nr

rấ

ất

tnhanh

nhanh trên

trên b

bề

ềm

mặ

ặt

tSi

Si s

sạ

ạch

ch ngay

ngay c

cả

ảở

ởnhi

nhiệ

ệt

tđ

độ

ộkhông

không cao

cao.

.

19

19

1/1/2007

1/1/2007 Đ

Đạ

ại h

i họ

ọc B

c Bá

ách khoa H

ch khoa Hà

àN

Nộ

ội

i

Ô

Ô xy

xy h

hó

óa

anhi

nhi

ệ

ệ

t

t(

(ti

tiế

ếp

p)

)

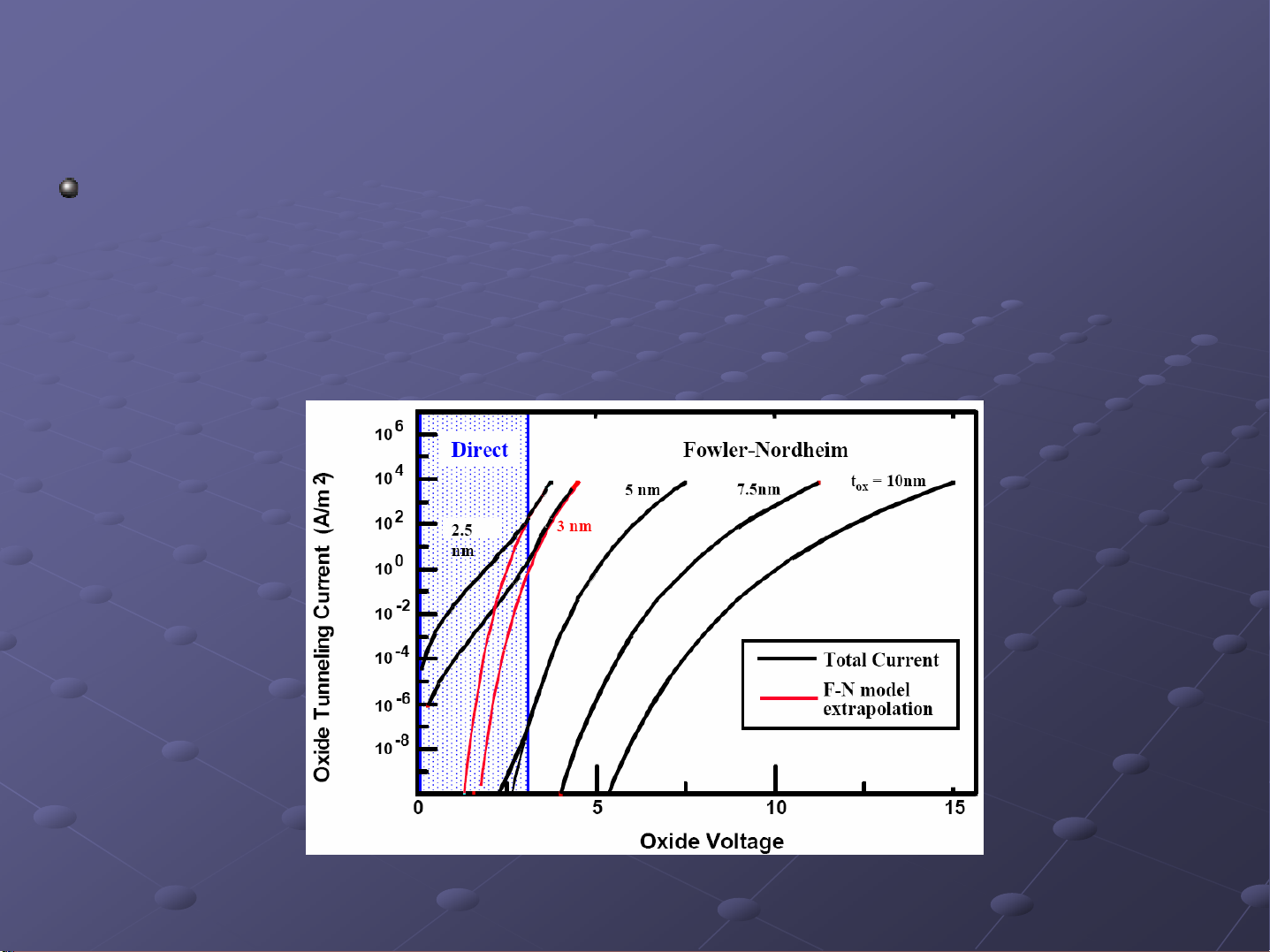

L

Lớ

ớp

ptunnel SiO

tunnel SiO2

2

So

So s

sá

ánh

nh th

thự

ực

cnghi

nghiệ

ệm

mv

và

àk

kế

ết

tqu

quả

ảmô

mô h

hì

ình

nh Fowler

Fowler –

–Nordheim

Nordheim trong

trong

c

cá

ác

cl

lớ

ớp

ptunnel SiO

tunnel SiO2

2.

.

V

Vớ

ới

ic

cá

ác

cl

lớ

ớp

ptunnel SiO

tunnel SiO2

2không

không d

dà

ày

yhơn

hơn3 nm

3 nm còn

còn c

có

óph

phầ

ần

nđ

đó

óng

ng g

gó

óp

pc

củ

ủa

adòng

dòng

rò

rò b

bổ

ổsung do

sung do cơ

cơch

chế

ếtunnel

tunnel tr

trự

ực

cti

tiế

ếp

p.

.

20

20

1/1/2007

1/1/2007 Đ

Đạ

ại h

i họ

ọc B

c Bá

ách khoa H

ch khoa Hà

àN

Nộ

ội

i

Ô

Ô xy

xy h

hó

óa

anhi

nhi

ệ

ệ

t

t(

(ti

tiế

ếp

p)

)

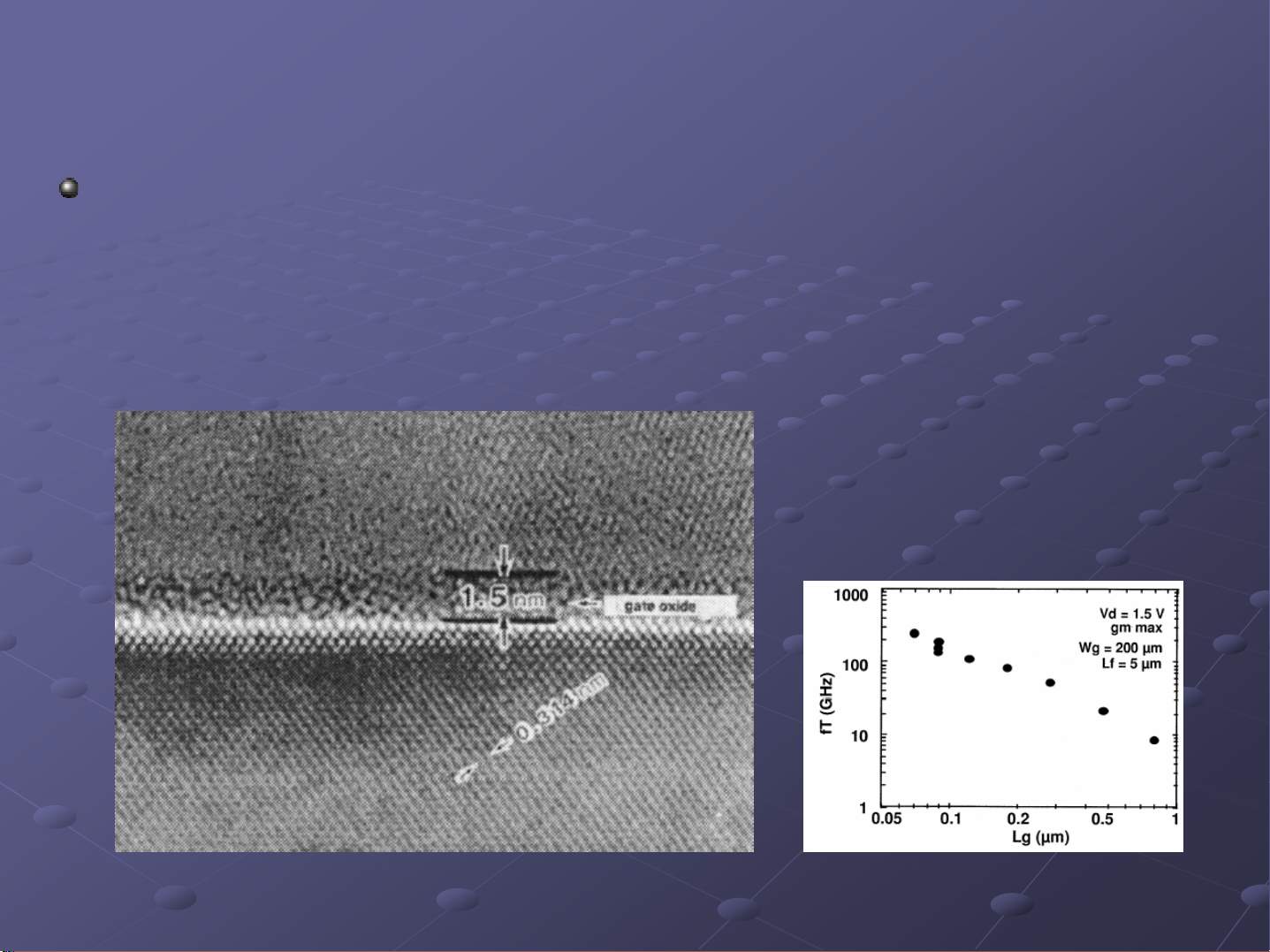

Ả

Ảnh

nh hi

hiể

ển

nvi

vi đi

điệ

ện

nt

tử

ửtruy

truyề

ền

nqua

qua c

củ

ủa

al

lớ

ớp

pSiO

SiO2

2.

.

Khi

Khi l

lớ

ớp

pSiO

SiO2

2m

mỏ

ỏng

ng đi

đi,

, hi

hiệ

ệu

uứ

ứng

ng tunnel

tunnel tăng

tăng lên

lên.

. Tuy

Tuy nhiên

nhiên,

, n

nế

ếu

uchi

chiề

ều

ud

dà

ài

ikênh

kênh d

dẫ

ẫn

ngi

giả

ảm

mxu

xuố

ống

ng,

, c

có

ó

th

thể

ểb

bỏ

ỏqua

qua hi

hiệ

ệu

uứ

ứng

ng tunnel

tunnel –

–l

lạ

ại

ic

có

óth

thể

ểch

chế

ết

tạ

ạo

oc

cá

ác

ctransistor MOS

transistor MOS k

kí

ích

ch thư

thướ

ớc

cnh

nhỏ

ỏv

vớ

ới

il

lớ

ớp

pô

ô xit

xit c

cự

ực

c

c

cử

ửa

ar

rấ

ất

tm

mỏ

ỏng

ng.

.

V

Vớ

ới

ic

cá

ác

cl

lớ

ớp

ptunnel SiO

tunnel SiO2

21,5 nm

1,5 nm t

tầ

ần

ns

số

ốc

cắ

ắt

tc

củ

ủa

aMOSFET

MOSFET lên

lên t

tớ

ới

i150 GHz.

150 GHz.

MOSFET

MOSFET v

vớ

ới

il

lớ

ớp

pSiO

SiO2

2c

cự

ực

cc

cử

ửa

ad

dà

ày

y1,3 nm

1,3 nm c

có

óm

mậ

ật

tđ

độ

ộdòng

dòng đi

điệ

ện

ntrong

trong kênh

kênh d

dẫ

ẫn

n1,8

1,8 mA

mA/mm,

/mm, đ

độ

ộh

hỗ

ỗ

d

dẫ

ẫn

nc

cự

ực

ccao

cao 1,2 S/mm

1,2 S/mm t

tạ

ại

ingu

nguồ

ồn

nnuôi

nuôi 1,5 V.

1,5 V. Đã

Đãc

có

óc

cá

ác

cm

mạ

ạch

ch VLSI

VLSI v

vớ

ới

ingu

nguồ

ồn

nnuôi

nuôi 0,5 V.

0,5 V.

21

21

1/1/2007

1/1/2007 Đ

Đạ

ại h

i họ

ọc B

c Bá

ách khoa H

ch khoa Hà

àN

Nộ

ội

i

Ô

Ô xy

xy h

hó

óa

anhi

nhi

ệ

ệ

t

t(

(ti

tiế

ếp

p)

)

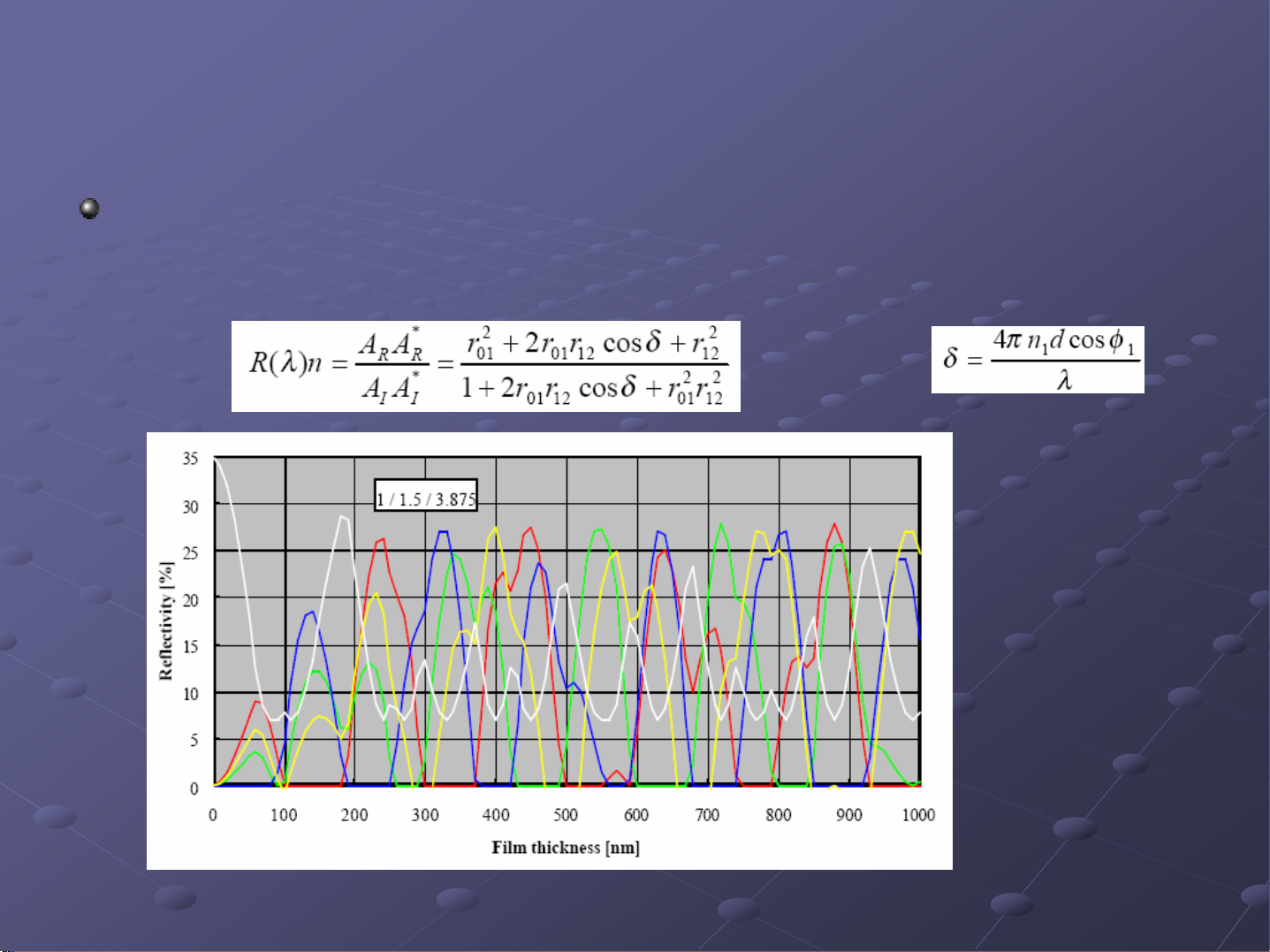

B

Bả

ảng

ng so

so m

mà

àu

uđ

để

ểđ

đá

ánh

nh gi

giá

áchi

chiề

ều

ud

dà

ày

yl

lớ

ớp

pSiO

SiO2

2trên

trên đ

đế

ếSi

Si

D

Dự

ựa

atrên

trên m

mẫ

ẫu

uh

hệ

ệgương

gương Fabry

Fabry –

–Perot (

Perot (hai

hai m

mặ

ặt

tgi

giớ

ới

ih

hạ

ạn

nsong

song song

song trên

trên v

và

àdư

dướ

ới

i

c

củ

ủa

al

lớ

ớp

pSiO

SiO2

2),

), t

tí

ính

nh h

hệ

ệs

số

ốph

phả

ản

nx

xạ

ạ:

: v

vớ

ới

i:

:

Theo Principles of

Semiconductor

Devices, B. Van

Zeghbroeck, 2004

22

22

1/1/2007

1/1/2007 Đ

Đạ

ại h

i họ

ọc B

c Bá

ách khoa H

ch khoa Hà

àN

Nộ

ội

i

C

Cá

ác

cb

bà

ài

it

tậ

ập

pv

ví

íd

dụ

ụ

B

Bà

ài

i1

1:

: X

Xá

ác

cđ

đị

ịnh

nh th

thờ

ời

igian

gian c

cầ

ần

nthi

thiế

ết

tđ

để

ểt

tạ

ạo

ol

lớ

ớp

pô

ô xit

xit SiO

SiO2

2chi

chiề

ều

ud

dà

ày

y0,35

0,35 μ

μm

m trên

trên phi

phiế

ến

nSi

Si đ

đị

ịnh

nh

hư

hướ

ớng

ng (100)

(100) không

không c

có

ól

lớ

ớp

pSiO

SiO2

2ban

ban đ

đầ

ầu

u(

(τ

τ= 0),

= 0), ở

ởnhi

nhiệ

ệt

tđ

độ

ộ1000

1000 °

°C,

C, trong

trong c

cả

ảhai

hai trư

trườ

ờng

ng h

hợ

ợp

pô

ô xy

xy

h

hó

óa

akhô

khô v

và

àẩ

ẩm

m.

.

Gi

Giả

ải

i:

:

X

Xé

ét

ttrư

trườ

ờng

ng h

hợ

ợp

p

ô

ô xy

xy h

hó

óa

aẩ

ẩm

m

.

. Trư

Trướ

ớc

ctiên

tiên,

, ở

ởnhi

nhiệ

ệt

tđ

độ

ộ1000

1000 °

°C

C t

tì

ìm

mc

cá

ác

ch

hệ

ệs

số

ố:

:

Th

Thờ

ời

igian

gian c

cầ

ần

nthi

thiế

ết

tđ

để

ểô

ô xy

xy h

hó

óa

aẩ

ẩm

mkhông

không c

có

ól

lớ

ớp

pô

ô xit

xit ban

ban đ

đầ

ầu

ul

là

à:

:

Tương

Tương t

tự

ự,

, trư

trườ

ờng

ng h

hợ

ợp

p

ô

ô xy

xy h

hó

óa

akhô

khô

cho

cho (B/

(B/A)

A)dry

dry = 0,0859

= 0,0859 μ

μm/h

m/h;

; B

Bdry

dry = 0,01077

= 0,01077 μ

μm

m2

2/h

/h v

và

àth

thờ

ời

i

gian

gian c

cầ

ần

nthi

thiế

ết

tđ

để

ểô

ô xy

xy h

hó

óa

akhô

khô l

là

àt =

t = 15,4 h

15,4 h hay

hay 15 h 27 min

15 h 27 min.

.

()

h

m

K

eV

eV

h

m

kT

eV

h

m

A

B

wet

μμμ

32.1

273100010617,8

93,1

exp108,5

93,1

exp108,5

5

77 =

⎟

⎟

⎟

⎟

⎠

⎞

⎜

⎜

⎜

⎜

⎝

⎛

+

⎟

⎠

⎞

⎜

⎝

⎛×

−

⎟

⎠

⎞

⎜

⎝

⎛×=

⎟

⎠

⎞

⎜

⎝

⎛−

⎟

⎠

⎞

⎜

⎝

⎛×=

⎟

⎠

⎞

⎜

⎝

⎛

−

() ()

h

m

K

eV

eV

h

m

kT

eV

h

m

Bwet

2

5

22 291,0

273100010617,8

71,0

exp188

71,0

exp188

μμμ

=

⎟

⎟

⎟

⎟

⎠

⎞

⎜

⎜

⎜

⎜

⎝

⎛

+

⎟

⎠

⎞

⎜

⎝

⎛×

−

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

=

⎟

⎠

⎞

⎜

⎝

⎛−

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

=

−

(

)

shayh

h

m

m

h

m

m

B

X

AB

X

toxox 10min4169,0

291,0

35,0

32,1

35,0

/2

2

2=+=+=

μ

μ

μ

μ

![Đề cương môn Công nghệ chế biến khí [năm học]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250910/thangkho12072002@gmail.com/135x160/88581757470791.jpg)

![Đề cương Công nghệ Polyme và Compozit [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250901/hungngao2711/135x160/24771756869342.jpg)