428

Y z h i X Y

i i i

11

[ ( ) ] (16.33)

ở đây Y-1 = 0.0 và Y-N = Y(z)

Chú ý rằng Y(z) là một trễ của tín hiệu đầu ra thực sự N+1 chu kỳ. Biểu

thức (16.31) và (16.33) xác định cấu trúc của phần tử xử lý và mảng tâm thu.

Chúng được giới thiệu trên hình 16.11. Hiển nhiên là cấu trúc này là một cấu

trúc tâm thu thực sự như là một cấu trúc pipeline. Vậy ưu điểm của cấu trúc là

gì? Nếu tìm hiểu lại cách xây dựng hệ thống pipeline tự động chúng ta thấy

thời gian trễ tổng sẽ tăng lên nếu tốc độ nạp vào tăng lên. Làm thế nào chúng

ta đạt được điều này? Chúng ta sẽ dùng một thực tế là Y(z) là X(z) có các trễ

bằng nhau và bị nhiễu gợn qua hệ thống ở cùng một tốc độ. Điều thực sự làm

cho hệ thống chậm lại là X(z) sẽ phải chờ để hoàn thành phép nhân cộng của

một từ trước khi một tín hiệu mẫu đầu vào mới được đưa vào.

Cái mà chúng ta mong muốn làm bây giờ là chia nhỏ các PE thành các đơn

vị nhỏ hơn và điều này điều kiển tốc độ đưa vào và tác động tổng thể tăng thời

gian trễ. Hình 16.12 giới thiệu cách thay đổi PE để tăng tốc độ đưa vào. Phần

cần phải cộng thêm vào là các dây trễ cho Xi và Yi để là cho các đầu vào có thể

bắt kịp với xử lý của bộ nhân pipeline. Các dây trễ này đồng thời cũng được

đặt vào bus X cho phép Xi và Yi truyền đồng thời. Các bộ nhân được thiết kế

với tốc độ đưa vào vượt quá 300 Mhz, và thế cấu trúc bộ lọc FIR thiết kế dùng

kỹ thuật này có thể xử lý 300 triệu từ/giây. Thời gian trễ tổng cho hệ thống này

sẽ tăng lên như dự đoán.

Các PE có kiểu giới thiệu trong hình 16.12 thì thông thường không được

xây dựng từ các chip riêng lẻ, bao gồm các thanh ghi và các bộ nhân mà được

xây dựng từ các thiết kế tuỳ chọn VLSI (hầu hết các trường đại học ở Bắc Mỹ

có các cơ sở sản xuất các bo mạch này). Dựa trên yêu cầu của các thiết kế này,

các nhà sản xuất VLSI phải làm cho chúng có dạng giống các PE.

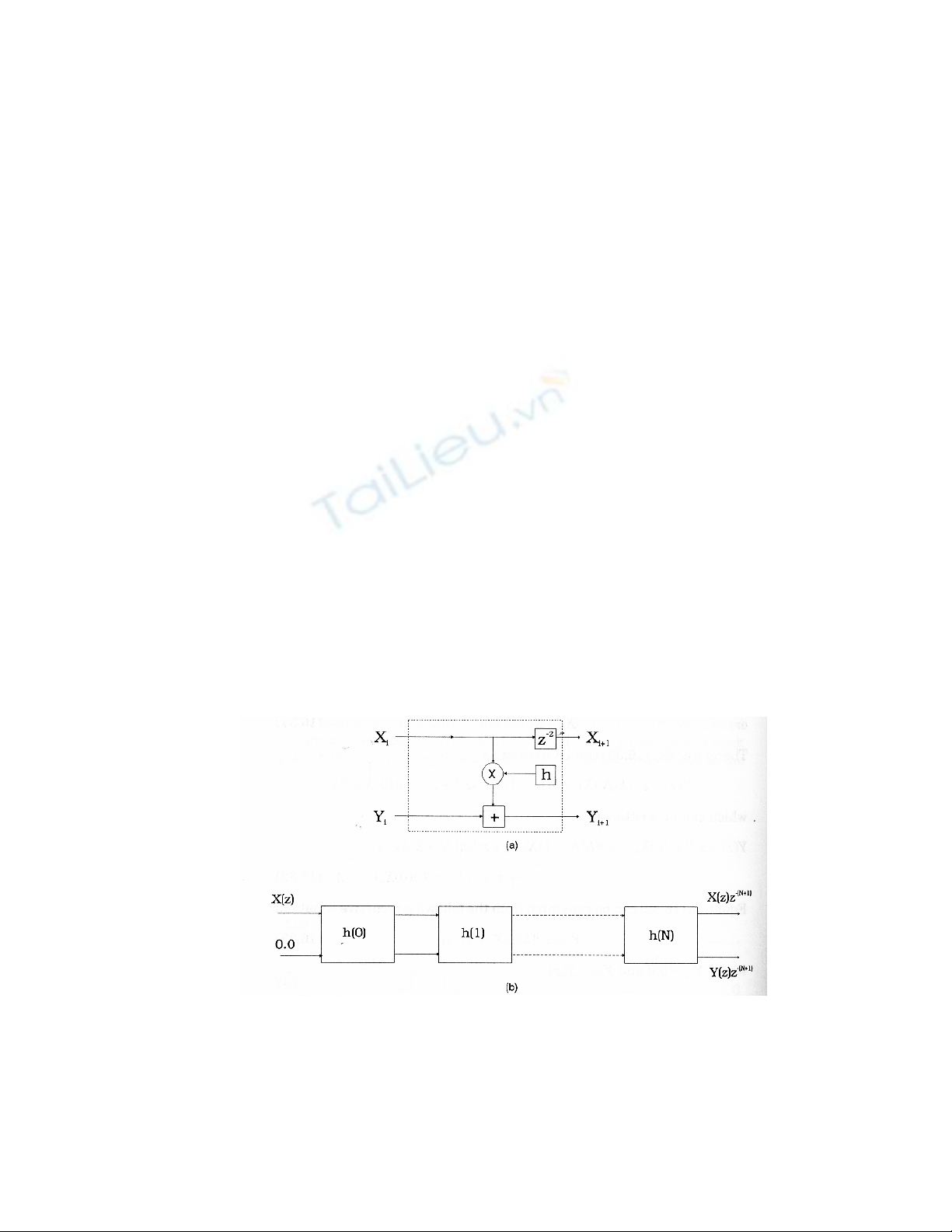

Hình 16.11 (a) Cấu trúc PE; (b) Cấu trúc tâm thu thực, pipeline thực của bộ

lọc FIR.

429

Hình 16.12 Đường ống PE.

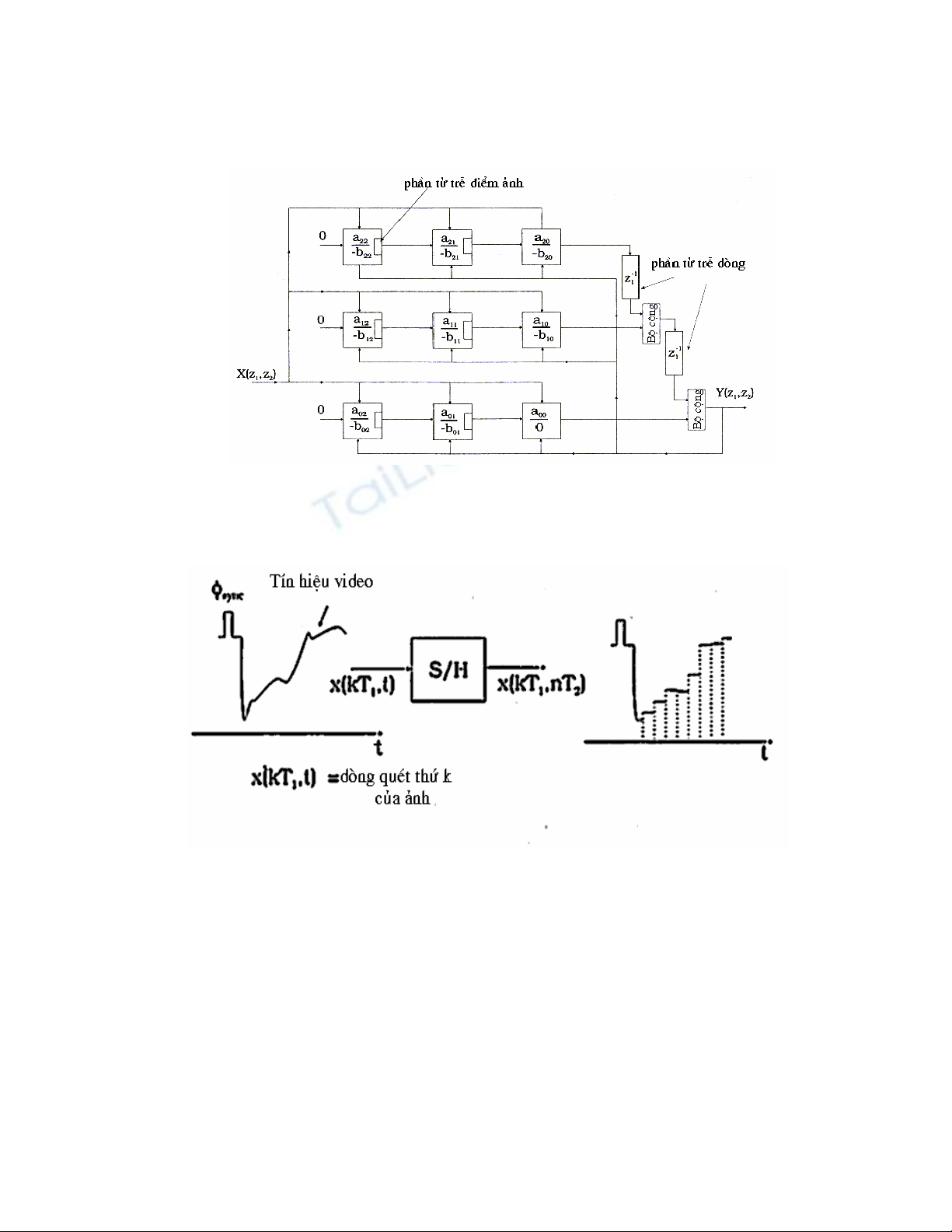

Thực hiện của các cấu trúc FIR 2-D theo kiểu cấu trúc tâm thu như cấu trúc

pipeline có thể được tạo ra dùng nhiều loại cấu trúc tương tự như cấu trúc 1-D

FIR của hình 16.11 b và các PE như trong hình 16.12, có kèm theo các dây trễ

số (các thanh ghi dịch chiều dài, chiều rộng một từ chiều dài bằng chiều rộng

ảnh). Một cấu trúc tâm thu pipeline 2 2 FIR được giới thiệu trong hình

16.13. Cấu trúc này được thiết kế thích ứng cho xử lý tín hiệu video tốc độ

cao. Kiểu cấu trúc này, nếu thực hiện dùng PE của hình 16.12, được gọi là tâm

thu mức bit.

Hình 16.13 Bộ lọc FIR 2-D ống tâm thu.

430

16.5 Thực hiện tâm thu của các bộ lọc 2-D IIR

Các bộ lọc hai chiều IIR có thể chiếu lên các cấu trúc tâm thu dùng giả thiết

biến đổi z được mô tả ở trong phần trên. Tuy nhiên, có thể biến đổi các bộ lọc

IIR như một cấu trúc pipeline thực sự. Lý do là các tín hiệu ra quá khứ thì cần

để tính các tín hiệu ra hiện tại, và vì lý do đấy, pipeline về mặt vật lý là không

thể được. Các bộ lọc IIR có thể được thực hiện như cấu trúc tâm thu mức từ.

Một ví dụ cho thực hiện được cho ở dưới đây.

Chúng ta hãy xem xét một bộ lọc 2 2 FIR được cho bởi

2

01

2

0

2

0

022122121 ),(),(),(

i

i

jjij

j

ij

j

ij zzzzYbzzzXazzY (16.34)

Điều này có thể biểu diễn thành

i

iii

i

iioio

zzzYbzzXazzzYb

zzXazzzYbzzXazzY

1212212

1

2211

211

2

0

1

2212121

))}],(,(()),(

),(({)),()),([(),( (16.35)

Với b00 = 0.

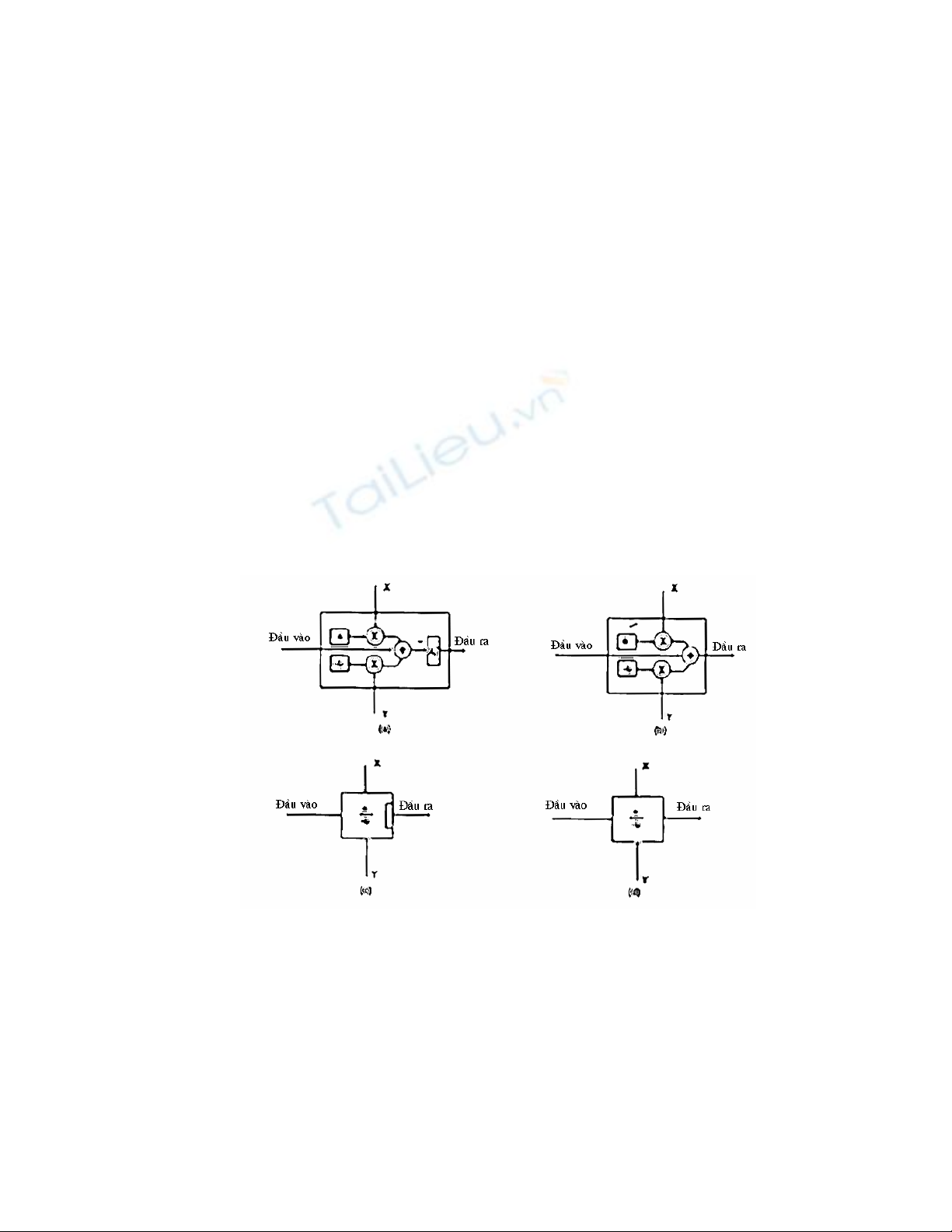

Hình 16.14 (a) PE m

ột chốt ra; (b) PE không chốt ra;

(c) Ký hiệu của (a); (d) Ký hiệu của (b).

Biểu thức (16.35) xác định hai kiểu của các PE: một kiểu có một chốt ra, và

một kiểu khác không chốt ra. Hình 16.14 giới thiệu hai kiểu của các PE, và

chiếu của biểu thức (16.35) lên một cấu trúc tâm thu là hình 16.15. Cấu trúc là

431

một kiểu giả tâm thu. Có thể dễ dàng nhận ra đây không phải là một cấu trúc

pipeline.

Tốc độ đưa vào của cấu trúc giới thiệu trong hình 16.15 được quyết định

bởi thời gian trễ của một phép nhân-cộng của chiều dài một từ. Các bộ nhân có

khả năng làm việc với thời gian trễ tổng 20 nano giây (50 MHz). Xử lý các tín

hiệu HDTV sẽ yêu cầu tốc độ đưa vào vào khoảng 44 triệu điểm/giây, phù hợp

với thiết kế này.

Có một số dạng khác của thiết kế này. Cho ví dụ biểu thức (16.35) có thể

viết lại dưới dạng:

))()(()(

)()()(),(

12

1

211

1

220

2

122

1

1212021

zYzzYzzY

zzYzzYzYzzY

(16.36)

Ở đây Y0(z2), Y1(z2), Y2(z2) được xác định bằng biểu thức (16.35). Kết quả

thực hiện được cho trong hình 16.16. Các phần tử PE được định nghĩa như

trong hình 16.14.

16.6 Lấy mẫu và lưu giữ chức năng của các bộ lọc FIR

Các yếu tố ảnh hưởng đến hoạt động của các bộ lọc 2-D IIR dùng cấu trúc

như trong hình 16.15 và 16.16 là chất lượng của phần cứng và tốc độ đưa vào.

Một số các ứng dụng yêu cầu tốc độ đưa vào vượt ra ngoài khoảng 40 triệu

điểm/giây như các ứng dụng trong radar. Một số các yếu tố có thể thực hiện

với giá thành thấp hơn bằng cách dùng các phần tử tương tự. Các CCD có thể

thay thế các thanh ghi dịch dòng (z1-1), và các phần tử lấy mẫu có thể thay

bằng các chốt số. Các bộ nhân tương tự có thể thay các bộ nhân số. Bởi vì tốc

độ xử lý của các mạch điện tương tự có thể lớn hơn rất nhiều tốc độ xử lý của

các mạch điện số nên có thể rất dễ dàng áp dụng cho các ứng dụng HDTV.

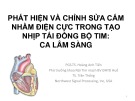

Chúng ta sẽ giả thiết rằng tín hiệu đầu vào các cấu trúc lọc là một dòng quét

trên ảnh TV, x(kT1, t). Một mạch điện lấy mẫu, đặt tại cổng đầu vào, lấy mẫu

và làm tròn tín hiệu từ một chu kỳ xung nhịp trở đi, sẽ chuyển tín hiệu tương

tự sang tín hiệu dưới dạng lấy mẫu (xem hình 16.17). Cấu trúc của các PE

tương tự được cho trong hình 16.18. Ba dạng xung nhịp điều khiển xử lý và

nạp lại. Các xung này được ký hiệu là

1,

2 và

sync.

1 và

2 là các tín hiệu

xung không trùng nhau và

sync là xung đồng bộ dòng của tín hiệu lấy vào

(xem hình 16.17).

432

Hình 16.15 Thực hiện nửa tâm thu cho bộ lọc IIR.

Hình 16.16 Bộ lọc IIR 2-Dkích thước 2 2 thực hiện tâm thu sử dụng các

thanh ghi dịch hai đường.

Hình 16.17 Lấy mẫu ảnh quét xen kẽ.

Trong PE kết quả: -(ax - by + yIN) được chứa trên tụ C1 trong mức cao của

xung nhịp

1. Trong mức cao của

2 kết quả được truyền đến tụ C2 và sẵn sàng

cho PE tiếp theo xử lý trong chu kỳ tiếp theo của xung nhịp

1. Trong hồi tiếp

(từ một dòng này đến dòng tiếp theo) xung đồng bộ dòng được dùng để mở hai

chốt tương tự SW1 và SW2, và nạp lại hai tụ C1 và C2. Khởi tạo trong PE việc

lưu và nạp lại có thể thay thế bằng một thiết bị lấy mẫu (S/H) được điều khiển

bằng chỉ một chu kỳ xung nhịp. Giá trị lưu giữ trong S/H được chuyển ra để

xử lý khi một giá trị mới được lấy mẫu. Các mạch S/H có thể hoạt động ở tần

![Đề thi Excel: Tổng hợp [Năm] mới nhất, có đáp án, chuẩn nhất](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251103/21139086@st.hcmuaf.edu.vn/135x160/61461762222060.jpg)

![Bài tập Tin học đại cương [kèm lời giải/ đáp án/ mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251018/pobbniichan@gmail.com/135x160/16651760753844.jpg)

![Bài giảng Nhập môn Tin học và kỹ năng số [Mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251003/thuhangvictory/135x160/33061759734261.jpg)

![Tài liệu ôn tập Lý thuyết và Thực hành môn Tin học [mới nhất/chuẩn nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20251001/kimphuong1001/135x160/49521759302088.jpg)

![Trắc nghiệm Tin học cơ sở: Tổng hợp bài tập và đáp án [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250919/kimphuong1001/135x160/59911758271235.jpg)

![Giáo trình Lý thuyết PowerPoint: Trung tâm Tin học MS [Chuẩn Nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2025/20250911/hohoainhan_85/135x160/42601757648546.jpg)