Khoa KTMT Vũ Đ c Lungứ1

Ch ng 6 – Ki n trúc b l nhươ ế ộ ệ

6.1. Phân lo i ki n trúc b l nhạ ế ộ ệ

6.2. Đ a ch b nhị ỉ ộ ớ

6.3. Mã hóa t p l nhậ ệ

6.3.1. Các tiêu chu n thi t k d ng th c l nhẩ ế ế ạ ứ ệ

6.3.2. Opcode m r ngở ộ

6.3.3. Ví d v d ng th c l nhụ ề ạ ứ ệ

6.3.4. Các ch đ l p đ a chế ộ ậ ị ỉ

6.4. B l nhộ ệ

6.4.1. Nhóm l nh truy n d li uệ ề ữ ệ

6.4.2. Nhóm l nh tính toán s h cệ ố ọ

6.4.3. Nhóm l nh Logicệ

6.4.4. Nhóm các l nh d ch chuy nệ ị ể

6.4.5. Nhóm các l nh có đi u ki n và l nh nh yệ ề ệ ệ ả

6.5. C u trúc l nh CISC và RISCấ ệ

Khoa KTMT Vũ Đ c Lungứ2

6.1. Phân lo i ki n trúc b l nhạ ế ộ ệ

ki n trúc ngăn x p (stack), ế ế

ki n trúc thanh ghi tích lũy (Accumulator)ế

ki n trúc thanh ghi đa d ng GPRA(general-purpose register ế ụ

architecture).

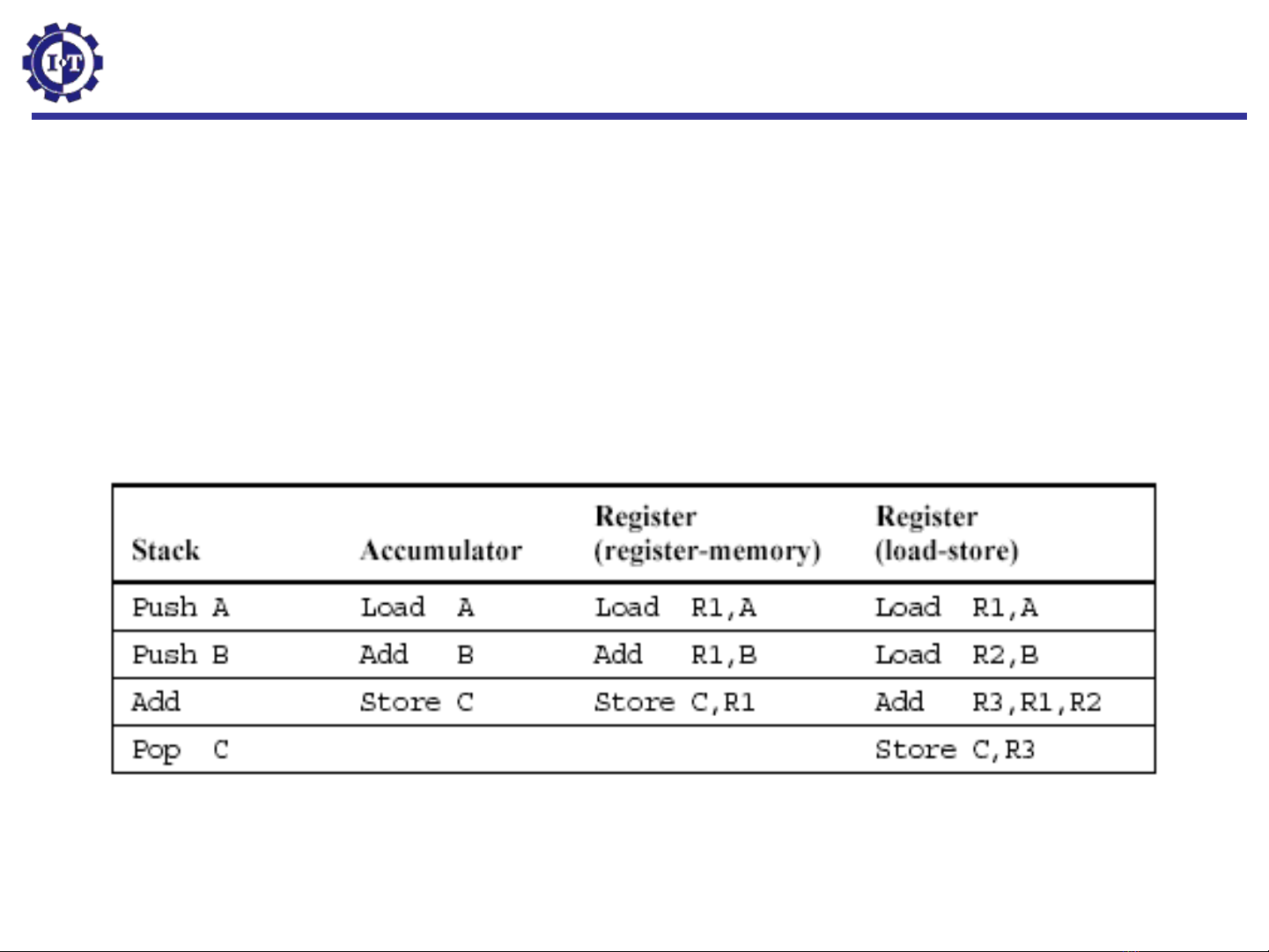

Ví d phép tính C = A + B đ c dùng trong các ki u ki n trúc:ụ ượ ể ế

Khoa KTMT Vũ Đ c Lungứ3

Ki u ki n trúc GPR ể ế

u đi m Ư ể

–Dùng thanh ghi, m t d ng l u tr trong c a CPU có t c đ nhanh ộ ạ ư ữ ủ ố ộ

h n b nh ngoàiơ ộ ớ

–Trình t th c hi n l nh có th m i th tự ự ệ ệ ể ở ọ ứ ự

–Dùng thanh ghi đ l u các bi n và nh v y s gi m thâm nh p đ n ể ư ế ư ậ ẽ ả ậ ế

b nh => ch ng trình s nhanh h nộ ớ ươ ẽ ơ

Nh c đi mượ ể

–L nh dàiệ

–S l ng thanh ghi b gi i h nố ượ ị ớ ạ

Ngăn x pế (Stack) ?

Thanh ghi tích luỹ (Accumulator Register) ?

Khoa KTMT Vũ Đ c Lungứ4

Ki u ki n trúc thanh ghi đa d ngể ế ụ

l nh có 2 toán h ng ệ ạ

ADD A, B

l nh có 3 toán h ng ệ ạ

ADD A, B, C

S toán h ng b nh có th thay đ i t 0 t i 3ố ạ ộ ớ ể ổ ừ ớ

Các lo i toán h ngạ ạ

•thanh ghi-thanh ghi (ki u này còn đ c g i n p - l u tr ), ể ượ ọ ạ ư ữ

•thanh ghi - b nh ộ ớ

•b nh - b nh . ộ ớ ộ ớ

Khoa KTMT Vũ Đ c Lungứ5

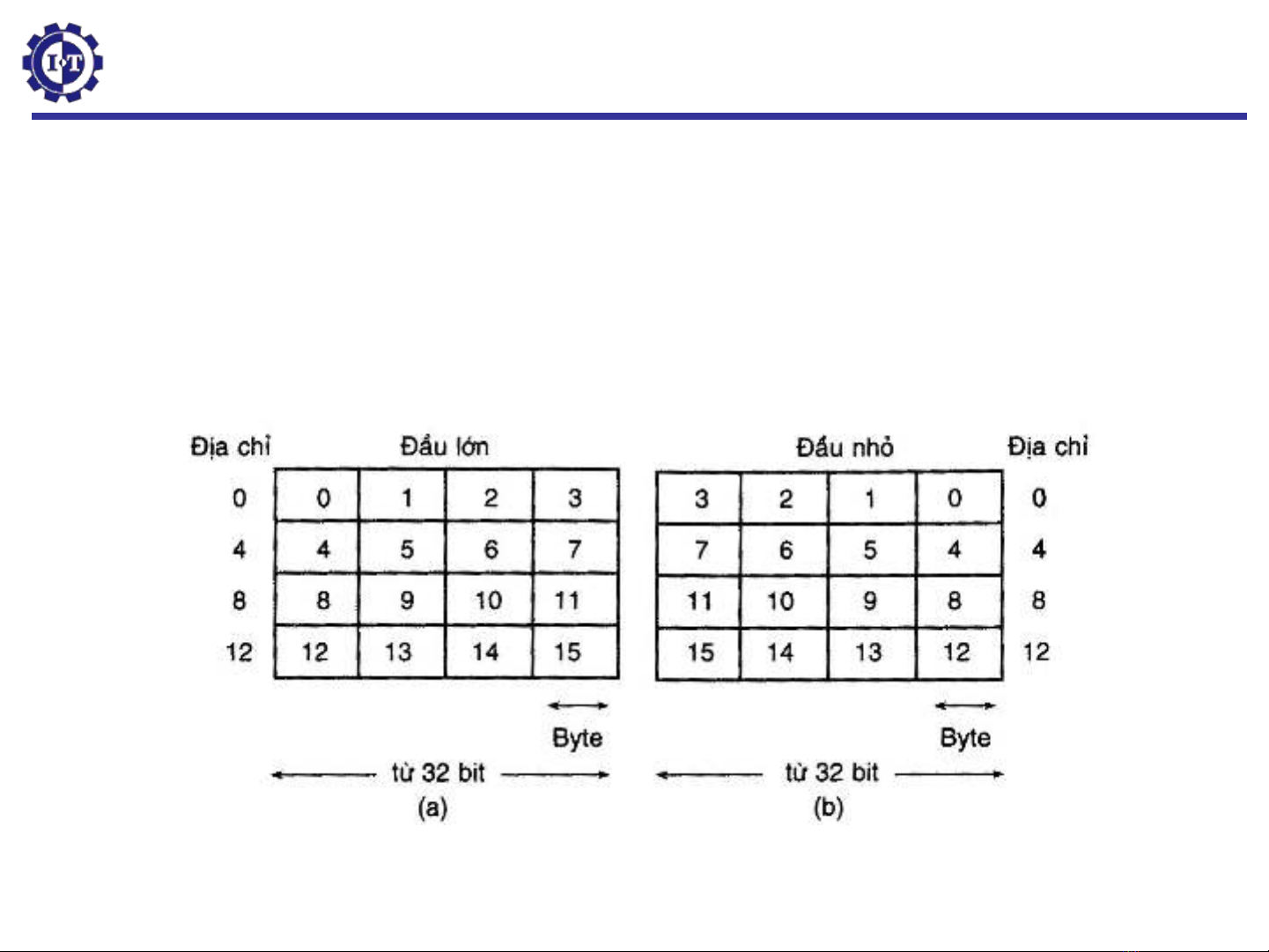

6.2. Đ a ch b nhị ỉ ộ ớ

Các khái ni m:ệ

–Memory, bit, cell, address, byte, word

S p x p th t byteắ ế ứ ự

–Có v n đ gì không trong cách s p x p th t byteấ ề ắ ế ứ ự