Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 1

8 September 2009 1

NKK-HUT

Hệthống máy tính

Chương 5

KIẾN TRÚC MÁY TÍNH TIÊN TIẾN

Nguyễn Kim Khánh

Trường Đại học Bách khoa Hà Nội

8 September 2009 2

NKK-HUT

Nội dung học phần

Chương 1. Giới thiệu chung

Chương 2. Kiến trúc bộnhớ

Chương 3. Kiến trúc vào-ra

Chương 4. Kiến trúc bộxửlý

Chương 5. Kiến trúc máy tính tiên tiến

8 September 2009 Bài giảng Kiến trúc Máy tính 3

NKK-HUT

5.1. Phân loại kiến trúc máy tính

5.2. Máy tính vector và bộxửlý mảng

5.3. Một sốkiến trúc MIMD thông dụng

5.4. Bộxử lý đa lõi

Nội dung

8 September 2009 Bài giảng Kiến trúc Máy tính 4

NKK-HUT

5.1. Phân loại kiến trúc máy tính

Phân loại của Michael Flynn (1966)

SISD - Single Instruction Stream, Single Data Stream

SIMD - Single Instruction Stream, Multiple Data Stream

MISD - Multiple Instruction Stream, Single Data Stream

MIMD - Multiple Instruction Stream, Multiple Data Stream

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 2

8 September 2009 5

NKK-HUT

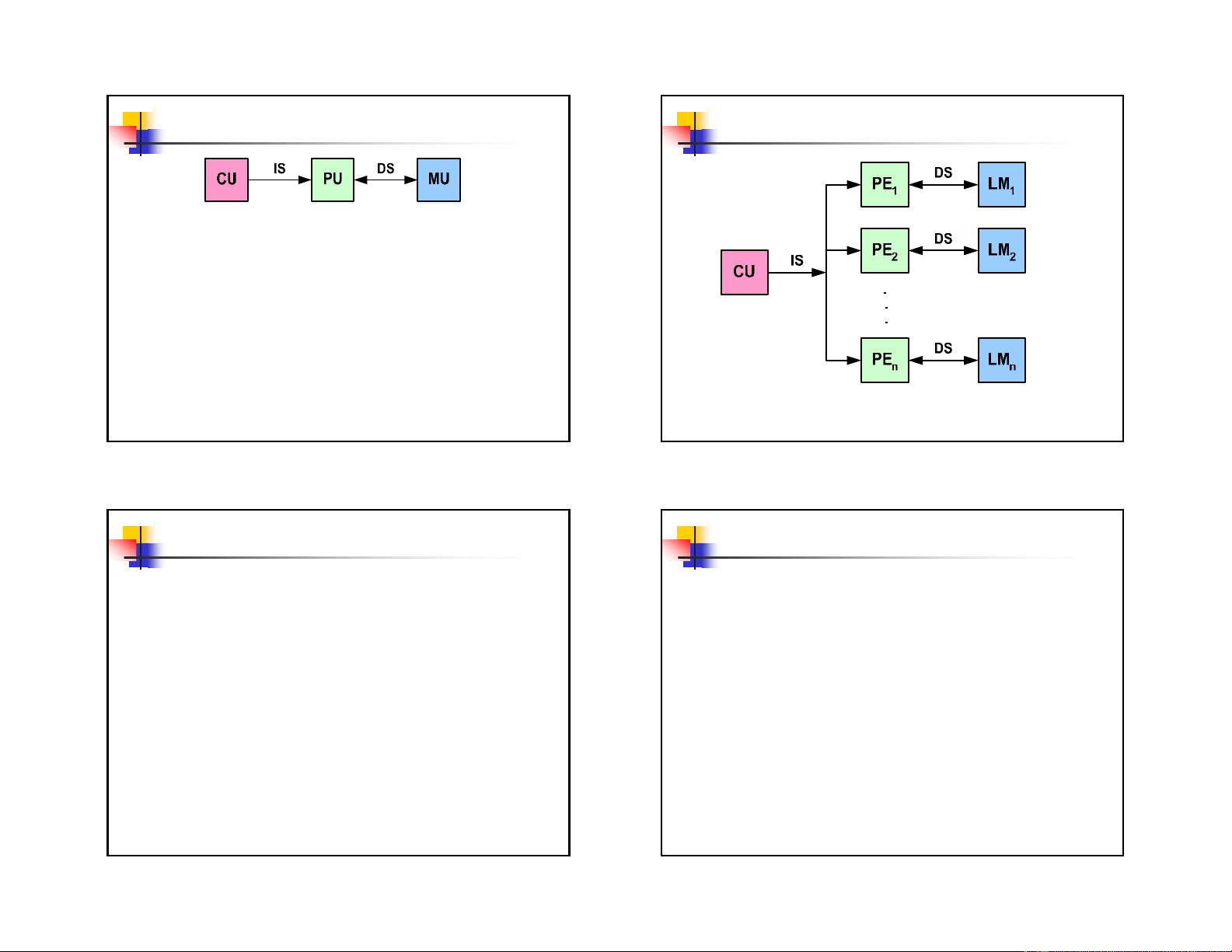

SISD

CU: Control Unit

PU: Processing Unit

MU: Memory Unit

Một bộxửlý

Đơn dòng lệnh

Dữliệu được lưu trữtrong một bộnhớ

Chính là Kiến trúc von Neumann

8 September 2009 6

NKK-HUT

SIMD

8 September 2009 7

NKK-HUT

SIMD (tiếp)

Đơn dòng lệnh điều khiển đồng thời các

phần tửxửlý PE (processing elements)

Mỗi phần tửxửlý có một bộnhớdữliệu

riêng LM (local memory)

Mỗi lệnh được thực hiện trên một tập

các dữliệu khác nhau

Các mô hình SIMD

Vector Computer

Array processor

8 September 2009 8

NKK-HUT

MISD

Một luồng dữliệu cùng được truyền đến

một tập các bộxửlý

Mỗi bộxửlý thực hiện một dãy lệnh

khác nhau.

Chưa tồn tại máy tính thực tế

Có thểcó trong tương lai

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 3

8 September 2009 9

NKK-HUT

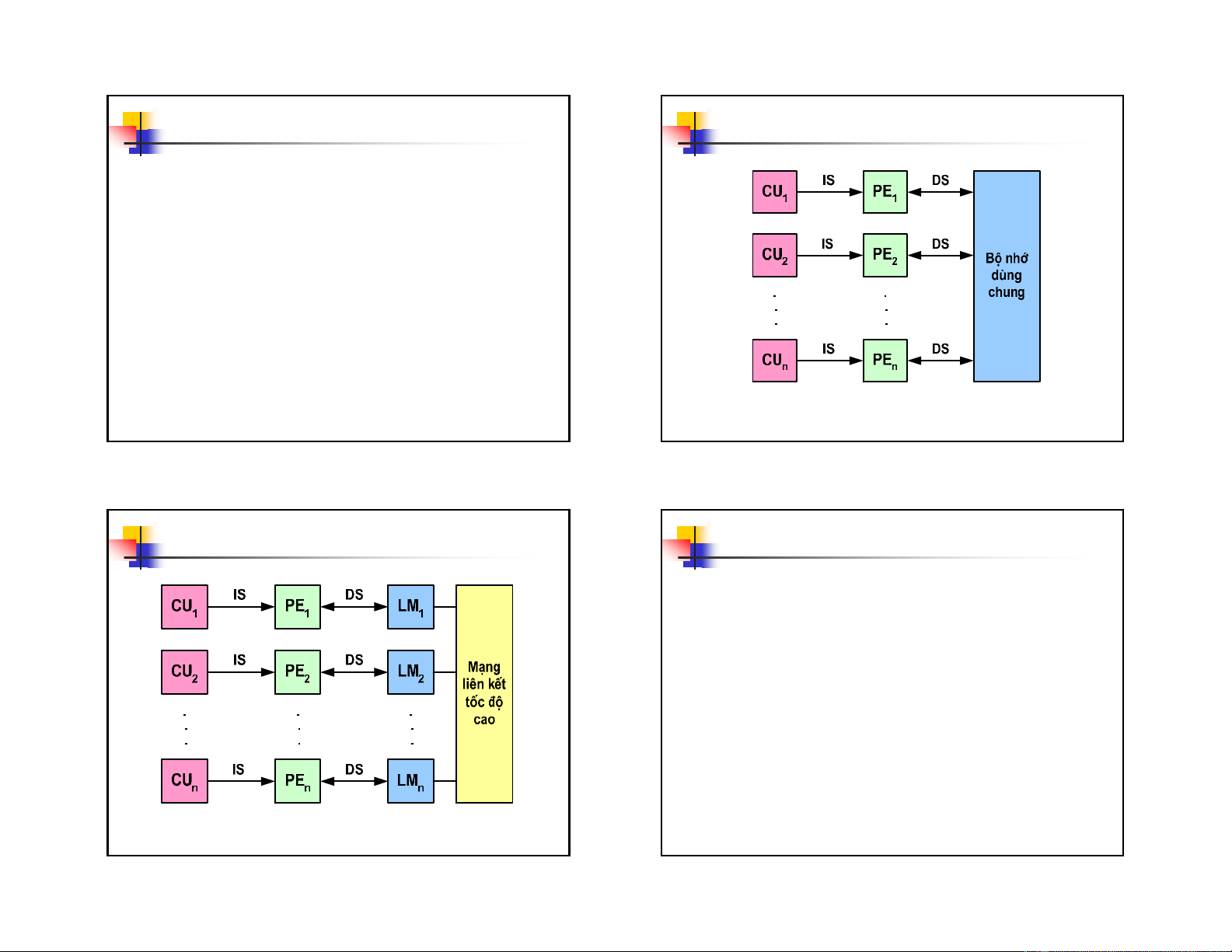

MIMD

Tập các bộxửlý

Các bộxử lý đồng thời thực hiện các

dãy lệnh khác nhau trên các dữliệu

khác nhau

Các mô hình MIMD

Multiprocessors (Shared Memory)

Multicomputers (Distributed Memory)

8 September 2009 10

NKK-HUT

MIMD - Shared Memory

8 September 2009 11

NKK-HUT

MIMD - Distributed Memory

8 September 2009 12

NKK-HUT

5.2. Máy tính vector và bộxửlý mảng

Thuộc loại SIMD

Data parallelism in time = vector processing

Data parallelism in space = array processing

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 4

8 September 2009 13

NKK-HUT

Phép toán trên vector

Bộxửlý tuần tự:

for i = 0 to 63 do

P[i] := W[i] ×D[i]

endfor

Bộxửlý vector:

load W

load D

P := W ×D

store P

for i = 0 to 63 do

X[i+1] := X[i] + Z[i]

Y[i+1] := X[i+1]+Y[i]

endfor

Không xửlý song

song được

8 September 2009 14

NKK-HUT

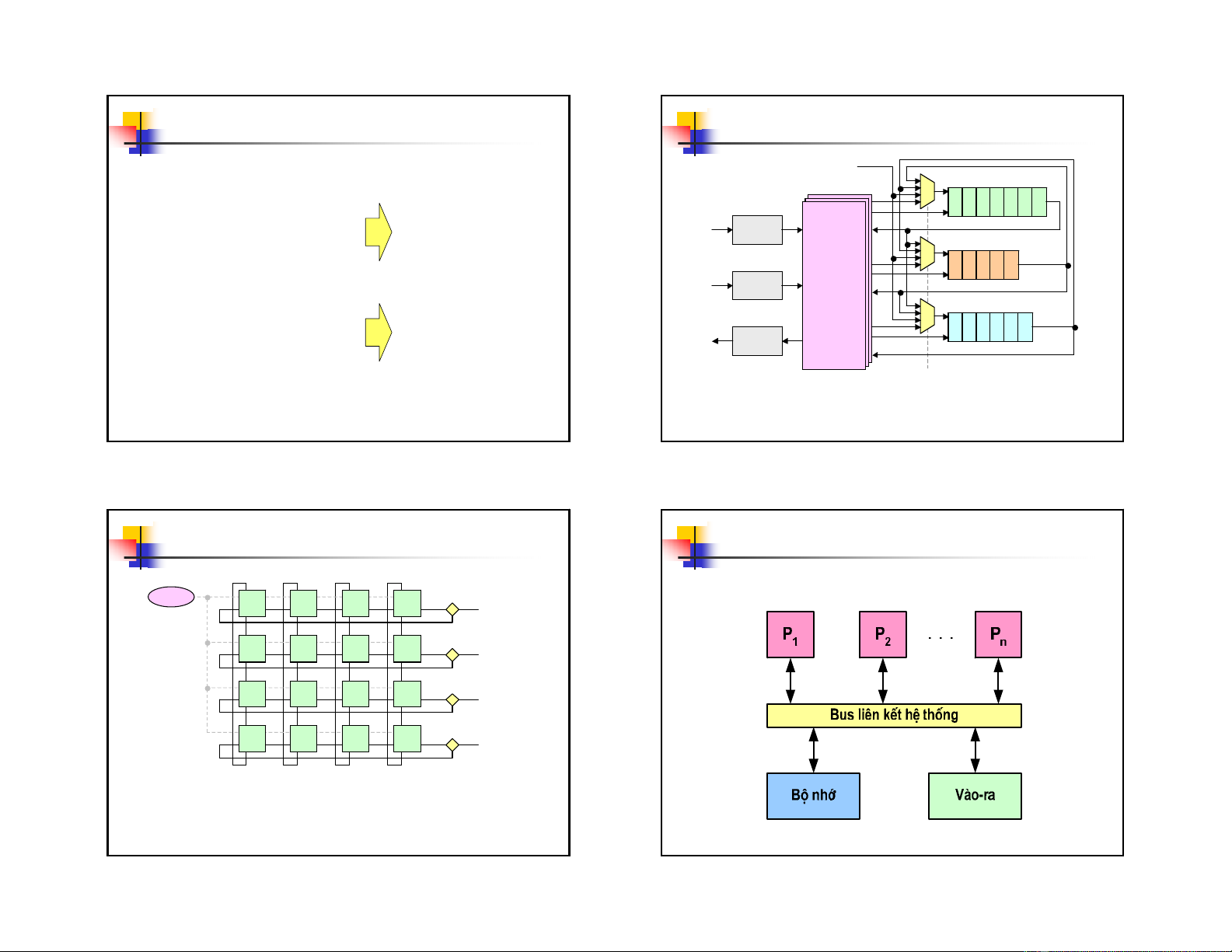

Thực hiện bộxửlý vector

Function unit 1 pipeline

To and from m emory unit

From scalar registers

Vector

register

file

Function unit 2 pipeline

Function unit 3 pipeline

Forwarding muxes

Load

unit A

Load

unit B

Store

unit

8 September 2009 15

NKK-HUT

Ví dụbộxửlý mảng

Control

broadcast Parallel

I/O

Processor array

Control

Switches

8 September 2009 16

NKK-HUT

5.3. Một sốkiến trúc MIMD thông dụng

1.SMP (Symmetric Multiprocessors)

Bài giảng Hệthống máy tính

Nguyễn Kim Khánh - ĐHBKHN 5

8 September 2009 17

NKK-HUT

SMP (tiếp)

Một máy tính có n >= 2 bộxửlý giống nhau

Các bộxửlý dùng chung bộnhớvà hệthống

vào-ra

Thời gian truy cập bộnhớlà bằng nhau với

các bộxửlý

Tất cảcác bộxửlý chia sẻtruy nhập vào-ra

Các bộxửlý có thểthực hiện chức năng

giống nhau

Hệthống được điều khiển bởi một hệ điều

hành phân tán

8 September 2009 18

NKK-HUT

Ưu điểm của SMP

Hiệu năng

Các công việc có thểthực hiện song song

Tính sẵn dùng

Các bộxửlý có thểthực hiện các chức

năng giống nhau, vì vậy lỗi của một bộxử

lý sẽkhông làm dừng hệthống

Khả năng mởrộng

Người sửdụng có thể tăng hiệu năng bằng

cách thêm bộxửlý

8 September 2009 19

NKK-HUT

2. Cluster

Nhiều máy tính được kết nối với nhau

bằng mạng liên kết tốc độ cao (~ Gbps)

Mỗi máy tính có thểlàm việc độc lập

Mỗi máy tính được gọi là một node

Các máy tính có thể được quản lý làm

việc song song theo nhóm (cluster)

Toàn bộhệthống có thể coi như là một

máy tính song song

8 September 2009 20

NKK-HUT

Cluster (tiếp)

Dễdàng xây dựng và mởrộng

Tính sẵn sàng cao

Khả năng chịu lỗi

Giá thành rẻvới hiệu năng cao

![Các thể loại thiết kế đồ họa [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2013/20130718/kimchimm/135x160/4321374142554.jpg)