Nguyễn Anh Đức TĐH-56

Page 1 of 30

Chương 1 : Giới thiệu chung

1.Hệ vi xử lý

1.1 Các loại tín hiệu

-Tín hiệu tương tự (analog) : tín hiệu có giá trị thay đổi liên tục theo thời gian

Đặc điểm : dễ bị nhiễu tác động, thiết bị biến đổi tuyến tính, dễ bị tác động của môi trường làm

ảnh hưởng đến việc sử dụng tín hiệu

-Tín hiệu rời rạc (xung) là tín hiệu được chia ra thành các xung hẹp có biên độ bằng giá trị tín

hiệu tương tự, tương ứng tại thời điểm lấy mẫu

Đặc điểm : Có biên độ không đổi và rời rạc về thời gian, chống nhiễu tốt, xử lí tín hiệu khó, xung

càng hẹp dải phổ càng rộng

Lưu ý : tín hiệu bình thường và tín hiệu rời rạc vẫn giữ nguyên giá trị góc

-Tín hiệu số là tín hiệu rời rạc và biên độ và thời gian

Đặc điểm : được lượng tử hóa, rời rạc hóa thời gian, biểu diễn các mẫu bằng một số số học bằng

chính số mức lượng tử hóa mà mẫu chiếm sau khi làm tròn. Không có thứ nguyên vì là số số học nên

thiết bị xử lí tín hiệu số là thiết bị tính toán, biểu diễn số phụ thuộc các bước lượng tử hóa. Việc lượng

tử hóa làm xuất hiện các hàm bậc 2

Hệ xử lí là hệ tính toán xử lí các tín hiệu số

1.2 Bộ vi xử lí (Micro Proccesor)

-Khái niệm : Là bộ xử lí tín hiệu số làm việc theo chương trình, được chế tạo trên 1 chíp bán dẫn

Lưu ý : tất cả các thông tin bên trong bộ vi xử lí và từ bên ngoài gửi vào bộ vi xử lí đều phải được

biểu diễn dạng số

-Chương trình là một dãy các lệnh liên tiếp, các lệnh được thực hiện một cách tuần tự và liên tục.

Chương trình được người sử dụng xây dựng trước và phải có thiết bị lưu trữ.

1.3 Hệ vi xử lí

-Khái niệm: Là một hệ thống só có hạt nhân là bộ vi xử lí làm việc theo chương trình được lưu

trong bộ nhớ, đưa ra các quyết định, xử lí các tín hiệu hoặc đưa ra các xung điều khiển để các khối

khác từng bước thao tác, liên hệ với bên ngoài thông qua các cửa vào ra

-Bộ vi xử lí : đóng vai trò não bộ của hệ vi xử lí, một mạch điện tử, có mật độ tích hợp cao, quyết

định tính năng của hệ, tên của hệ là tên của chip

Tính năng của hệ được thể hiện qua các đặc tính sau :

+Tốc độ xử lí tín hiệu (số lượng phép tinh cơ bản/giây)

+Khả năng quản lí bộ nhớ

-Bộ nhớ : Thiết bị lưu trữ thông tin (dữ liệu và chương trình), thực hiện chương trình, đưa ra các

quy định dưới dạng kết quả được lưu trong bộ nhớ và thông tin được đưa ra ngoài (tín hiệu điều

khiển)

-Cổng vào, ra là thiết bị trao đổi thông tin với thiết bị ngoại vi. Tại một thời điểm, thông tin chỉ có

thể là vào hoặc ra

-Thiết bị ngoại vi gồm thiết bị vào (biến đổi tín hiệu vào thành tín hiệu số) và thiết bị ra (biến đổi

thông tin từ hệ 2 thành các hệ thích hợp để con người sử dụng được)

Nguyễn Anh Đức TĐH-56

Page 2 of 30

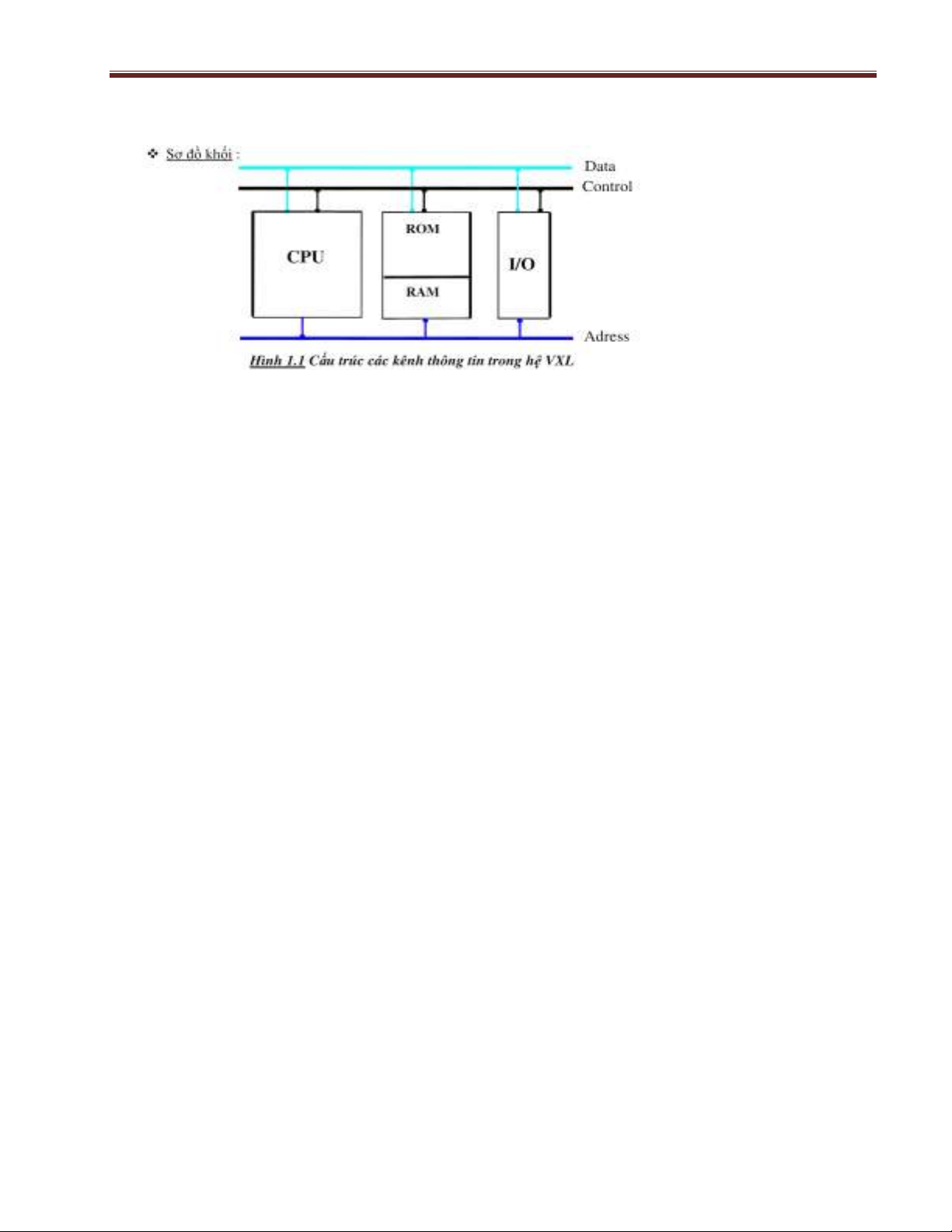

2.Hệ vi xử lí tối thiểu

-Bộ xử lí trung tâm CPU ( Center processing unit): là trung tâm đầu não của hệ, có chức năng thu

thập, xử lí thông tin, điều khiển mọi hoạt động của hệ vi xử lí

-Bộ nhớ trung tâm có nhiệm vụ lưu trữ thông tin dữ liệu

-Thiết bị I/O thực hiện việc nhận dữ liệu từ các kênh thông tin bên ngoài vào để CPU xử lí và

xuất ra các tín hiệu điều khiển hệ thống

-Hệ thống bus là hệ thống để trao đổi thông tin giữa các thành phần trong hệ thống. Để trao đổi

nhanh, mỗi thành phần trong hệ thống phải có 1 địa chỉ xác định, phải có đường truyền tin

*Add bus: để xác định địa chỉ nguồn và đích

*Data bus: trao đổi dữ liệ theo 2 phương pháp tuần tự và song song

*Control bus: truyền các tín hiệu điều khiển việc trao đổi thông tin. Việc trao đổi thông tin diễn ra

chặt chẽ theo 1 trình tự xác định

*Power bus: cung cấp nguồn cho các thành phần trong hệ thống với mức điện áp xác định

Nhận xét: các tín hiệu truyền trên bus dữ liệu truyền theo 2 hướng đến CPU, M, I, O và ngược lại

( hướng truyền tại thời điểm khác nhau, có điều khiển)

Độ rộng của đường truyền tín hiệu tính bằng bit. Chính là số lượng, các đường truyền của bus dữ

liệu. Độ rộng đường truyền càng lớn, tốc độ trao dổi dữ liệu càng nhanh

Các tín hiệu địa chỉ truyền trên add bus theo hướng từ CPU đến các thiết bị ngoại vi.

Các tín hiệu điều khiển truyền trên bus điều khiển thường là tín hiệu riêng lẻ, truyền đi theo cả 2

hướng CPU phát ra tín hiệu hướng về các phân tử, còn các phân tử phát ra các tín hiệu truyền về CPU

để thông báo trạng thái của chúng.

2.1 Các thành phần tạo nên một hệ vi xử lí

Hệ vi xử lí: gồm phần cứng và phần mềm.

-Phần cứng là các thiết bị vật lí cấu tạo nên hệ thống bao gồm các linh kiện, thiết bị điện tử, cơ

khí mà ta có thể cảm nhận và lắp ráp được. Phần cứng của hệ vi xử lí được thiết kế theo yêu cầu

-Phần mềm là toàn bộ các chương trình đã được mã hóa nhị phân và được đặt trong bộ nhớ của hệ

thống. Phần mềm gồm hệ điều hành, chương trình hệ điều hành quản lí các thiết bị, chương trình ứng

dụng chạy trên hệ điều hành, chương trình được viết dưới dang mã máy để biết được cần phải biết

phần cứng, cấu trúc của hệ

Phân loại

MP đa năng: để chế tạo máy tính, các thiết bị viễn thông

MP đơn năng: Vi điều khiển… Các hệ MP đơn năng không có tốc độ xử lí cao, dung lượng bộ

nhớ nhỏ

Sơ đồ phát triển của hệ

vi x

-Theo chiều dọ

c (đa năng): đư

quản lí thông tin…)

-Theo chiề

u ngang (đơn năng

thành họ các sản phầm

Ứng dụ

ng: Máy vi tính cá nh

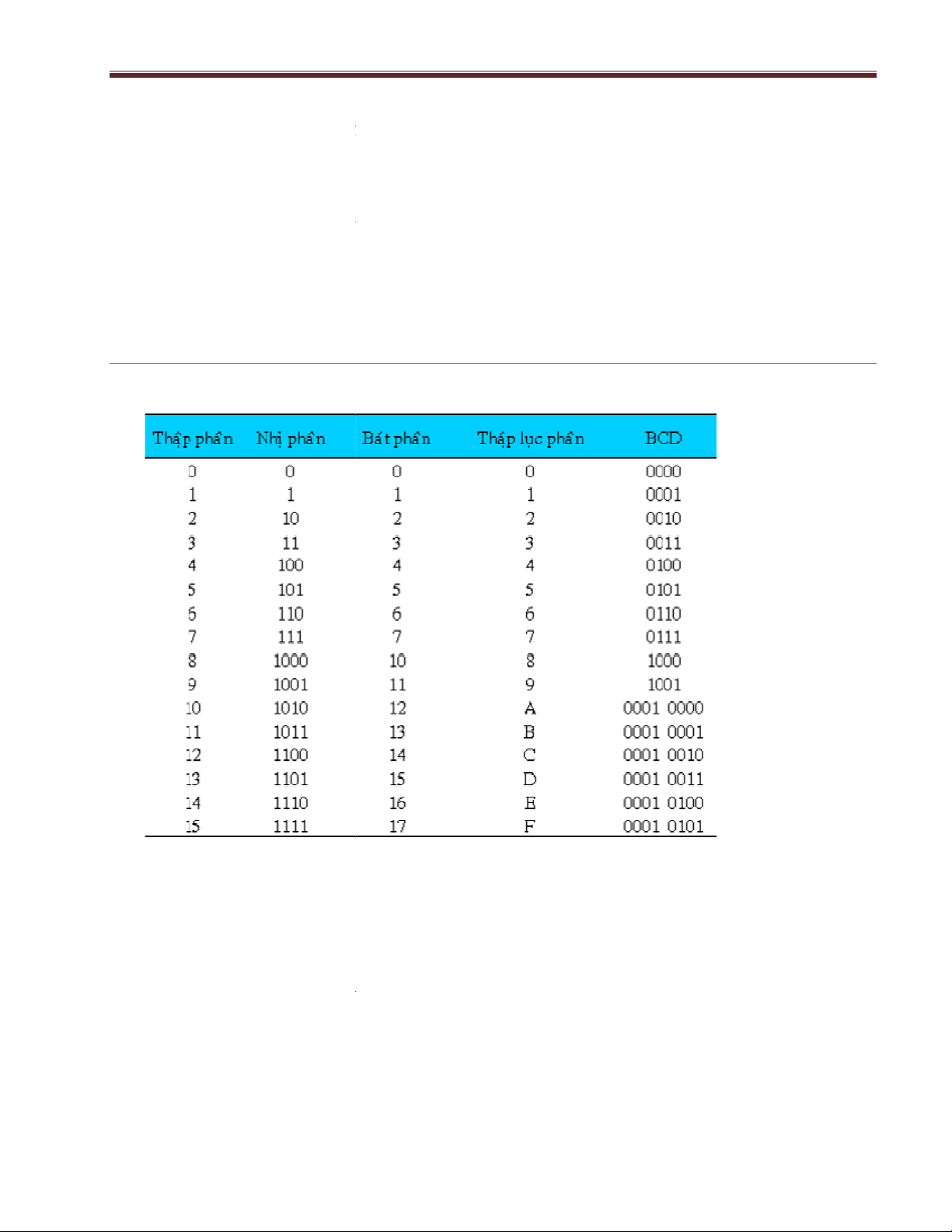

Chương 2 : Hệ đế

m và

1. Hệ đếm

2.Các phần tử logic cơ b

ả

Để thực hiệ

n các phép tính cơ

2.1 Các dạng tín hiệu logic

-Các tín hiệu xung : tuyề

n tín

-Tín hiệu logic thế

: chia làm

Chú ý với cùng mạch phần c

ứ

toán logic khác nhau

Mạch logic gồm mạch rời rạ

c

Nguy

ễ

i x

ử lí

đư

ợc chế tạo với xu hướng ngày càng hoàn thiệ

n

ăng): tích h

ợp các tính năng điều khiể

n, các phiên b

hân (đa năng), các b

ộ điều khiển số (đơn năng)

m và các ph

ần tử cơ bản

ả

n

cơ b

ản (các thiết bị)

tín hi

ệu đi xa

m 2 lo

ại logic âm và logic dương (high =1

; low =0

ứ

ng việc chọn tín hiệu logic thế

dương hay âm s

c và m

ạch tích hợp (các Ic số, Ic logic để thự

c hi

ễ

n Anh Đức TĐH-56

Page 3 of 30

n ( t

ốc độ, khả năng

n b

ản nâng cấp tạo

=0)

s

ẽ thực hiện 2 phép

hi

ện các hàm cơ bản)

Nguyễn Anh Đức TĐH-56

Page 4 of 30

2.2 Các họ Ic logic

-TTL : sử dụng cấu trúc nền tảng từ các transistor (BJT) nên có đầy đủ ưu điểm của một

Transistor (công suất tiêu tán thấp, độ miễn nhiễu cao), điện áp Vdd = 5V.

+74XXX ( Ic dân dụng)

+54XXX (Ic quân sự)

+84XXX (Ic công nghiệp)

XXX là chức năng các Ic

Các series thông dụng bao gồm các dòng sau:

*Tiêu chuẩn (Standard) mang tên 74

*Công suất thấp (Low Power) mang tên 74L

*Công suất cao (High Power) mang tên 74H

*Schottky công suất thấp (Low Power Schottky) mang tên 74LS

*Schottky công suất thấp nâng cấp so LS (Advanced Low Power Schottky) mang tên 74ALS

*Schottky (Advanced Schottky) mang tên 74AS

*Schottky công suất nhanh (Fast Schottky) mang tên 74F

-CMOS: sử dụng cấu trúc nền tảng từ các MOSFET nhưng cũng mang khá nhiều đặc điểm nổi

trội của TTL, ban đầu khi mới ra đời tốc độ của các dòng CMOS chậm hơn các dòng TTL rất nhiều,

nhưng sau này với hàng loạt cải tiến tốc độ của CMOS đã ngang ngửa TTL. Hiện nay, người ta đang

bắt đầu sử dụng dần các dòng CMOS thay cho TTL. Điện áp hoạt động Vdd = 5V - 15V.

Hãng RCA được xem là hãng tiên phong trong việc sản xuất các dòng IC CMOS như các

dòng CD40xxA, CD40xxB, CD45xx, CD47xx (các dòng có chữ B ở cuối có thêm các ưu điểm như

sau: khả năng chịu dòng cao hơn, thời tăng, thời giảm của xung vuông ra ngắn hơn tốc độ cao hơn.).

Ngoài ra, hãng Motorola còn cho ra đời cái dòng IC CMOS của riêng họ như 140xx, 140xxB, 145xx.

-Ghép nối tiếp giữa các họ IC logic

*Ghép trực tiếp

*Ghép qua bộ chuyển đổi mức logic

*Mạch dịch mức tích hợp sẵn

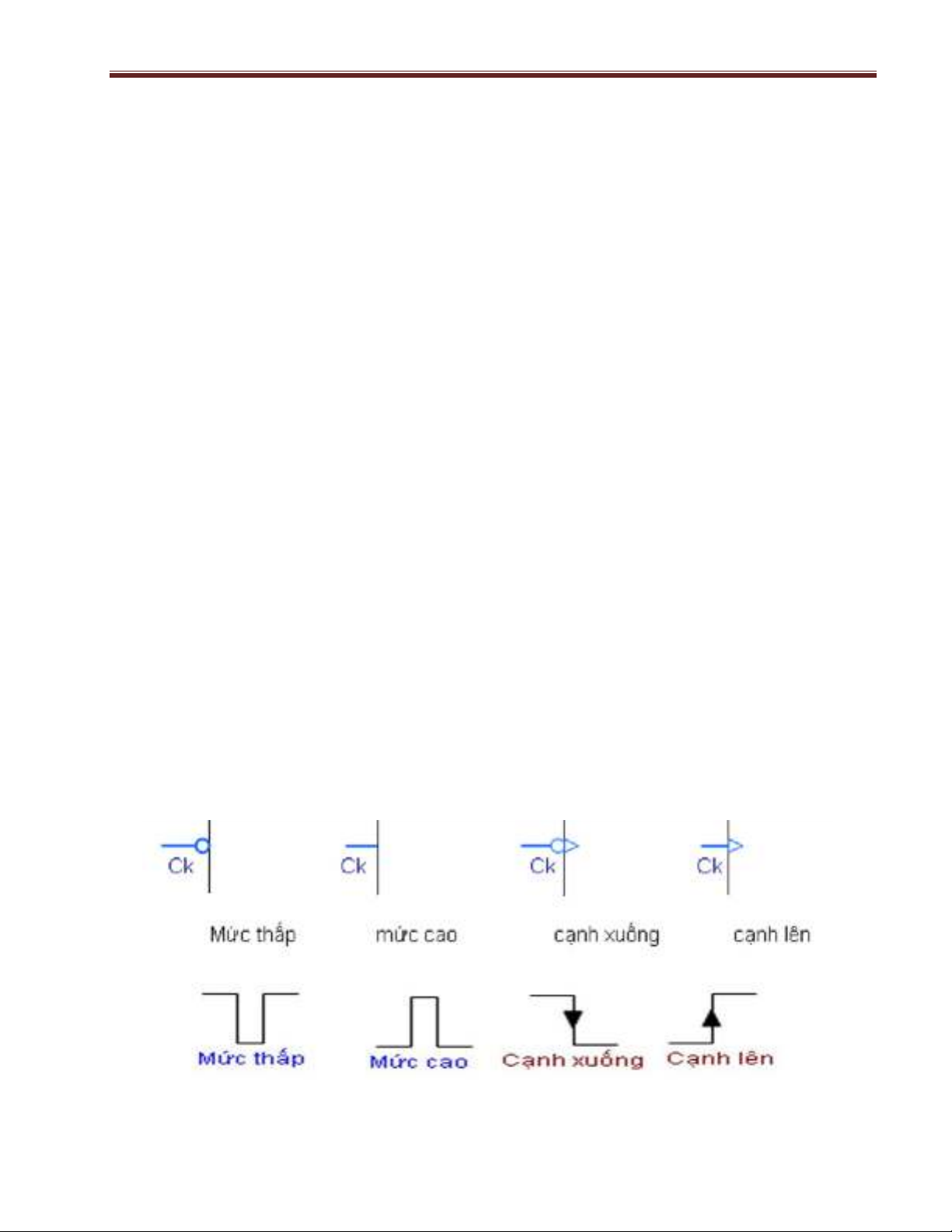

2.3 Các tín hiệu điều khiển mạch logic

-Chức năng: Thiết lập chế độ hoạt động của mạch bằng tín hiệu ngoài, tăng tính mềm dẻo và khả

năng điều khiển

-Các dạng tín hiệu

-Mức logic: Chắc chắn, tin cậy cao, chống nhiễu tốt nhưng tác động chậm

-Sườn tích cực: tác động nhanh nhung độ tin cậy thấp (phụ thuộc trị số mạch vi phân)

![Tài liệu học tập Vi điều khiển ứng dụng trong đo lường và điều khiển [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2021/20210705/lovebychance06/135x160/7771625534375.jpg)

![Tài liệu thực tập cơ sở điều khiển tự động [mới nhất]](https://cdn.tailieu.vn/images/document/thumbnail/2026/20260507/hoahongxanh0906/135x160/26581778488080.jpg)